अनुरूप से अंकीय परिवर्तक: Difference between revisions

m (removed Category:Vigyan Ready using HotCat) |

No edit summary |

||

| (2 intermediate revisions by 2 users not shown) | |||

| Line 364: | Line 364: | ||

{{DEFAULTSORT:Analog-To-Digital Converter}} | {{DEFAULTSORT:Analog-To-Digital Converter}} | ||

] | ] | ||

[[Category:Machine Translated Page]] | |||

[[Category:AC with 0 elements|Analog-To-Digital Converter]] | |||

[[Category:All Wikipedia articles written in American English|Analog-To-Digital Converter]] | |||

[[Category:All articles needing additional references|Analog-To-Digital Converter]] | |||

[[Category:All articles with unsourced statements|Analog-To-Digital Converter]] | |||

[[Category:Articles needing additional references from July 2018|Analog-To-Digital Converter]] | |||

[[Category:Articles needing additional references from July 2022|Analog-To-Digital Converter]] | |||

[[Category:Articles with hatnote templates targeting a nonexistent page|Analog-To-Digital Converter]] | |||

[[Category:Articles with short description|Analog-To-Digital Converter]] | |||

[[Category:Articles with unsourced statements from February 2019|Analog-To-Digital Converter]] | |||

[[Category:CS1 maint]] | |||

[[Category:Missing redirects|Analog-To-Digital Converter]] | |||

[[Category:Pages with script errors]] | |||

[[Category:Short description with empty Wikidata description|Analog-To-Digital Converter]] | |||

[[Category:Template documentation pages|Documentation/doc]] | |||

[[Category:Templates used by AutoWikiBrowser|Cite web]] | |||

[[Category:Templates using TemplateData]] | |||

[[Category:Use American English from January 2020|Analog-To-Digital Converter]] | |||

[[Category:Use mdy dates from September 2021|Analog-To-Digital Converter]] | |||

[[Category:Webarchive template wayback links|Analog-To-Digital Converter]] | |||

Latest revision as of 14:30, 23 September 2022

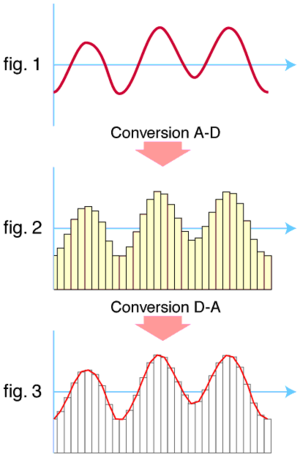

इलेक्ट्रॉनिक्स में, अनुरुप से अंकीय परिवर्तक (ADC, A/D, or A-to-D) एक ऐसी प्रणाली है जो एक अनुरूप संकेत ( एनालॉग सिग्नल ) को परिवर्तित करती है, जैसे किसी माइक्रोफ़ोन द्वारा चयन की गई ध्वनि या डिजिटल कैमरा में डिजिटल सिग्नल के रूप में प्रवेश करने वाला प्रकाश। एक अनुरुप से अंकीय परिवर्तक एक पृथक माप भी प्रदान कर सकता है, जैसे कि एक इलेक्ट्रॉनिक उपकरण जो एक अनुरूप निविष्ट वोल्टता ( एनालॉग इनपुट वोल्टेज ) या करंट को एक डिजिटल संख्या में परिवर्तित करता है जो वोल्टेज या करंट के परिमाण का प्रतिनिधित्व करता है। सामान्यत: डिजिटल आउटपुट एक द्वि-पूरक बाइनरी नंबर है, जो इनपुट के समानुपाती होता है, लेकिन अन्य संभावनाएं भी होती हैं।

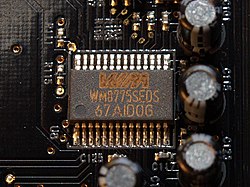

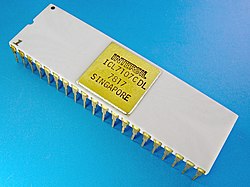

कई अनुरुप से अंकीय परिवर्तक (ADC) स्थापत्य ( आर्किटेक्चर ) हैं। जटिल और सटीक रूप से मिलान किए गए घटकों की आवश्यकता के कारण, सभी लेकिन सबसे विशिष्ट ADCs को एकीकृत सर्किट (ICs) के रूप में कार्यान्वित किया जाता है। ये सामान्यत: धातु-ऑक्साइड-अर्धचालक (MOS) मिश्रित-सिग्नल एकीकृत सर्किट चिप्स का रूप लेते हैं, जो एनालॉग और डिजिटल सर्किट दोनों को एकीकृत करते हैं।

एक अंकीय अनुरूप परिवर्तक ( डिजिटल-टू-एनालॉग कनवर्टर) विपरीत फ़ंक्शन करता है, यह एक डिजिटल सिग्नल को एक अनुरूप संकेत में परिवर्तित करता है।

व्याख्या

अनुरुप से अंकीय परिवर्तक (ADC), एक निरंतर-समय और निरंतर-आयाम अनुरूप संकेत को असतत-समय और असतत आयाम अनुरूप संकेत में परिवर्तित करता है। रूपांतरण में इनपुट का परिमाणीकरण शामिल है, इसलिए यह आवश्यक रूप से अल्प मात्रा में त्रुटि या शोर का परिचय देता है। इसके अतिरिक्त, लगातार रूपांतरण करने के स्थान पर एक अनुरुप से अंकीय परिवर्तक (ADC) समय-समय पर रूपांतरण करता है, इनपुट का नमूना लेता है व इनपुट सिग्नल की स्वीकार्य बैंड चौड़ाई को सीमित करता है।

अनुरुप से अंकीय परिवर्तक (ADC) का प्रदर्शन मुख्य रूप से इसकी बैंड चौड़ाई और सिग्नल-टू-शोर अनुपात (SNR) की विशेषता है। एक अनुरुप से अंकीय परिवर्तक की बैंड चौड़ाई की विशेषता मुख्य रूप से इसकी नमूना दर है। ADC का SNR कई कारकों से प्रभावित होता है, जिसमें विभेदन (रिज़ॉल्यूशन), रैखिकता और सटीकता (कितनी अच्छी तरह से परिमाणीकरण स्तर सही अनुरूप संकेत से मेल खाता है), उपघटन ( अलियासिंग ) और तनाव शामिल है। एक ADC के SNR को प्राय: बिट्स (bits) की प्रभावी संख्या {ENOB} के संदर्भ में संक्षेपित किया जाता है, प्रत्येक माप के बिट्स (bits) की संख्या जो औसत पर शोर नहीं होती है। एक आदर्श अनुरुप से अंकीय परिवर्तक के पास इसके विभेदन (रिज़ॉल्यूशन) के बराबर एक ENOB होता है। ADCs को बैंड चौड़ाई से मेल खाने के लिए चुना जाता है और सिग्नल के आवश्यक SNR को डिजीटल किया जाता है। यदि कोई ADC सिग्नल के बैंड चौड़ाई से दोगुना से अधिक नमूना दर पर संचालित होता है, तो न्यक्विस्ट-शैनन नमूनाकरण (सैम्पलिंग) प्रमेय के अनुसार, सही पुनर्निर्माण संभव है। परिमाणीकरण त्रुटि की उपस्थिति एक आदर्श ADC के SNR को भी सीमित कर देती है। हालांकि, यदि ADC का SNR इनपुट सिग्नल से अधिक है, तो इसके प्रभावों को उपेक्षित किया जा सकता है, जिसके परिणामस्वरूप अनुरूप ( एनालॉग ) इनपुट सिग्नल का अनिवार्य रूप से सही डिजिटल निरूपण होता है।

विभेदन (रिज़ॉल्यूशन)

परिवर्तक ( कनवर्टर ) का विभेदन (रिज़ॉल्यूशन) अलग-अलग, अर्थात् असतत मानों की संख्या को इंगित करता है, जो अनुरूप ( एनालॉग ) इनपुट मानों की अनुमत सीमा से अधिक उत्पन्न कर सकते हैं। इस प्रकार एक विशेष विभेदन परिमाणीकरण त्रुटि के परिमाण को निर्धारित करता है और इसलिए अधिप्रतिचयन ( ओवरसैम्पलिंग ) के उपयोग के बिना एक आदर्श अनुरुप से अंकीय परिवर्तक के लिए अधिकतम संभावित सिग्नल-टू-शोर (SNR) अनुपात निर्धारित करता है। इनपुट नमूनों को सामान्यत: अनुरुप से अंकीय परिवर्तक के भीतर बाइनरी रूप में इलेक्ट्रॉनिक रूप से संग्रहीत किया जाता है, इसलिए विभेदन (रिज़ॉल्यूशन) को आमतौर पर ऑडियो बिट गहनता के रूप में व्यक्त किया जाता है। परिणाम में, उपलब्ध असतत मानों की संख्या प्राय: दो की शक्ति होती है। उदाहरण के लिए, 8 बिट्स के रिज़ॉल्यूशन वाला एक ADC एक एनालॉग इनपुट को 256 विभिन्न स्तरों (28 = 256) में से एक में एन्कोड कर सकता है। मान 0 से 255 ( अर्थात् अचिहिनत पूर्णांक के रूप में ) या −128 से 127 ( अर्थात् चिहिनत पूर्णांक के रूप में ) तक की सीमाओं का प्रतिनिधित्व कर सकते हैं, जो अनुप्रयोग पर निर्भर करता है।

विभेदन (रिज़ॉल्यूशन) को विद्युत रूप से भी परिभाषित किया जा सकता है और वोल्ट में व्यक्त किया जा सकता है। आउटपुट कोड स्तर में परिवर्तन की गारंटी के लिए आवश्यक वोल्टेज में परिवर्तन को कम से कम महत्वपूर्ण बिट (LSB) वोल्टेज कहा जाता है। अनुरुप से अंकीय परिवर्तक (ADC) का विभेदन Q LSB वोल्टेज के बराबर है। अनुरुप से अंकीय परिवर्तक का वोल्टता वियोजन ( रिज़ॉल्यूशन), अंतराल की संख्या से विभाजित इसकी समग्र वोल्टेज माप सीमा के बराबर होता है;

जहाँ M बिट्स में ADC का रिज़ॉल्यूशन है और EFSR फुल स्केल वोल्टेज रेंज ( जिसे 'स्पैन' भी कहा जाता है ) है। EFSR द्वारा दिया जाता है

जहां VRefHi और VRefLow कोडित किए जा सकने वाले वोल्टेज के क्रमशः ऊपरी और निचले छोर हैं।

प्राय:, वोल्टेज अंतराल की संख्या निम्न के द्वारा दी जाती है

जहां M बिट्स में ADC's का विभेदन (रिज़ॉल्यूशन) है।[1]

अर्थात्, दो क्रमागत कोड स्तरों के बीच एक वोल्टेज अंतराल नियत किया जाता है।

उदाहरण:

- चित्र 1 में कोडिंग योजना

- पूर्ण पैमाने पर माप सीमा = 0 से 1 वोल्ट

- ADC रिज़ॉल्यूशन 3 बिट है: 23 = 8 परिमाणीकरण स्तर (कोड)

- ADC वोल्टेज रिज़ॉल्यूशन, Q = 1 V / 8 = 0.125 V।

कई मामलों में, एक कनवर्टर का उपयोगी विभेदन (रिज़ॉल्यूशन) सिग्नल-टू-शोर अनुपात (SNR) और एक ENOB के रूप में व्यक्त समग्र प्रणाली में अन्य त्रुटियों द्वारा सीमित है।

परिमाणीकरण त्रुटि

परिमाणीकरण त्रुटि एक आदर्श अनुरुप से अंकीय परिवर्तक में निहित परिमाणीकरण द्वारा प्रवेशित की जाती है। यह अनुरुप से अंकीय परिवर्तक के लिए अनुरूप निविष्ट वोल्टता ( एनालॉग इनपुट वोल्टेज ) और आउटपुट डिजीटल मान के बीच एक गोल (राउंडिंग) त्रुटि है। त्रुटि अरेखीय और संकेत-निर्भर है। एक आदर्श अनुरुप से अंकीय परिवर्तक में, जहां परिमाणीकरण त्रुटि को समान रूप से-1/2 LSB और +1/2 LSB के बीच वितरित किया जाता है, और सिग्नल में सभी परिमाणीकरण स्तरों को कवर करने वाला एक समान वितरण होता है, सिग्नल-टू-क्वेंटाइजेशन-शोर अनुपात (SQNR) है वारा दिया जाता है

जहां Q परिमाणीकरण बिट्स की संख्या है। उदाहरण के लिए, 16-बिट ADC के लिए, परिमाणीकरण त्रुटि अधिकतम स्तर से 96.3 db नीचे है।

परिमाणीकरण त्रुटि DC से निक्विस्ट आवृत्ति तक वितरित की जाती है। नतीजतन, यदि ADC's के बैंड चौड़ाई के हिस्से का उपयोग नहीं किया जाता है, जैसा कि ओवरसैम्प्लिंग के मामले में होता है, तो कुछ परिमाणीकरण त्रुटि आउट-ऑफ-बैंड हो जाएगी, प्रभावी रूप से उपयोग में बैंड चौड़ाई के लिए SQNR में सुधार होगा। एक अधिप्रतिचयन ( ओवरसैम्पलिंग ) प्रणाली में, शोर को आकार देने का उपयोग SQNR को और बढ़ाने के लिए किया जा सकता है, जिससे बैंड से अधिक परिमाणीकरण त्रुटि हो सकती है।

स्पंदित होना ( डिथर )

ADCs में, निष्पादन को आमतौर पर डिथर का उपयोग करके सुधारा जा सकता है। यह बहुत कम मात्रा में अनियमित शोर (जैसे सफेद शोर) है, जिसे रूपांतरण से पहले इनपुट में जोड़ा जाता है। इसका प्रभाव सिग्नल के आधार पर LSB की स्थिति को अनियमित करना है। सिग्नल केवल निम्न स्तरों पर पूरी तरह से कट जाने के बावजूद भी, यह शोर में सामान्य वृद्धि की व्यय पर ADC को परिवर्तित कर सकने वाले संकेतों की प्रभावी सीमा का विस्तार करता है। ध्यान दें कि स्पंदन (डिथर) केवल एक नमूना के विभेदन (रिज़ॉल्यूशन) को बढ़ा सकता है। यह रैखिकता में सुधार नहीं कर सकता है और इस प्रकार सटीकता में सुधार जरूरी नहीं है।

अनुरुप से अंकीय परिवर्तक (ADC) की बिट गहनता के संबंध में बहुत निम्न स्तर के एक ऑडियो सिग्नल में परिमाणीकरण विरूपण सिग्नल के साथ सहसंबद्ध है और यह विकृत और अप्रिय लगता है। डीथरिंग के साथ, विरूपण शोर में बदल जाता है। समय के साथ औसत से विकृत संकेत को सटीक रूप से पुनर्प्राप्त किया जा सकता है। बिजली मीटर जैसे सिस्टम को एकीकृत करने में भी डिथरिंग का उपयोग किया जाता है। चूंकि मानों को एक साथ जोड़ा जाता है, तो डिथरिंग ऐसे परिणाम उत्पन्न करता है जो अनुरुप से अंकीय परिवर्तक के LSB से अधिक सटीक होते हैं।

फोटोग्राफिक छवियों को प्रति पिक्सेल बिट्स की कम संख्या में परिमाणित करते समय अक्सर लागू किया जाता है- इमेज शोर हो जाती है, लेकिन आंख के लिए मात्राबद्ध छवि ( इमेज ) की तुलना में कहीं अधिक यथार्थवादी लगती है, जो अन्यथा बैंडेड हो जाती है। यह अनुरूप प्रक्रिया डिजिटल में परिवर्तित होने वाले अनुरूप ऑडियो सिग्नल पर डिथर के प्रभाव की कल्पना करने में मदद कर सकती है।

सटीकता

एक अनुरुप से अंकीय परिवर्तक में त्रुटियों के कई स्रोत हैं। परिमाणीकरण त्रुटि और (यह मानते हुए कि अनुरुप से अंकीय परिवर्तक (ADC) का उद्देश्य रैखिक होना है) गैर-रैखिकता किसी भी अनुरुप से अंकीय परिवर्तक रूपांतरण के लिए आंतरिक हैं। इन त्रुटियों को कम से कम महत्वपूर्ण बिट (LSB) नामक इकाई में मापा जाता है। आठ-बिट ADC के उपरोक्त उदाहरण में, एक LSB की एक त्रुटि पूर्ण सिग्नल रेंज का 1/256 या लगभग 0.4% है।

अरैखिकता

सभी ADCs उनकी भौतिक खामियों के कारण होने वाली गैर -त्रुटियों की त्रुटियों से ग्रस्त हैं, जिससे उनका आउटपुट उनके इनपुट के एक रैखिक फ़ंक्शन (या जानबूझकर गैर-रेखीय ADC के मामले में कुछ अन्य फ़ंक्शन) से भ्रमित हो जाता है। इन त्रुटियों को कभी-कभी अंशांकन द्वारा कम किया जा सकता है या परीक्षण द्वारा रोका जा सकता है। रैखिकता के लिए महत्वपूर्ण मानक अभिन्न अरैखिकता और डिफरेंशियल अरैखिकता हैं। ये अरैखिकता विकृति का परिचय देते हैं जो अनुरुप से अंकीय परिवर्तक (ADC) के सिग्नल-टू-शोर अनुपात प्रदर्शन को कम कर सकते हैं और इस प्रकार इसके प्रभावी विभेदन (रिज़ॉल्यूशन) को कम कर सकते हैं।

तनाव ( जिटर )

जब एक साइन तरंग को अंकीकरण ( डिजिटाइज़ ) करते समय , एएक गैर-आदर्श नमूना घड़ी के उपयोग के परिणामस्वरूप नमूने दर्ज किए जाने में कुछ अनिश्चितता होगी। बशर्ते कि क्लॉक जिटर के कारण वास्तविक नमूना समय अनिश्चितता है, इस घटना के कारण होने वाली त्रुटि के रूप में लगाया जा सकता है। इससे अतिरिक्त रिकॉर्ड किए गए शोर का परिणाम होगा जो अकेले परिमाणीकरण त्रुटि द्वारा भविष्यवाणी की गई बिट्स (ENOB) की प्रभावी संख्या को कम कर देगा। DC के लिए त्रुटि शून्य है, कम आवृत्तियों पर छोटा है, लेकिन उच्च आयाम और उच्च आवृत्ति के संकेतों के साथ महत्वपूर्ण है। प्रदर्शन पर तनाव ( जिटर ) के प्रभाव की तुलना परिमाणीकरण त्रुटि से की जा सकती है: , जहां Q एडीसी बिट्स की संख्या है।[citation needed]

| निर्गम माप (bits) |

संकेतक आवृत्ति | ||||||

|---|---|---|---|---|---|---|---|

| 1 Hz | 1 kHz | 10 kHz | 1 MHz | 10 MHz | 100 MHz | 1 GHz | |

| 8 | 1,243 µs | 1.24 µs | 124 ns | 1.24 ns | 124 ps | 12.4 ps | 1.24 ps |

| 10 | 311 µs | 311 ns | 31.1 ns | 311 ps | 31.1 ps | 3.11 ps | 0.31 ps |

| 12 | 77.7 µs | 77.7 ns | 7.77 ns | 77.7 ps | 7.77 ps | 0.78 ps | 0.08 ps ("77.7fs") |

| 14 | 19.4 µs | 19.4 ns | 1.94 ns | 19.4 ps | 1.94 ps | 0.19 ps | 0.02 ps ("19.4fs") |

| 16 | 4.86 µs | 4.86 ns | 486 ps | 4.86 ps | 0.49 ps | 0.05 ps ("48.5 fs") | – |

| 18 | 1.21 µs | 1.21 ns | 121 ps | 1.21 ps | 0.12 ps | – | – |

| 20 | 304 ns | 304 ps | 30.4 ps | 0.30 ps ("303.56 fs") | 0.03 ps ("30.3 fs") | – | – |

| 24 | 18.9 ns | 18.9 ps | 1.89 ps | 0.019 ps ("18.9 fs") | - | – | – |

घड़ी तनाव ( जिटर ) चरण शोर का कारण होता है।[3][4] 1 मेगाहर्ट्ज और 1 गीगाहर्ट्ज के बीच डिजिटलीकरण बैंड चौड़ाई वाले ADCs का विभेदन जिटर द्वारा सीमित है।[5] कम बैंड चौड़ाई रूपांतरणों के लिए जैसे कि 44.1 kHz पर ऑडियो सिग्नल का नमूना लेते समय, क्लॉक जिटर का प्रदर्शन पर कम महत्वपूर्ण प्रभाव पड़ता है।[6]

नमूना दर

एक अनुरूप संकेत समय में निरंतर होता है और इसे डिजिटल मानों के प्रवाह में बदलना आवश्यक है। इसलिए उस दर को परिभाषित करना आवश्यक है जिस पर नए डिजिटल मूल्यों का अनुरूप संकेत से नमूना लिया जाता है। नए मानों की दर को कनवर्टर की नमूनाकरण दर या नमूना आवृत्ति कहा जाता है। लगातार अलग-अलग बैंडलिमिटेड सिग्नल का नमूना लिया जा सकता है और फिर मूल सिग्नल को पुनर्निर्माण फ़िल्टर द्वारा असतत-समय मानों से पुनरुत्पादन किया जा सकता है। न्यक्विस्ट-शैनन नमूना प्रमेय का तात्पर्य है कि मूल संकेत का एक विश्वसनीय पुनरुत्पादन केवल तभी संभव है जब नमूना दर सिग्नल की उच्चतम आवृत्ति के दोगुना से अधिक हो।

चूंकि एक व्यावहारिक अनुरुप से अंकीय परिवर्तक (ADC) तात्कालिक रूपांतरण नहीं कर सकता है, इसलिए इनपुट मूल्य को आवश्यक रूप से उस समय के दौरान स्थिर रखा जाना चाहिए जब कनवर्टर एक रूपांतरण (जिसे रूपांतरण समय कहा जाता है) करता है। एक इनपुट सर्किट जिसे सैंपल एंड होल्ड कहा जाता है, यह कार्य करता है - ज्यादातर मामलों में इनपुट पर अनुरुप ( एनालॉग ) वोल्टेज को संग्रहीत करने के लिए एक संधारित्र का उपयोग करके और इनपुट से संधारित्र को डिस्कनेक्ट करने के लिए एक इलेक्ट्रॉनिक स्विच या गेट का उपयोग करके। कई अनुरुप से अंकीय परिवर्तक एकीकृत सर्किट में नमूना और आंतरिक रूप से उपतंत्र ( सबसिस्टम ) होल्ड शामिल हैं।

उपघटन ( अलियासिंग )

एक अनुरुप से अंकीय परिवर्तक समय में असतत अंतराल पर इनपुट के मूल्य का नमूना लेकर कार्य करता है। बशर्ते कि इनपुट का निक्विस्ट दर से ऊपर का नमूना लिया गया हो। जिसे ब्याज की उच्चतम आवृत्ति के दोगुने के रूप में परिभाषित किया गया हो, तो सिग्नल में सभी आवृत्तियों का पुनर्निर्माण किया जा सकता है। यदि निक्विस्ट दर आधी से अधिक आवृत्तियों का नमूना लिया जाता है, तो उन्हें गलत तरीके से कम आवृत्तियों के रूप में पहचाना जाता है, इस प्रक्रिया को उपघटन के रूप में संदर्भित किया जाता है। उपघटन इसलिए होता है क्योंकि दो या उससे कम बार प्रति चक्र किसी फ़ंक्शन का तुरंत नमूना लेने से चक्र छूट जाता है और इसलिए गलत तरीके से कम आवृत्ति की उपस्थिति होती है। उदाहरण के लिए,1.5 kHz पर नमूना की जा रही 2 kHz साइन वेव को 500 Hz साइन वेव के रूप में पुनर्निर्माण किया जाएगा।

उपघटन से बचने के लिए, अनुरुप से अंकीय परिवर्तक (ADC) के लिए इनपुट को कम-पास फ़िल्टर किया जाना चाहिए ताकि आधा नमूना दर से ऊपर की आवृत्तियों को हटाया जा सके। इस फ़िल्टर को एक एंटी-अलियासिंग फ़िल्टर कहा जाता है और एक व्यावहारिक ADC प्रणाली के लिए आवश्यक है जो उच्च आवृत्ति सामग्री के साथ अनुरूप संकेत पर लागू होता है। उन अनुप्रयोगों में जहां उपघटन के प्रतिकूल सुरक्षा आवश्यक है, अधिप्रतिचयन ( ओवरसैम्पलिंग ) का उपयोग इसे कम करने या इसे खत्म करने के लिए किया जा सकता है।

यद्यपि अधिकांश प्रणालियों में उपघटन अवांछित है, इसका उपयोग बैंड-सीमित उच्च-आवृत्ति सिग्नल (अंडरसैंपलिंग और फ़्रीक्वेंसी मिक्सर देखें) के साथ-साथ डाउन-मिक्सिंग प्रदान करने के लिए किया जा सकता है। उपघटन प्रभावी रूप से सिग्नल आवृत्ति और नमूना आवृत्ति के निचले संकरण यंत्र ( हेटेरोडाइन ) है।[7]

अधिप्रतिचयन ( ओवरसैम्पलिंग )

अर्थव्यवस्था के लिए, संकेतों को अक्सर इस परिणाम के साथ आवश्यक न्यूनतम दर पर नमूने लिये जाते है कि पेश की गई परिमाणीकरण त्रुटि कनवर्टर के पूरे पासबैंड पर फैली शुद्ध शोर है। यदि एक सिग्नल को नाइक्विस्ट दर की तुलना में बहुत अधिक दर पर नमूना लिया जाता है और फिर डिजिटल रूप से इसे सिग्नल बैंड चौड़ाई तक सीमित करने के लिए फ़िल्टर किया जाता है, तो निम्नलिखित लाभ उत्पन्न होते हैं:

- अधिप्रतिचयन ( ओवरसैम्पलिंग ) एनालॉग एंटी-अलियासिंग फिल्टर को महसूस करना आसान बना सकता है।

- उन्नत ऑडियो बिट गहनता

- कम शोर, खासकर जब शोर को आकार देने के लिए नियोजित किया जाता है।

ओवरसैंपलिंग का उपयोग आम तौर पर ऑडियो आवृत्ति ADCs में किया जाता है जहां आवश्यक नमूना दर (आमतौर पर 44.1 या 48 किलोहर्ट्ज़) विशिष्ट ट्रांजिस्टर सर्किट (> 1 मेगाहर्ट्ज) की घड़ी की गति की तुलना में बहुत कम होती है। इस स्थिति में, अनुरुप से अंकीय परिवर्तक (ADC) के प्रदर्शन को बहुत कम या बिना लागत में बहुत बढ़ाया जा सकता है। इसके अलावा, जैसा कि कोई भी अलियास सिग्नल आमतौर पर बैंड से बाहर होता हैं, उपघटन ( अलियासिंग ) को प्राय: बहुत कम लागत वाले फिल्टर का उपयोग करके पूरी तरह से समाप्त किया जा सकता है।

सापेक्ष गति और परिशुद्धता

अनुरुप से अंकीय परिवर्तक (ADC) की गति प्रकार के अनुसार भिन्न होती है। विल्किंसन ADC घड़ी की दर से सीमित है जो वर्तमान डिजिटल सर्किट द्वारा प्रक्रिया योग्य है। क्रमिक-सन्निकटन ADC के लिए रूपांतरण, विभेदन काल के लघुगणक के साथ, अर्थात् बिट्स की संख्या के साथ होता है। फ्लैश ADC निश्चित रूप से तीनों का सबसे तीव्र प्रकार है;रूपांतरण मूल रूप से एक ही समानांतर चरण में किया जाता है।

गति और सटीकता के बीच एक संभावित दुविधा (ट्रेडऑफ़) है। फ्लैश ADC में उतार-चढ़ाव होता है और तुलनित्र स्तरों से जुड़ी अनिश्चितताओं के परिणामस्वरूप खराब रैखिकता होती है। कुछ हद तक, क्रमिक-सन्निकटन ADCs के लिए खराब रैखिकता भी एक विषय हो सकता है। यहां, घटाव प्रक्रियाओं से त्रुटियों को जमा करने से अरैखिकता उत्पन्न होती है। विल्किंसन ADCs में तीनों की सबसे अच्छी रैखिकता है।[8][9]

स्लाइडिंग स्केल सिद्धांत

स्लाइडिंग स्केल या रैंडमाइजिंग विधि को किसी भी प्रकार के ADC की रैखिकता में सुधार करने के लिए नियोजित किया जा सकता है, लेकिन विशेष रूप से फ्लैश और क्रमिक सन्निकटन प्रकार में। किसी भी ADC के लिए इनपुट वोल्टेज से डिजिटल आउटपुट मान तक मैपिंग एक फ्लोर या सीलिंग फ़ंक्शन नहीं है जैसा कि यह होनी चाहिए। सामान्य परिस्थितियों में, एक विशेष आयाम की एक स्पंद हमेशा एक ही डिजिटल मूल्य में परिवर्तित हो जाती है। समस्या यह है कि अंकीकृत ( डिजिटाइज्ड ) मानों के लिए अनुरुप संख्या की सीमाएं सभी समान चौड़ाई में नहीं हैं, और अंतर रैखिकता औसत चौड़ाई से विचलन के साथ आनुपातिक रूप से घट जाती है। स्लाइडिंग स्केल सिद्धांत इस घटना को दूर करने के लिए एक औसत प्रभाव का उपयोग करता है। यादृच्छिक, लेकिन ज्ञात अनुरुप वोल्टता को सैंपल इनपुट वोल्टेज में जोड़ा जाता है। फिर इसे डिजिटल रूप में परिवर्तित कर दिया जाता है, और समतुल्य डिजिटल राशि को घटाया जाता है, इस प्रकार इसे अपने मूल मान में बहाल किया जाता है। लाभ यह है कि रूपांतरण एक यादृच्छिक बिंदु पर हुआ है। अंतिम स्तरों का सांख्यिकीय वितरण ADC की सीमा के एक क्षेत्र में एक भारित औसत द्वारा तय किया जाता है। यह बदले में इसे किसी भी विशिष्ट स्तर की चौड़ाई तक पहुंचाता है।[10][11]

प्रकार

इलेक्ट्रॉनिक अनुरुप से अंकीय परिवर्तक को लागू करने के ये कई सामान्य तरीके हैं।

प्रत्यक्ष-रूपांतरण

एक प्रत्यक्ष-रूपांतरण या फ्लैश ADC में एक विशिष्ट वोल्टेज रेंज के लिए समानांतर में इनपुट सिग्नल का नमूना लेने वाले तुलनित्रों ( कम्परेटर ) का एक बैंक होता है। तुलनित्र ( कम्परेटर ) बैंक एक लॉजिक सर्किट फीड करता है जो प्रत्येक वोल्टेज रेंज के लिए एक कोड उत्पन्न करता है।

इस प्रकार के ADCs में एक बड़ा आकार और उच्च शक्ति अपव्यय होता है। ये प्रायः वीडियो, वाइडबैंड संचार, या प्रकाशीय और चुंबकीय भंडारण में अन्य तेज संकेतों के लिए उपयोग किए जाते हैं।

सर्किट में एक प्रतिरोधात्मक विभक्त नेटवर्क, op-amp तुलनित्र का एक सेट और एक प्राथमिक संकेतक होता है। वोल्टेज सीमाओं पर किसी भी समस्या को हल करने के लिए तुलनित्र में अल्प मात्रा में शैथिल्य ( हिस्टैरिसीस ) बनाया गया है। प्रतिरोधक विभक्त के प्रत्येक नोड पर, एक संतुलक वोल्टेज उपलब्ध होता है। सर्किट का उद्देश्य प्रत्येक नोड वोल्टेज के साथ अनुरूप निविष्ट वोल्टता ( एनालॉग इनपुट वोल्टेज ) की तुलना करना है।

सर्किट में उच्च गति का लाभ होता है क्योंकि रूपांतरण क्रमिक रूप से होने के स्थान पर एक साथ होता है। विशिष्ट रूपांतरण समय 100 ns या उससे कम होता है। रूपांतरण समय केवल तुलनित्र की गति और प्राथमिक एन्कोडर द्वारा सीमित है। इस प्रकार के अनुरुप से अंकीय परिवर्तक (ADC) का नुकसान यह है कि प्रत्येक जोड़े गए बिट के लिए आवश्यक तुलनित्रों की संख्या लगभग दोगुनी होती है। साथ ही, n का मान जितना बड़ा होगा, प्राथमिक संकेतक उतना ही अधिक जटिल होगा।

क्रमिक सन्निकटन

एक क्रमिक-सन्निकटन ADC, एक तुलनित्र और एक द्विआधारी खोज का उपयोग करता है जो इनपुट वोल्टेज वाली एक सीमा को क्रमिक रूप से संकीर्ण करता है। प्रत्येक क्रमिक चरण में, कनवर्टर इनपुट वोल्टेज की तुलना एक आंतरिक डिजिटल से अनुरुप परिवर्तक ( कनवर्टर ) के आउटपुट से करता है जो शुरू में अनुमत इनपुट वोल्टेज रेंज के मध्य बिंदु का प्रतिनिधित्व करता है। इस प्रक्रिया में प्रत्येक चरण में, सन्निकटन को एक क्रमिक सन्निकटन रजिस्टर (SAR) में संग्रहीत किया जाता है और डिजिटल से अनुरुप परिवर्तक ( एनालॉग कनवर्टर ) के आउटपुट को एक संकीर्ण सीमा पर तुलना के लिए अपडेट किया जाता है।

रैंप-तुलना

एक रैंप-तुलना ( रैंप-कम्पेयर ) ADC एक आरा-दांत संकेत का उत्पादन करता है जो ऊपर या नीचे रैंप करता है और फिर शीघ्रता से शून्य पर लौटता है।[12] जब रैंप शुरू होता है, तो एक टाइमर की गिनती शुरू होती है। जब रैंप वोल्टेज इनपुट से मेल खाता है, तो एक तुलनित्र आग लगाता है, और टाइमर का मान दर्ज किया जाता है। समयबद्ध रैंप परिवर्तक को आर्थिक रूप से लागू किया जा सकता है,[lower-alpha 1] हालांकि, रैंप का समय तापमान के प्रति संवेदनशील हो सकता है क्योंकि रैंप उत्पन्न करने वाला सर्किट अक्सर एक साधारण अनुरूप समाकलित्र ( एनालॉग इंटीग्रेटर ) होता है। अधिक सटीक कनवर्टर एक डिजिटल-टू-एनालॉग कनवर्टर ड्राइविंग एक क्लॉक्ड काउंटर का उपयोग करता है, जो एक DAC चलाता है। रैंप-कम्पेयर सिस्टम का एक विशेष लाभ यह है कि एक दूसरे संकेत को परिवर्तित करने के लिए बस एक और तुलनित्र और टाइमर मूल्य को संग्रहीत करने के लिए एक और रजिस्टर की आवश्यकता होती है। रूपांतरण के दौरान इनपुट परिवर्तनों के प्रति संवेदनशीलता को कम करने के लिए, एक नमूना और होल्ड एक संधारित्र को तात्कालिक इनपुट वोल्टेज के साथ चार्ज कर सकता है और परिवर्तक को निरंतर करंट के साथ डिस्चार्ज होने में समय लग सकता है।

विल्किनसन

विल्किनसन ADC को 1950 में डेनिस विल्किनसन द्वारा डिजाइन किया गया था। विल्किन्सन ADC एक चार्जिंग संधारित्र द्वारा उत्पादित इनपुट वोल्टेज की तुलना पर आधारित होता है। संधारित्र को तब तक चार्ज करने की अनुमति दी जाती है जब तक एक तुलनित्र यह निर्धारित नहीं करता कि यह इनपुट वोल्टेज से मेल खाता है। फिर, संधारित्र को रैखिक रूप से मुक्त कर दिया जाता है। संधारित्र को मुक्त (डिस्चार्ज) करने में लगा समय इनपुट वोल्टेज के आयाम के समानुपाती होता है। जबकि संधारित्र मुक्त (डिस्चार्ज) हो रहा है, एक उच्च-आवृत्ति दोलक ( ऑसिलेटर ) घड़ी से स्पंदन को एक रजिस्टर द्वारा गिना जाता है। रजिस्टर में दर्ज घड़ी स्पंदन (क्लॉक पल्स) की संख्या भी इनपुट वोल्टेज के समानुपाती होती है।[14][15]

एकीकृत

एक एकीकृत ADC ( दोहरी ढलान या बहु-ढलान ADC भी ) एक समाकलित्र ( इंटीग्रेटर ) के इनपुट पर अज्ञात इनपुट वोल्टेज को लागू करता है और वोल्टेज को एक निश्चित समय अवधि ( रन-अप अवधि ) के लिए रैंप करने की अनुमति देता है। फिर विपरीत ध्रुवीयता के एक ज्ञात संदर्भ वोल्टेज को समाकलित्र पर लागू किया जाता है और इसे तब तक रैंप करने की अनुमति दी जाती है जब तक कि इंटीग्रेटर आउटपुट शून्य ( रन-डाउन अवधि ) पर वापस न आ जाए। इनपुट वोल्टेज की गणना, संदर्भ वोल्टेज के एक फ़ंक्शन के रूप में निरंतर रन-अप समय अवधि और मापी गई रन-डाउन समय अवधि के रूप में की जाती है। रन-डाउन समय की माप आमतौर पर कनवर्टर की घड़ी की इकाइयों में की जाती है, इसलिए लंबे समय तक एकीकरण समय उच्च विभेदन की अनुमति देता है। इसी तरह, विभेदन (रेजोल्यूशन) का त्याग करके कनवर्टर की गति में सुधार किया जा सकता है। इस प्रकार के कन्वर्टर्स (या अवधारणा पर भिन्नता) का उपयोग अधिकांश डिजिटल वोल्टमीटर में उनकी रैखिकता और लचीलेपन (फ्लेक्सीबिलिटी) के लिए किया जाता है।

- चार्ज संतुलन ADC

- चार्ज संतुलन ADC का सिद्धांत पहले इनपुट सिग्नल को वोल्टेज-टू-फ़्रीक्वेंसी कनवर्टर का उपयोग करके आवृत्ति में परिवर्तित करना है। इस आवृत्ति को तब एक काउंटर द्वारा मापा जाता है और एनालॉग इनपुट के आनुपातिक आउटपुट कोड में परिवर्तित किया जाता है। इन कन्वर्टर्स का मुख्य लाभ यह है कि शोर वातावरण में या पृथक रूप में भी आवृत्ति को संचारित करना संभव है। हालांकि, इस सर्किट की सीमा यह है कि वोल्टेज-टू-फ़्रीक्वेंसी कनवर्टर का आउटपुट एक RC उत्पाद पर निर्भर करता है जिसका मान, तापमान और समय पर सटीक रूप से नहीं बनाए रखा जा सकता है।

द्वि-ढलान ADC

- सर्किट के अनुरूप ( एनालॉग ) भाग में एक उच्च इनपुट प्रतिबाधा बफर, सुनिश्चित समाकलित्र और एक वोल्टेज तुलनित्र होता है। परिवर्तक ( कनवर्टर ) पहले एक निश्चित अवधि के लिए एनालॉग इनपुट सिग्नल को एकीकृत करता है और फिर यह विपरीत ध्रुवीयता के एक आंतरिक संकेत वोल्टेज को एकीकृत करता है जब तक कि इंटीग्रेटर आउटपुट शून्य न हो। इस सर्किट का मुख्य दोष लंबी अवधि का समय है। ये विशेष रूप से धीरे -धीरे अलग -अलग संकेतों जैसे कि थर्मोकपल्स और वजन तराजू के सटीक माप के लिए उपयुक्त हैं।

डेल्टा-कूटलिखित ( एन्कोडेड )

एक डेल्टा-एन्कोडेड या काउंटर-रैंप ADC में एक अप-डाउन काउंटर होता है जो एक डिजिटल से एनालॉग कनवर्टर (DAC) को फीड करता है। इनपुट सिग्नल और DAC दोनों एक तुलनित्र में जाते हैं। तुलनित्र काउंटर को नियंत्रित करता है। सर्किट काउंटर को समायोजित करने के लिए तुलनित्र से नकारात्मक प्रतिक्रिया का उपयोग करता है जब तक कि DAC का आउटपुट इनपुट सिग्नल से मेल नहीं खाता है और काउंटर से संख्या पढ़ी जाती है। डेल्टा कन्वर्टर्स में बहुत व्यापक रेंज और उच्च रिज़ॉल्यूशन होता है, लेकिन रूपांतरण समय इनपुट सिग्नल व्यवहार पर निर्भर होता है, यद्यपि इसमें हमेशा सबसे निकृष्टतम स्थिति की आश्वस्तता (गारंटी) होगी। डेल्टा कन्वर्टर्स अक्सर वास्तविक दुनिया के संकेतों को पढ़ने के लिए बहुत अच्छे विकल्प होते हैं क्योंकि भौतिक प्रणालियों के अधिकांश संकेत अकस्मात नहीं बदलते हैं। कुछ कन्वर्टर्स डेल्टा और क्रमिक सन्निकटन दृष्टिकोण को जोड़ते हैं, यह विशेष रूप से अच्छी तरह से कार्य करता है जब इनपुट सिग्नल के उच्च आवृत्ति घटकों को परिमाण में छोटा माना जाता है।

पाइपलाइन

एक पाइपलाइज्ड अनुरुप से अंकीय परिवर्तक (जिसे सबरेंजिंग क्वांटाइज़र भी कहा जाता है) दो या अधिक रूपांतरण चरणों का उपयोग करता है। सबसे पहले, एक अपरिष्कृत रूपांतरण किया जाता है। दूसरे चरण में, इनपुट सिग्नल के अंतर को डिजिटल से एनालॉग कनवर्टर (DAC) के साथ निर्धारित किया जाता है। यह अंतर तब अधिक सटीक रूप से परिवर्तित होता है और परिणाम अंतिम चरण में संयुक्त होता हैं। इसे क्रमिक-सन्निकटन ADC का परिशोधन माना जा सकता है जिसमें प्रतिक्रिया संदर्भ संकेत में केवल अगले-सबसे महत्वपूर्ण बिट के बजाय बिट्स की एक पूरी श्रृंखला (उदाहरण के लिए, चार बिट्स) का अंतरिम रूपांतरण होता है। क्रमिक सन्निकटन और फ्लैश ADC के गुणों के संयोजन का यह प्रकार तीव्र है, इसका उच्च रिज़ॉल्यूशन है और इसे कुशलता से लागू किया जा सकता है।

सिग्मा-डेल्टा

एक सिग्मा-डेल्टा ADC (जिसे डेल्टा-सिग्मा ADC भी कहा जाता है), एक बड़े कारक द्वारा आने वाले सिग्नल को आवश्यकता से कम बिट्स व फ्लैश ADC का उपयोग करके परिवर्तित किया जाता है और वांछित सिग्नल बैंड को फ़िल्टर किया जाता है। परिणामी संकेत, फ्लैश के असतत स्तरों द्वारा उत्पन्न त्रुटि के साथ, वापस फीड किया जाता है और इनपुट से फ़िल्टर में घटाया जाता है। इस नकारात्मक प्रतिक्रिया के परिमाणीकरण त्रुटि को आकार देने वाले शोर का प्रभाव है कि वांछित सिग्नल आवृत्तियों में प्रकट नहीं होता है। एक डिजिटल फ़िल्टर (डिकिमेशन फ़िल्टर) ADC का अनुसरण करता है जो नमूनाकरण दर को कम करता है, अवांछित ध्वनि सिग्नल को फिल्टर करता है और आउटपुट के विभेदन ( रिज़ॉल्यूशन ) को बढ़ाता है।

समय-अंतरापत्रित (टाइम-इंटरलेवेड)

एक समय-अंतरापत्रित अनुरुप से अंकीय परिवर्तक (ADC) एम समानांतर ADCs का उपयोग करता है जहां प्रत्येक ADC प्रभावी प्रतिदर्श (सैम्पल) घड़ी के प्रत्येक M वें चक्र के डेटा का नमूना लेता है। परिणाम यह है कि प्रत्येक ADC जो प्रबंधन कर सकता है उसकी तुलना में नमूना दर M गुना बढ़ जाती है। अभ्यास में, M ADCs के बीच अलग-अलग अंतर समग्र प्रदर्शन को कम कर देता है जो कि सहज-मुक्त गतिशील रेंज (SFDR) को कम करता है। हालांकि, समय-अंतरापत्रित (टाइम-इंटरलेवेड) बेमेल त्रुटियों को ठीक करने के लिए कई तकनीक मौजूद हैं।[16]

इंटरमीडिएट FM चरण

एक इंटरमीडिएट FM चरण के साथ एक अनुरुप से अंकीय परिवर्तक, पहले इनपुट सिग्नल के वोल्टेज के लिए एक आवृत्ति आनुपातिक के साथ एक आवृत्ति के साथ एक दोलन संकेत का उत्पादन करने के लिए एक वोल्टेज-से-आवृति परिवर्तक का उपयोग करता है और फिर उस आवृत्ति को वांछित सिग्नल वोल्टेज के आनुपातिक अंकीय गणना में परिवर्तित करने के लिए आवृत्ति गणक ( काउंटर ) का उपयोग करता है। लंबे समय तक एकीकरण समय उच्च विभेदन के लिए अनुमति देता है। इसी तरह, विभेदन (रिज़ॉल्यूशन) का त्याग करके कनवर्टर की गति में सुधार किया जा सकता है। ADC के दो भागों को व्यापक रूप से अलग किया जा सकता है जैसे आवृत्ति संकेत, ऑप्टो-आइसोलेटर के माध्यम से पारित किया जाता है या वायरलेस रूप से प्रेषित होता है। ऐसे कुछ ADCs साइन तरंग या स्क्वायर तरंग फ्रीक्वेंसी मॉड्यूलेशन का उपयोग करते हैं, अन्य पल्स-फ्रीक्वेंसी मॉड्यूलेशन का उपयोग करते हैं। इस तरह के ADCs एक बार एक दूरस्थ एनालॉग सेंसर की स्थिति का डिजिटल प्रदर्शन दिखाने के लिए सबसे लोकप्रिय तरीका थे।[17][18][19][20][21]

समय विस्तार

एक समय विस्तार अनुरुप से अंकीय परिवर्तक (TS-ADC) एक बहुत ही विस्तृत बैंड चौड़ाई अनुरूप संकेत को अंकीकृत करता है, जिसे अंकीकरण ( डिजिटाइजेशन ) से पहले सिग्नल को समय-तनाव द्वारा एक परम्परागत इलेक्ट्रॉनिक ADC द्वारा अंकीकृत नहीं किया जा सकता है। यह सामान्यतः सिग्नल को टाइम-स्ट्रेच करने के लिए एक फोटोनिक प्रीप्रोसेसर का उपयोग करता है, जो समय पर सिग्नल को प्रभावी ढंग से धीमा कर देता है और इसकी बैंड चैड़ाई को संपीड़ित करता है।परिणामतः, एक इलेक्ट्रॉनिक ADC, जो मूल सिग्नल को पकड़ने में बहुत धीमा होता है, अब इस धीमे-धीमे सिग्नल को पकड़ सकता है। सिग्नल के निरंतर कैप्चर के लिए, फ्रंटेंड भी समय-स्ट्रेचिंग के अलावा सिग्नल को कई खंडों में विभाजित करता है। प्रत्येक खंड को व्यक्तिगत रूप से एक अलग इलेक्ट्रॉनिक ADC द्वारा अंकीकृत ( डिजिटाइज़ ) किया जाता है। अंत में, एक डिजिटल सिग्नल प्रोसेसर नमूनों को पुनर्व्यवस्थित करता है और प्रीप्रोसेसर द्वारा जोड़े गए किसी भी विकृतियों को बाइनरी डेटा उत्पन्न करने के लिए हटा देता है जो मूल अनुरूप संकेत का डिजिटल प्रतिनिधित्व है।

वाणिज्यिक

This section does not cite any sources. (July 2018) (Learn how and when to remove this template message) |

कई मामलों में, एक एकीकृत सर्किट का सबसे महंगा हिस्सा पिन होता है, क्योंकि वे पैकेज को बड़ा बनाते हैं, और प्रत्येक पिन को एकीकृत सर्किट के सिलिकॉन से जोड़ा जाना होता है। पिन को बचाने के लिए, ADCs द्वारा कंप्यूटर में एक क्रमिक अंतरापृष्ठ ( सीरियल इंटरफ़ेस ) पर एक बार में अपना एक बिट डेटा भेजना सामान्य बात है, प्रत्येक बिट के साथ घड़ी संकेत की स्थिति बदल जाती है। यह ADC पैकेज पर पर्याप्त पिन बचाता है, और अनेक स्थितियों में, सभी डिजाइन को और अधिक जटिल नहीं बनाता है।

वाणिज्यिक ADCs में अक्सर कई इनपुट होते हैं जो एक कनवर्टर को सामान्यत: एक एनालॉग मल्टीप्लेक्सर के माध्यम से फीड करते हैं। ADC के विभिन्न मॉडलों में नमूने और होल्ड सर्किट, यंत्र विन्यास प्रवर्धक ( इंस्ट्रूमेंटेशन एम्पलीफायर ) या डिफरेंशियल इनपुट शामिल हो सकते हैं, जहां मापी गई मात्रा दो इनपुट के बीच का अंतर है।

अनुप्रयोग

संगीत रिकॉर्डिंग

एनालॉग-टू-डिजिटल कन्वर्टर्स आधुनिक संगीत पुनरुत्पत्ति प्रौद्योगिकी और डिजिटल ऑडियो वर्कस्टेशन-आधारित ध्वनि रिकॉर्डिंग के अभिन्न अंग हैं। एनालॉग रिकॉर्डिंग का उपयोग करके कंप्यूटर पर संगीत का उत्पादन किया जा सकता है और इसलिए कॉम्पैक्ट डिस्क और डिजिटल म्यूजिक फाइलों पर जाने वाले पल्स-कोड मॉड्यूलेशन (PCM) डेटा स्ट्रीम को बनाने के लिए एनालॉग-टू-डिजिटल कन्वर्टर्स की आवश्यकता होती है। संगीत में उपयोग किए जाने वाले एनालॉग-टू-डिजिटल कन्वर्टर्स की वर्तमान क्रॉप 192 किलोहर्ट्ज़ तक की दरों पर नमूना ले सकती है। कई रिकॉर्डिंग स्टूडियो 24-बिट/96 किलोहर्ट्ज़ पल्स-कोड मॉड्यूलेशन (PCM) प्रारूप में रिकॉर्ड करते हैं और फिर कॉम्पैक्ट डिस्क डिजिटल ऑडियो प्रोडक्शन (44.1 किलोहर्ट्ज़) या रेडियो और टेलीविज़न प्रसारण अनुप्रयोगों के लिए 48 किलोहर्ट्ज़ के सिग्नल को कम करते हैं।

अंकीय संकेत प्रक्रिया ( डिजिटल सिग्नल प्रोसेसिंग )

डिजिटल सिग्नल प्रोसेसिंग सिस्टम में अनुरुप से अंकीय परिवर्तक (ADC) की आवश्यकता होती है जो डिजिटल रूप में किसी भी अनुरूप संकेत को प्रोसेस, स्टोर या ट्रांसपोर्ट करता है। टीवी ट्यूनर कार्ड, उदाहरण के लिए, तेज़ वीडियो एनालॉग-टू-डिजिटल कन्वर्टर्स का उपयोग करते हैं। धीमी ऑन-चिप 8-, 10-, 12- या 16-बिट एनालॉग-टू-डिजिटल कन्वर्टर्स माइक्रोकंट्रोलर में सामान्य हैं। डिजिटल स्टोरेज ऑसिलोस्कोप को बहुत तेज़ एनालॉग-टू-डिजिटल कन्वर्टर्स की आवश्यकता होती है, जो सॉफ्टवेयर-परिभाषित रेडियो और उनके नए अनुप्रयोगों के लिए भी महत्वपूर्ण है।

वैज्ञानिक उपकरण

डिजिटल इमेजिंग सिस्टम सामान्यत: पिक्सल को अंकीकृत ( डिजिटाइज़ ) करने के लिए एनालॉग-टू-डिजिटल कन्वर्टर्स का उपयोग करते हैं। कुछ रडार सिस्टम सिग्नल क्षमता को अनुगामी सिग्नल प्रसंस्करण ( प्रोसेसिंग ) के लिए अंकीय मान में बदलने के लिए एनालॉग-टू-डिजिटल कन्वर्टर्स का उपयोग करते हैं। Situ और रिमोट सेंसिंग सिस्टम में कई अन्य सामान्यत: समान तकनीक का उपयोग करते हैं।

वैज्ञानिक उपकरणों में कई सेंसर एक अनुरूप संकेत तापमान, दाब, पीएच, प्रकाश की तीव्रता आदि का उत्पादन करते हैं। इन सभी संकेतों के डिजिटल प्रतिरूप का उत्पादन करने के लिए अनुरुप से अंकीय परिवर्तक (ADC) को प्रवर्धित और फेड किया जा सकता है।

चक्रीय संकेतक ( रोटरी एनकोडर )

कुछ गैर-इलेक्ट्रॉनिक या केवल आंशिक रूप से इलेक्ट्रॉनिक उपकरण, जैसे चक्रीय संकेतक ( रोटरी एनकोडर ), को भी ADCs माना जा सकता है। विशिष्ट रूप से ADC का डिजिटल आउटपुट एक द्विपूरक बाइनरी नंबर होगा जो इनपुट के समानुपाती होता है। एक संकेतक एक ग्रे कोड आउटपुट कर सकता है।

डिस्प्ले

फ्लैट-पैनल डिस्प्ले स्वाभाविक रूप से डिजिटल होते हैं और एक अनूरूप ( एनालॉग ) सिग्नल जैसे संयुक्त या VGA को संसाधित करने के लिए ADC की आवश्यकता होती है।

विद्युतीय प्रतीक

परीक्षण

This section does not cite any sources. (July 2022) (Learn how and when to remove this template message) |

अनुरुप से अंकीय परिवर्तक का परीक्षण करने के लिए नियंत्रण सिग्नल भेजने और डिजिटल डेटा आउटपुट कैप्चर करने के लिए एक एनालॉग इनपुट स्रोत और हार्डवेयर की आवश्यकता होती है। कुछ एडीसी को संदर्भ संकेत के सटीक स्रोत की भी आवश्यकता होती है।

अनुरुप से अंकीय परिवर्तक का परीक्षण करने के लिए प्रमुख मापदंड हैं:

- डीसी प्रतिसंतुलन त्रुटि

- डीसी लाभ त्रुटि

- सिग्नल-टू-शोर अनुपात (SNR)

- कुल हार्मोनिक विरूपण (THD)

- अभिन्न अरैखिकता (INL)

- विभेदक अरैखिकता (DNL)

- मिथ्या मुक्त गतिशील सीमा

- शक्ति का अपव्यय

यह भी देखें

- अनुकूली भविष्यसूचक कोडिंग, एक प्रकार का ADC जिसमें सिग्नल का मान एक रैखिक फ़ंक्शन द्वारा पूर्वकथित होता है

- ऑडियो कोडेक

- बीटा संकेतक

- डिजिटलीकरण

- अंकीय संकेत प्रक्रिया

- अभिन्न रैखिकता

- मॉडेम

टिप्पणियाँ

संदर्भ

- ↑ "Principles of Data Acquisition and Conversion" (PDF). Texas Instruments. April 2015. Retrieved October 18, 2016.

- ↑ Lathi, B.P. (1998). Modern Digital and Analog Communication Systems (3rd ed.). Oxford University Press.

- ↑ "Maxim App 800: Design a Low-Jitter Clock for High-Speed Data Converters", maxim-ic.com, July 17, 2002

- ↑ "Jitter effects on Analog to Digital and Digital to Analog Converters" (PDF). Retrieved August 19, 2012.

- ↑ Löhning, Michael; Fettweis, Gerhard (2007). "The effects of aperture jitter and clock jitter in wideband ADCs". Computer Standards & Interfaces Archive. 29 (1): 11–18. CiteSeerX 10.1.1.3.9217. doi:10.1016/j.csi.2005.12.005.

- ↑ Redmayne, Derek; Steer, Alison (December 8, 2008), "Understanding the effect of clock jitter on high-speed ADCs", eetimes.com

- ↑ "RF-Sampling and GSPS ADCs – Breakthrough ADCs Revolutionize Radio Architectures" (PDF). Texas Instruments. Retrieved November 4, 2013.

- ↑ Knoll (1989, pp. 664–665)

- ↑ Nicholson (1974, pp. 313–315)

- ↑ Knoll (1989, pp. 665–666)

- ↑ Nicholson (1974, pp. 315–316)

- ↑ Couch - 2001 - Digital and analog communication systems - Prentice Hall - New Jersey, USA

- ↑ "Atmel Application Note AVR400: Low Cost A/D Converter" (PDF). atmel.com.

- ↑ Knoll (1989, pp. 663–664)

- ↑ Nicholson (1974, pp. 309–310)

- ↑ Gabriele Manganaro; David H. Robertson (July 2015), Interleaving ADCs: Unraveling the Mysteries, Analog Devices, retrieved October 7, 2021

- ↑ Analog Devices MT-028 Tutorial: "Voltage-to-Frequency Converters" by Walt Kester and James Bryant 2009, apparently adapted from Kester, Walter Allan (2005) Data conversion handbook, Newnes, p. 274, ISBN 0750678410.

- ↑ Microchip AN795 "Voltage to Frequency / Frequency to Voltage Converter" p. 4: "13-bit A/D converter"

- ↑ Carr, Joseph J. (1996) Elements of electronic instrumentation and measurement, Prentice Hall, p. 402, ISBN 0133416860.

- ↑ "Voltage-to-Frequency Analog-to-Digital Converters". globalspec.com

- ↑ Pease, Robert A. (1991) Troubleshooting Analog Circuits, Newnes, p. 130, ISBN 0750694998.

- Knoll, Glenn F. (1989). Radiation Detection and Measurement (2nd ed.). New York: John Wiley & Sons. ISBN 978-0471815044.

- Nicholson, P. W. (1974). Nuclear Electronics. New York: John Wiley & Sons. pp. 315–316. ISBN 978-0471636977.

अग्रिम पठन

- Allen, Phillip E.; Holberg, Douglas R. (2002). CMOS Analog Circuit Design. ISBN 978-0-19-511644-1.

- Fraden, Jacob (2010). Handbook of Modern Sensors: Physics, Designs, and Applications. Springer. ISBN 978-1441964656.

- Kester, Walt, ed. (2005). The Data Conversion Handbook. Elsevier: Newnes. ISBN 978-0-7506-7841-4.

- Johns, David; Martin, Ken (1997). Analog Integrated Circuit Design. ISBN 978-0-471-14448-9.

- Liu, Mingliang (2006). Demystifying Switched-Capacitor Circuits. ISBN 978-0-7506-7907-7.

- Norsworthy, Steven R.; Schreier, Richard; Temes, Gabor C. (1997). Delta-Sigma Data Converters. IEEE Press. ISBN 978-0-7803-1045-2.

- Razavi, Behzad (1995). Principles of Data Conversion System Design. New York, NY: IEEE Press. ISBN 978-0-7803-1093-3.

- Ndjountche, Tertulien (May 24, 2011). CMOS Analog Integrated Circuits: High-Speed and Power-Efficient Design. Boca Raton, FL: CRC Press. ISBN 978-1-4398-5491-4.

- Staller, Len (February 24, 2005). "Understanding analog to digital converter specifications". Embedded Systems Design.

- Walden, R. H. (1999). "Analog-to-digital converter survey and analysis". IEEE Journal on Selected Areas in Communications. 17 (4): 539–550. CiteSeerX 10.1.1.352.1881. doi:10.1109/49.761034.

बाहरी संबंध

- An Introduction to Delta Sigma Converters A very nice overview of Delta-Sigma converter theory.

- Digital Dynamic Analysis of A/D Conversion Systems through Evaluation Software based on FFT/DFT Analysis RF Expo East, 1987

- Which ADC Architecture Is Right for Your Application? article by Walt Kester

- ADC and DAC Glossary Archived November 24, 2009, at the Wayback Machine Defines commonly used technical terms.

- Introduction to ADC in AVR – Analog to digital conversion with Atmel microcontrollers

- Signal processing and system aspects of time-interleaved ADCs.

- Explanation of analog-digital converters with interactive principles of operations.

- MATLAB Simulink model of a simple ramp ADC.

]