थ्रेशोल्ड वोल्टेज: Difference between revisions

(Created page with "{{Short description|Minimum source-to-gate voltage for a field effect transistor to be conducting from source to drain}} {{Use American English|date = March 2019}} {{anchor|LV...") |

m (Abhishek moved page सीमा वोल्टेज to थ्रेशोल्ड वोल्टेज without leaving a redirect) |

(No difference)

| |

Revision as of 16:15, 10 May 2023

थ्रेशोल्ड वोल्टेज, जिसे आमतौर पर वी के रूप में संक्षिप्त किया जाता हैth या वीGS(th), एक फील्ड इफ़ेक्ट ट्रांजिस्टर (FET) का न्यूनतम गेट-टू-सोर्स वोल्टेज (VGS) जो स्रोत और नाली टर्मिनलों के बीच एक संवाहक पथ बनाने के लिए आवश्यक है। बिजली दक्षता बनाए रखने के लिए यह एक महत्वपूर्ण स्केलिंग कारक है।

JFET|जंक्शन फील्ड-इफेक्ट ट्रांजिस्टर (JFET) का जिक्र करते समय, दहलीज वोल्टेज को अक्सर इसके बजाय पिंच-ऑफ वोल्टेज कहा जाता है।[1][2] यह कुछ हद तक भ्रमित करने वाला है क्योंकि IGFET|इन्सुलेटेड-गेट फील्ड-इफेक्ट ट्रांजिस्टर (IGFET) पर लागू पिंच ऑफ चैनल लंबाई मॉडुलन को संदर्भित करता है जो उच्च स्रोत-ड्रेन बायस के तहत वर्तमान संतृप्ति व्यवहार की ओर जाता है, भले ही वर्तमान कभी बंद न हो। पिंच ऑफ के विपरीत, दहलीज वोल्टेज शब्द स्पष्ट है और किसी भी क्षेत्र-प्रभाव ट्रांजिस्टर में समान अवधारणा को संदर्भित करता है।

मूल सिद्धांत

एन-टाइप सेमीकंडक्टर | एन-चैनल एन्हांसमेंट-मोड डिवाइस में, ट्रांजिस्टर के भीतर एक प्रवाहकीय चैनल स्वाभाविक रूप से मौजूद नहीं होता है, और ऐसा एक बनाने के लिए एक सकारात्मक गेट-टू-सोर्स वोल्टेज आवश्यक है। सकारात्मक वोल्टेज प्रवाहकीय चैनल बनाने, गेट की ओर शरीर के भीतर फ्री-फ्लोटिंग इलेक्ट्रॉनों को आकर्षित करता है। लेकिन पहले, FET के शरीर में जोड़े गए डोपेंट आयनों का मुकाबला करने के लिए पर्याप्त इलेक्ट्रॉनों को गेट के पास आकर्षित किया जाना चाहिए; यह एक ऐसा क्षेत्र बनाता है जिसमें कोई मोबाइल वाहक नहीं होता है जिसे कमी क्षेत्र कहा जाता है, और जिस वोल्टेज पर यह होता है वह FET का थ्रेशोल्ड वोल्टेज होता है। आगे गेट-टू-सोर्स वोल्टेज वृद्धि गेट की ओर और भी अधिक इलेक्ट्रॉनों को आकर्षित करेगी जो स्रोत से नाली तक एक प्रवाहकीय चैनल बनाने में सक्षम हैं; इस प्रक्रिया को उलटा कहा जाता है। पी-चैनल एन्हांसमेंट-मोड एमओएस ट्रांजिस्टर के लिए रिवर्स सही है। जब वीGS = 0 डिवाइस "बंद" है और चैनल खुला / गैर-संचालन है। पी-टाइप एन्हांसमेंट-मोड MOSFET के लिए एक नकारात्मक गेट वोल्टेज का अनुप्रयोग इसे "चालू" करने वाले चैनलों की चालकता को बढ़ाता है।

इसके विपरीत, एन-चैनल रिक्तीकरण-मोड उपकरणों में एक प्रवाहकीय चैनल होता है जो स्वाभाविक रूप से ट्रांजिस्टर के भीतर मौजूद होता है। तदनुसार, थ्रेशोल्ड वोल्टेज शब्द ऐसे उपकरणों को चालू करने के लिए आसानी से लागू नहीं होता है, बल्कि इसका उपयोग वोल्टेज स्तर को इंगित करने के लिए किया जाता है, जिस पर चैनल इतना चौड़ा होता है कि इलेक्ट्रॉनों को आसानी से प्रवाहित किया जा सके। यह आसानी से बहने वाला थ्रेशोल्ड पी-प्रकार अर्धचालक | पी-चैनल डिप्लेशन-मोड डिवाइस पर भी लागू होता है, जिसमें गेट से बॉडी/स्रोत तक एक नकारात्मक वोल्टेज गेट-इन्सुलेटर से सकारात्मक रूप से चार्ज किए गए छिद्रों को मजबूर करके एक कमी परत बनाता है। / सेमीकंडक्टर इंटरफ़ेस, स्थिर, नकारात्मक रूप से चार्ज किए गए स्वीकर्ता आयनों के एक वाहक-मुक्त क्षेत्र को उजागर करता है।

एन-चैनल रिक्तीकरण एमओएस ट्रांजिस्टर के लिए, एक नकारात्मक गेट-स्रोत वोल्टेज समाप्त हो जाएगा (इसलिए इसका नाम) ट्रांजिस्टर "ऑफ" स्विच करने वाले अपने मुक्त इलेक्ट्रॉनों के प्रवाहकीय चैनल। इसी तरह एक पी-चैनल रिक्तीकरण-मोड एमओएस ट्रांजिस्टर के लिए एक सकारात्मक गेट-स्रोत वोल्टेज अपने मुक्त छिद्रों के चैनल को "बंद" कर देगा।

वाइड प्लानर ट्रांजिस्टर में थ्रेशोल्ड वोल्टेज ड्रेन-सोर्स वोल्टेज से अनिवार्य रूप से स्वतंत्र होता है और इसलिए यह एक अच्छी तरह से परिभाषित विशेषता है, हालांकि ड्रेन-प्रेरित बैरियर कम होने के कारण यह आधुनिक नैनोमीटर-आकार के MOSFETs में कम स्पष्ट है।

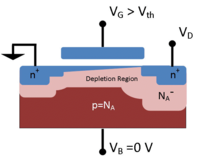

आंकड़ों में, भारी डोप्ड (नीला) एन-क्षेत्रों को इंगित करने के लिए स्रोत (बाईं ओर) और नाली (दाईं ओर) को n+ लेबल किया गया है। कमी परत डोपेंट को एन लेबल किया गया हैA− यह इंगित करने के लिए कि (गुलाबी) अवक्षय परत में आयन ऋणात्मक रूप से आवेशित हैं और बहुत कम छिद्र हैं। (लाल) बल्क में छिद्रों की संख्या p=NAबल्क चार्ज को न्यूट्रल बनाना।

यदि गेट वोल्टेज दहलीज वोल्टेज (बाएं आंकड़ा) से नीचे है, तो एन्हांसमेंट-मोड ट्रांजिस्टर बंद हो जाता है और आदर्श रूप से नाली से ट्रांजिस्टर के स्रोत तक कोई विद्युत प्रवाह नहीं होता है। वास्तव में, थ्रेशोल्ड (सबथ्रेशोल्ड रिसाव ) करंट के नीचे गेट बायसेस के लिए भी एक करंट होता है, हालांकि यह छोटा होता है और गेट बायस के साथ घातीय रूप से भिन्न होता है। इसलिए, डेटाशीट वर्तमान की निर्दिष्ट औसत दर्जे की मात्रा (आमतौर पर 250 μA या 1 mA) के अनुसार थ्रेसहोल्ड वोल्टेज निर्दिष्ट करेगी।

यदि गेट वोल्टेज थ्रेशोल्ड वोल्टेज (सही आंकड़ा) से ऊपर है, तो एन्हांसमेंट-मोड ट्रांजिस्टर चालू हो जाता है, क्योंकि ऑक्साइड-सिलिकॉन इंटरफ़ेस में चैनल में कई इलेक्ट्रॉन होते हैं, एक कम-प्रतिरोध चैनल बनाते हैं जहां से चार्ज प्रवाहित हो सकता है। स्रोत के लिए नाली। दहलीज से काफी अधिक वोल्टेज के लिए, इस स्थिति को मजबूत उलटा कहा जाता है। जब चैनल टेप किया जाता है VD > 0 क्योंकि प्रतिरोधक चैनल में करंट के कारण वोल्टेज में गिरावट चैनल का समर्थन करने वाले ऑक्साइड क्षेत्र को कम कर देती है क्योंकि नाली से संपर्क किया जाता है।

शारीरिक प्रभाव

शरीर प्रभाव स्रोत-बल्क वोल्टेज में परिवर्तन के बराबर राशि से थ्रेशोल्ड वोल्टेज में परिवर्तन है, , क्योंकि शरीर दहलीज वोल्टेज को प्रभावित करता है (जब यह स्रोत से बंधा नहीं होता है)। इसे दूसरे गेट के रूप में माना जा सकता है, और कभी-कभी इसे बैक गेट के रूप में संदर्भित किया जाता है, और तदनुसार शरीर के प्रभाव को कभी-कभी बैक-गेट प्रभाव कहा जाता है।[3] एन्हांसमेंट-मोड nMOS MOSFET के लिए, थ्रेशोल्ड वोल्टेज पर शरीर के प्रभाव की गणना शिचमैन-होजेस मॉडल के अनुसार की जाती है,[4] जो पुराने प्रोसेस नोड्स के लिए सटीक है,[clarification needed] निम्नलिखित समीकरण का उपयोग करते हुए:

कहाँ;

दहलीज वोल्टेज है जब सब्सट्रेट पूर्वाग्रह मौजूद है,

स्रोत-टू-बॉडी सब्सट्रेट पूर्वाग्रह है,

सतह क्षमता है,

शून्य सब्सट्रेट पूर्वाग्रह के लिए थ्रेसहोल्ड वोल्टेज है,

शरीर प्रभाव पैरामीटर है,

ऑक्साइड की मोटाई है,

ऑक्साइड परावैद्युतांक है,

सिलिकॉन की पारगम्यता है,

एक डोपिंग एकाग्रता है,

प्राथमिक प्रभार है।

ऑक्साइड की मोटाई पर निर्भरता

किसी दिए गए प्रौद्योगिकी नोड में, जैसे कि 90 नैनोमीटर | 90-एनएम सीएमओएस प्रक्रिया, थ्रेशोल्ड वोल्टेज ऑक्साइड की पसंद और ऑक्साइड की मोटाई पर निर्भर करता है। ऊपर दिए गए बॉडी फ़ार्मुलों का उपयोग करके, के सीधे आनुपातिक है , और , जो ऑक्साइड मोटाई के लिए पैरामीटर है।

इस प्रकार, ऑक्साइड की मोटाई जितनी पतली होगी, थ्रेशोल्ड वोल्टेज उतना ही कम होगा। हालांकि यह एक सुधार प्रतीत हो सकता है, यह बिना लागत के नहीं है; क्योंकि ऑक्साइड की मोटाई जितनी पतली होगी, डिवाइस के माध्यम से सबथ्रेशोल्ड लीकेज करंट उतना ही अधिक होगा। नतीजतन, रिसाव वर्तमान को नियंत्रित करने के लिए 90-एनएम गेट-ऑक्साइड मोटाई के लिए डिजाइन विनिर्देश 1 एनएम पर सेट किया गया था।[5] इस तरह की टनलिंग को फाउलर-नॉर्डहाइम टनलिंग कहा जाता है।[6]

कहाँ;

और स्थिर हैं,

गेट ऑक्साइड के पार विद्युत क्षेत्र है।

डिज़ाइन सुविधाओं को 90 एनएम तक कम करने से पहले, ऑक्साइड की मोटाई बनाने के लिए एक दोहरे ऑक्साइड दृष्टिकोण इस समस्या का एक सामान्य समाधान था। 90 एनएम प्रक्रिया प्रौद्योगिकी के साथ, कुछ मामलों में ट्रिपल-ऑक्साइड दृष्टिकोण अपनाया गया है।[7] अधिकांश ट्रांजिस्टर के लिए एक मानक थिन ऑक्साइड का उपयोग किया जाता है, दूसरा I/O ड्राइवर सेल के लिए, और तीसरा मेमोरी-एंड-पास ट्रांजिस्टर सेल के लिए। ये अंतर विशुद्ध रूप से सीएमओएस प्रौद्योगिकियों के थ्रेशोल्ड वोल्टेज पर ऑक्साइड मोटाई की विशेषताओं पर आधारित हैं।

तापमान निर्भरता

जैसा कि थ्रेशोल्ड वोल्टेज को प्रभावित करने वाले ऑक्साइड की मोटाई के मामले में होता है, तापमान का CMOS डिवाइस के थ्रेशोल्ड वोल्टेज पर प्रभाव पड़ता है। MOSFET#बॉडी इफेक्ट सेक्शन में समीकरण के हिस्से का विस्तार

कहाँ;

आधी संपर्क क्षमता है,

बोल्ट्जमैन स्थिरांक है,

तापमान है,

प्राथमिक शुल्क है,

डोपिंग पैरामीटर है,

सब्सट्रेट के लिए आंतरिक डोपिंग पैरामीटर है।

हम देखते हैं कि सतह की क्षमता का तापमान के साथ सीधा संबंध है। ऊपर देखते हुए, कि दहलीज वोल्टेज का सीधा संबंध नहीं है, लेकिन यह प्रभावों से स्वतंत्र नहीं है। डोपिंग स्तर के आधार पर यह भिन्नता आमतौर पर -4 mV/K और -2 mV/K के बीच होती है।[8] 30 डिग्री सेल्सियस के परिवर्तन के लिए यह 90-एनएम प्रौद्योगिकी नोड के लिए आमतौर पर उपयोग किए जाने वाले 500 एमवी डिजाइन पैरामीटर से महत्वपूर्ण भिन्नता का परिणाम है।

रैंडम डोपेंट उतार-चढ़ाव पर निर्भरता

रैंडम डोपेंट फ्लक्चुएशन (RDF) प्रत्यारोपित अशुद्धता एकाग्रता में भिन्नता के परिणामस्वरूप होने वाली प्रक्रिया भिन्नता का एक रूप है। एमओएसएफईटी ट्रांजिस्टर में, चैनल क्षेत्र में आरडीएफ ट्रांजिस्टर के गुणों, विशेष रूप से थ्रेसहोल्ड वोल्टेज को बदल सकता है। नई प्रक्रिया प्रौद्योगिकियों में आरडीएफ का बड़ा प्रभाव होता है क्योंकि डोपेंट की कुल संख्या कम होती है।[9] डोपेंट के उतार-चढ़ाव को दबाने के लिए अनुसंधान कार्य किए जा रहे हैं, जिससे एक ही निर्माण प्रक्रिया से गुजरने वाले उपकरणों के बीच थ्रेशोल्ड वोल्टेज में बदलाव होता है।[10]

यह भी देखें

- MOSFET#संरचना और चैनल निर्माण

- चैनल लंबाई मॉडुलन

संदर्भ

- ↑ "जंक्शन क्षेत्र प्रभाव ट्रांजिस्टर (JFET)" (PDF). ETEE3212 Lecture Notes.

This is called the threshold, or pinch-off, voltage and occurs at vGS=VGS(OFF).

- ↑ Sedra, Adel S.; Smith, Kenneth C. "5.11 THE JUNCTION FIELD-EFFECT TRANSISTOR (JFET)" (PDF). माइक्रोइलेक्ट्रॉनिक सर्किट.

For JFETs the threshold voltage is called the pinch-off voltage and is denoted VP.

- ↑ Marco Delaurenti, PhD dissertation, Design and optimization techniques of high-speed VLSI circuits (1999)) Archived 2014-11-10 at the Wayback Machine

- ↑ NanoDotTek Report NDT14-08-2007, 12 August 2007

- ↑ Sugii, Watanabe and Sugatani. Transistor Design for 90-nm Generation and Beyond. (2002)

- ↑ S. M. Sze, Physics of Semiconductor Devices, Second Edition, New York: Wiley and Sons, 1981, pp. 496–504.

- ↑ Anil Telikepalli, Xilinx Inc, Power considerations in designing with 90 nm FPGAs (2005))[1]

- ↑ Weste and Eshraghian, Principles of CMOS VLSI Design : a systems perspective, Second Edition, (1993) pp.48 ISBN 0-201-53376-6

- ↑ Asenov, A. Huang,Random dopant induced threshold voltage lowering and fluctuations in sub-0.1 μm MOSFET's: A 3-D “atomistic” simulation study, Electron Devices, IEEE Transactions, 45, Issue: 12

- ↑ Asenov, A. Huang,Suppression of random dopant-induced threshold voltage fluctuations in sub-0.1-μm MOSFET's with epitaxial and δ-doped channels, Electron Devices, IEEE Transactions, 46, Issue: 8

बाहरी संबंध

- Online lecture on: Threshold Voltage and MOSFET Capacitances by Dr. Lundstrom