रिंग ऑसिलेटर: Difference between revisions

No edit summary |

No edit summary |

||

| (5 intermediate revisions by 3 users not shown) | |||

| Line 5: | Line 5: | ||

चूंकि इन्वर्टर अपने इनपुट के लॉजिकल नॉट की गणना करता है, यह दिखाया जा सकता है कि इनवर्टर की विषम संख्या की श्रृंखला का अंतिम आउटपुट पहले इनपुट का लॉजिकल नॉट है। पहले इनपुट पर जोर देने के बाद अंतिम आउटपुट को सीमित समय के लिए मुखर किया जाता है और इनपुट के अंतिम आउटपुट की प्रतिक्रिया दोलन का कारण बनती है। | चूंकि इन्वर्टर अपने इनपुट के लॉजिकल नॉट की गणना करता है, यह दिखाया जा सकता है कि इनवर्टर की विषम संख्या की श्रृंखला का अंतिम आउटपुट पहले इनपुट का लॉजिकल नॉट है। पहले इनपुट पर जोर देने के बाद अंतिम आउटपुट को सीमित समय के लिए मुखर किया जाता है और इनपुट के अंतिम आउटपुट की प्रतिक्रिया दोलन का कारण बनती है। | ||

इनवर्टर की सम संख्या से बनी गोलाकार श्रृंखला को रिंग ऑसिलेटर के रूप में उपयोग नहीं किया जा सकता है। इस | इनवर्टर की सम संख्या से बनी गोलाकार श्रृंखला को रिंग ऑसिलेटर के रूप में उपयोग नहीं किया जा सकता है। इस स्थिति में अंतिम आउटपुट इनपुट के समान है। चूँकि, इन्वर्टर फीडबैक के इस कॉन्फ़िगरेशन को स्टोरेज एलिमेंट के रूप में उपयोग किया जा सकता है और यह [[स्टेटिक रैंडम एक्सेस मेमोरी]] या एसरैम का बेसिक बिल्डिंग ब्लॉक है। | ||

रिंग ऑसिलेटर के चरण अधिकांश विभेदक चरण होते हैं, जो बाहरी गड़बड़ी के प्रति अधिक प्रतिरोधी होते हैं। यह नॉन-इनवर्टिंग स्टेज भी उपलब्ध कराता है। रिंग ऑसिलेटर को इनवर्टिंग और नॉन-इनवर्टिंग चरणों के मिश्रण से बनाया जा सकता है, परन्तु इनवर्टिंग चरणों की कुल संख्या विषम हो। ऑसिलेटर अवधि सभी स्थितियों में सभी चरणों की व्यक्तिगत देरी के योग के दोगुने के बराबर है। | रिंग ऑसिलेटर के चरण अधिकांश विभेदक चरण होते हैं, जो बाहरी गड़बड़ी के प्रति अधिक प्रतिरोधी होते हैं। यह नॉन-इनवर्टिंग स्टेज भी उपलब्ध कराता है। रिंग ऑसिलेटर को इनवर्टिंग और नॉन-इनवर्टिंग चरणों के मिश्रण से बनाया जा सकता है, परन्तु इनवर्टिंग चरणों की कुल संख्या विषम हो। ऑसिलेटर अवधि सभी स्थितियों में सभी चरणों की व्यक्तिगत देरी के योग के दोगुने के बराबर है। | ||

रिंग ऑसिलेटर को संचालित करने के लिए केवल शक्ति की आवश्यकता होती है। निश्चित वोल्टेज के ऊपर, सामान्यतः उपयोग किए जाने वाले MOSFETs के थ्रेसहोल्ड वोल्टेज के नीचे, दोलन अनायास प्रारंभ हो जाते हैं। दोलन की आवृत्ति बढ़ाने के लिए सामान्यतः दो विधियों का उपयोग किया जाता है। सबसे पहले, कम संख्या में इनवर्टर से रिंग बनाने से दोलन की उच्च आवृत्ति होती है, जिसमें लगभग समान विद्युत की खपत होती है। दूसरा, आपूर्ति वोल्टेज बढ़ाया जा सकता है। उन | रिंग ऑसिलेटर को संचालित करने के लिए केवल शक्ति की आवश्यकता होती है। निश्चित वोल्टेज के ऊपर, सामान्यतः उपयोग किए जाने वाले MOSFETs के थ्रेसहोल्ड वोल्टेज के नीचे, दोलन अनायास प्रारंभ हो जाते हैं। दोलन की आवृत्ति बढ़ाने के लिए सामान्यतः दो विधियों का उपयोग किया जाता है। सबसे पहले, कम संख्या में इनवर्टर से रिंग बनाने से दोलन की उच्च आवृत्ति होती है, जिसमें लगभग समान विद्युत की खपत होती है। दूसरा, आपूर्ति वोल्टेज बढ़ाया जा सकता है। उन परिपथों में जहां इस पद्धति को प्रायुक्त किया जा सकता है, यह चरणों की श्रृंखला के माध्यम से प्रसार विलंब को कम करता है, दोलन की आवृत्ति और उपभोग की गई धारा दोनों को बढ़ाता है। | ||

== ऑपरेशन == | == ऑपरेशन == | ||

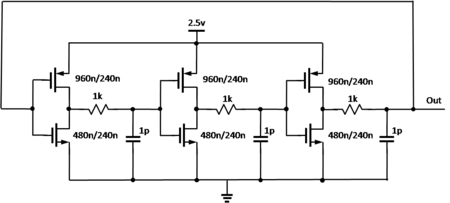

[[Image:Ring osc 5.png|thumb|right|450px|.25u CMOS प्रक्रिया में देरी के साथ तीन-चरण रिंग ऑसिलेटर का ट्रांजिस्टर स्तर योजनाबद्ध। इस विशेष | [[Image:Ring osc 5.png|thumb|right|450px|.25u CMOS प्रक्रिया में देरी के साथ तीन-चरण रिंग ऑसिलेटर का ट्रांजिस्टर स्तर योजनाबद्ध। इस विशेष परिपथ में इसकी गति के लिए उच्च विद्युत की खपत होती है, क्योंकि इनवर्टर विद्युत से जमीन तक बड़ा धारा चलाते हैं जब उनके इनपुट मध्यवर्ती वोल्टेज पर होते हैं। इन्वर्टर स्विच के साथ श्रृंखला में वर्तमान-सीमित उपकरणों वाला परिपथ अधिक ऊर्जा कुशल होता है।]]रिंग ऑसिलेटर के संचालन को समझने के लिए, पहले गेट विलंब को समझना चाहिए। भौतिक उपकरण में, कोई गेट तुरंत स्विच नहीं कर सकता हैं। उदाहरण के लिए, MOSFETs से निर्मित उपकरण में, स्रोत और अपवाह के बीच [[विद्युत प्रवाह]] प्रवाहित होने से पहले [[ गेट समाई |गेट संधारित्र]] को आवेशित किया जाना चाहिए। इस प्रकार, रिंग ऑसिलेटर में प्रत्येक इन्वर्टर का आउटपुट इनपुट बदलने के बाद सीमित समय के अन्दर बदल जाता है। यहाँ से, यह आसानी से देखा जा सकता है कि श्रृंखला में अधिक इनवर्टर जोड़ने से गेट की कुल देरी बढ़ जाती है, जिससे दोलन की आवृत्ति कम हो जाती है। | ||

रिंग ऑसिलेटर टाइम-डिले ऑसिलेटर्स के वर्ग का सदस्य है। समय-विलंब ऑसिलेटर में प्रवर्धक आउटपुट और इसके इनपुट के बीच विलंब तत्व के साथ प्रत्यावर्ती प्रवर्धक होता है। प्रवर्धक का अभीष्ट दोलन आवृत्ति पर 1 से अधिक लाभ होना चाहिए। प्रारंभिक | रिंग ऑसिलेटर टाइम-डिले ऑसिलेटर्स के वर्ग का सदस्य है। समय-विलंब ऑसिलेटर में प्रवर्धक आउटपुट और इसके इनपुट के बीच विलंब तत्व के साथ प्रत्यावर्ती प्रवर्धक होता है। प्रवर्धक का अभीष्ट दोलन आवृत्ति पर 1 से अधिक लाभ होना चाहिए। प्रारंभिक स्थिति पर विचार करें जहां एम्पलीफायर इनपुट और आउटपुट वोल्टेज स्थिर बिंदु पर क्षणिक रूप से संतुलित होते हैं। थोड़ी मात्रा में ध्वनि एम्पलीफायर आउटपुट को थोड़ा बढ़ा सकता है। समय-विलंब तत्व से निकलने के बाद, यह छोटा आउटपुट वोल्टेज परिवर्तन एम्पलीफायर इनपुट में प्रस्तुत किया जाएगा। एम्पलीफायर का ऋणात्मक लाभ 1 से अधिक है, इसलिए आउटपुट इस इनपुट वोल्टेज के विपरीत दिशा में बदल जाएगा। यह 1 से अधिक लाभ के लिए इनपुट मान से बड़ी राशि से बदल जाएगा। यह प्रवर्धित और व्युत्क्रम संकेत समय-देरी के माध्यम से आउटपुट से फैलता है और इनपुट पर वापस जाता है जहां इसे फिर से प्रवर्धित और व्युत्क्रम किया जाता है। इस अनुक्रमिक पाश का परिणाम एम्पलीफायर आउटपुट पर स्क्वायर-वेव सिग्नल होता है, जिसमें स्क्वायर वेव के प्रत्येक आधे की अवधि समय की देरी के बराबर होती है। स्क्वायर वेव तब तक बढ़ेगी जब तक एम्पलीफायर आउटपुट वोल्टेज अपनी सीमा तक नहीं पहुंच जाता, जहां यह स्थिर हो जाएगा। अधिक त्रुटिहीन विश्लेषण से पता चलेगा कि प्रारंभिक ध्वनि से बढ़ने वाली तरंग बढ़ने पर वर्गाकार नहीं हो सकती है, किन्तु यह वर्गाकार हो जाएगी क्योंकि एम्पलीफायर अपनी आउटपुट सीमा तक पहुंच जाता है। | ||

रिंग ऑसिलेटर समय-विलंब ऑसिलेटर का वितरित संस्करण है। रिंग ऑसिलेटर एक से अधिक (चूंकि, एक लूप में एक एकल इन्वर्टर स्थिर होता है और एक लूप में विषम संख्या या इनवर्टर के साथ एक रिंग ऑसिलेटर नहीं होता है) के लाभ के साथ एकल प्रवर्धक प्रवर्धक का प्रभाव देने के लिए इनवर्टर की विषम संख्या का उपयोग करता है। एकल विलंब तत्व होने के अतिरिक्त, प्रत्येक इन्वर्टर इनवर्टर के रिंग के चारों ओर सिग्नल की देरी में योगदान देता है, इसलिए नाम रिंग ऑसिलेटर है। रिंग में इनवर्टर के जोड़े जोड़ने से कुल विलंब बढ़ जाता है और इस प्रकार ऑसिलेटर की आवृत्ति कम हो जाती है। आपूर्ति वोल्टेज को बदलने से प्रत्येक इन्वर्टर के माध्यम से देरी में परिवर्तन होता है, उच्च वोल्टेज के साथ सामान्यतः देरी कम हो जाती है और ऑसिलेटर आवृत्ति बढ़ जाती है। व्रातिस्लाव सीएमओएस रिंग-ऑसिलेटर की आवृत्ति-स्थिरता और विद्युत की व्यय में सुधार के कुछ प्रणालियों का वर्णन करता है।<ref> Vratislav MICHAL. [http://www.postreh.com/vmichal/papers/Stability-CMOS-ring-oscillator.pdf "On the Low-power Design, Stability Improvement and Frequency Estimation of the CMOS Ring Oscillator"]. 2012.</ref> | |||

यदि t एकल इन्वर्टर के लिए समय की देरी का प्रतिनिधित्व करता है और n इन्वर्टर श्रृंखला में इनवर्टर की संख्या का प्रतिनिधित्व करता है, तो दोलन की आवृत्ति निम्न द्वारा दी जाती है: | यदि t एकल इन्वर्टर के लिए समय की देरी का प्रतिनिधित्व करता है और n इन्वर्टर श्रृंखला में इनवर्टर की संख्या का प्रतिनिधित्व करता है, तो दोलन की आवृत्ति निम्न द्वारा दी जाती है: | ||

| Line 22: | Line 24: | ||

== | == जिटर == | ||

रिंग ऑसिलेटर की अवधि यादृच्छिक तरीके से T+T' के रूप में भिन्न होती है जहां T' यादृच्छिक मान है। उच्च-गुणवत्ता वाले | रिंग ऑसिलेटर की अवधि यादृच्छिक तरीके से T+T' के रूप में भिन्न होती है जहां T' यादृच्छिक मान है। उच्च-गुणवत्ता वाले परिपथ में, औसत अवधि T की तुलना में T' की सीमा अपेक्षाकृत कम होती है। ऑसिलेटर अवधि में इस भिन्नता को जिटर कहा जाता है।<ref name="provablysecurerng">{{Cite web |url=http://cacr.uwaterloo.ca/~dstinson/papers/rng-IEEE.pdf |title=सक्रिय हमलों के लिए अंतर्निहित सहिष्णुता के साथ एक प्रमाणित रूप से सुरक्षित ट्रू रैंडम नंबर जेनरेटर|access-date=2012-05-12 |archive-date=2016-03-04 |archive-url=https://web.archive.org/web/20160304185717/http://cacr.uwaterloo.ca/~dstinson/papers/rng-IEEE.pdf |url-status=dead }}</ref> | ||

स्थानीय तापमान प्रभाव रिंग ऑसिलेटर की अवधि को लंबी अवधि की औसत अवधि के ऊपर और नीचे भटकने का कारण बनता है।<ref name="whirlygig"> | स्थानीय तापमान प्रभाव रिंग ऑसिलेटर की अवधि को लंबी अवधि की औसत अवधि के ऊपर और नीचे भटकने का कारण बनता है।<ref name="whirlygig"> | ||

Andy Green. [https://warmcat.com/2007/11/24/whirlygig-gpl'd-hwrng.html Whirlygig GPL Hardware RNG]. 2010</ref> | Andy Green. [https://warmcat.com/2007/11/24/whirlygig-gpl'd-hwrng.html Whirlygig GPL Hardware RNG]. 2010</ref> | ||

जब स्थानीय सिलिकॉन ठंडा होता है, तो प्रसार विलंब थोड़ा कम होता है, जिससे रिंग ऑसिलेटर थोड़ी अधिक आवृत्ति पर चलता है, जो अंततः स्थानीय तापमान को बढ़ाता है। जब स्थानीय सिलिकॉन गर्म होता है, तो प्रसार में देरी थोड़ी लंबी होती है, जिससे रिंग ऑसिलेटर थोड़ी कम आवृत्ति पर चलता है, जो अंततः स्थानीय तापमान को कम करता है। इसलिए, सिलिकॉन रिंग ऑसिलेटर की आवृत्ति | |||

जब स्थानीय सिलिकॉन ठंडा होता है, तो प्रसार विलंब थोड़ा कम होता है, जिससे रिंग ऑसिलेटर थोड़ी अधिक आवृत्ति पर चलता है, जो अंततः स्थानीय तापमान को बढ़ाता है। जब स्थानीय सिलिकॉन गर्म होता है, तो प्रसार में देरी थोड़ी लंबी होती है, जिससे रिंग ऑसिलेटर थोड़ी कम आवृत्ति पर चलता है, जो अंततः स्थानीय तापमान को कम करता है। इसलिए, सिलिकॉन रिंग ऑसिलेटर की आवृत्ति सामान्यतः स्थिर होगी, जब परिवेश का तापमान स्थिर होता है और उपकरण से परिवेश के वातावरण में गर्मी हस्तांतरण के कारक भिन्न नहीं होते हैं। | |||

== अनुप्रयोग == | == अनुप्रयोग == | ||

* | *अधिकांश [[ चरण बंद लूप |चरण बंद लूप]] में वोल्टेज-नियंत्रित ऑसिलेटर रिंग ऑसिलेटर से बनाया गया है।<ref> | ||

Takahito MIYAZAKI Masanori HASHIMOTO Hidetoshi ONODERA. | Takahito MIYAZAKI Masanori HASHIMOTO Hidetoshi ONODERA. | ||

[https://web.archive.org/web/20051015030950/http://ietele.oxfordjournals.org/cgi/content/abstract/E88-C/3/437 "A Performance Prediction of Clock Generation PLLs: A Ring Oscillator Based PLL and an LC Oscillator Based PLL"]{{dubious|date=January 2012}}<!-- maybe for clock generation, but PLLs are used elsewhere --> | [https://web.archive.org/web/20051015030950/http://ietele.oxfordjournals.org/cgi/content/abstract/E88-C/3/437 "A Performance Prediction of Clock Generation PLLs: A Ring Oscillator Based PLL and an LC Oscillator Based PLL"]{{dubious|date=January 2012}}<!-- maybe for clock generation, but PLLs are used elsewhere --> | ||

| Line 35: | Line 39: | ||

</ref> | </ref> | ||

* रिंग ऑसिलेटर्स का जिटर सामान्यतः [[हार्डवेयर यादृच्छिक संख्या जनरेटर]] में उपयोग किया जाता है।<ref name="provablysecurerng" /><ref name="whirlygig" /><ref>[http://www.cryptography.com/public/pdf/IntelRNG.pdf THE INTEL RANDOM NUMBER GENERATOR. CRYPTOGRAPHY RESEARCH, INC]</ref> | * रिंग ऑसिलेटर्स का जिटर सामान्यतः [[हार्डवेयर यादृच्छिक संख्या जनरेटर]] में उपयोग किया जाता है।<ref name="provablysecurerng" /><ref name="whirlygig" /><ref>[http://www.cryptography.com/public/pdf/IntelRNG.pdf THE INTEL RANDOM NUMBER GENERATOR. CRYPTOGRAPHY RESEARCH, INC]</ref> | ||

*रिंग ऑसिलेटर का उपयोग कभी-कभी नई हार्डवेयर | *रिंग ऑसिलेटर का उपयोग कभी-कभी नई हार्डवेयर विधि को प्रदर्शित करने के लिए किया जाता है, जिस तरह से [[हैलो वर्ल्ड प्रोग्राम]] का उपयोग अधिकांश नई सॉफ्टवेयर विधि को प्रदर्शित करने के लिए किया जाता है।<ref> | ||

[http://science.slashdot.org/article.pl?sid=06/03/24/015207 Slashdot Science: "IBM Creates Ring Oscillator on a Single Nanotube"] | [http://science.slashdot.org/article.pl?sid=06/03/24/015207 Slashdot Science: "IBM Creates Ring Oscillator on a Single Nanotube"] | ||

</ref><ref> | </ref><ref> | ||

[http://hardware.slashdot.org/article.pl?sid=06/03/20/223206 Slashdot Hardware: "World's First Completely Transparent IC"] | [http://hardware.slashdot.org/article.pl?sid=06/03/20/223206 Slashdot Hardware: "World's First Completely Transparent IC"] | ||

</ref> | </ref> | ||

*कई [[वेफर (इलेक्ट्रॉनिक्स)]] में स्क्राइब लाइन परीक्षण संरचनाओं के | *कई [[वेफर (इलेक्ट्रॉनिक्स)]] में स्क्राइब लाइन परीक्षण संरचनाओं के भाग के रूप में रिंग ऑसिलेटर सम्मिलित है। निर्माण प्रक्रिया विविधताओं के प्रभावों को मापने के लिए [[वेफर परीक्षण]] के सम्मिलित उनका उपयोग किया जाता है।<ref>[http://cat.inist.fr/?aModele=afficheN&cpsidt=17502322 "Ring oscillators for CMOS process tuning and variability control"] {{Webarchive|url=https://web.archive.org/web/20120603174909/http://cat.inist.fr/?aModele=afficheN&cpsidt=17502322 |date=2012-06-03 }} | ||

by BHUSHAN Manjul; GATTIKER Anne; KETCHEN Mark B.; DAS Koushik K.</ref> | by BHUSHAN Manjul; GATTIKER Anne; KETCHEN Mark B.; DAS Koushik K.</ref> | ||

* चिप पर वोल्टेज और तापमान के प्रभाव को मापने के लिए रिंग ऑसिलेटर्स का भी उपयोग किया जा सकता है।<ref> | * चिप पर वोल्टेज और तापमान के प्रभाव को मापने के लिए रिंग ऑसिलेटर्स का भी उपयोग किया जा सकता है।<ref> | ||

| Line 55: | Line 59: | ||

{{commons category|Ring oscillators}} | {{commons category|Ring oscillators}} | ||

{{Reflist}}<!--added above categories/infobox footers by script-assisted edit--> | {{Reflist}}<!--added above categories/infobox footers by script-assisted edit--> | ||

[Category:Electronic oscillato | |||

[[Category: | [[Category:All accuracy disputes]] | ||

[[Category:Articles with disputed statements from January 2012]] | |||

[[Category:Articles with invalid date parameter in template]] | |||

[[Category:Commons category link is locally defined]] | |||

[[Category:Created On 12/06/2023]] | [[Category:Created On 12/06/2023]] | ||

[[Category:Machine Translated Page]] | |||

[[Category:Pages with script errors]] | |||

[[Category:Templates Vigyan Ready]] | |||

[[Category:Webarchive template wayback links]] | |||

[[Category:इलेक्ट्रॉनिक ऑसिलेटर]] | |||

[[Category:डिजिटल सर्किट]] | |||

Latest revision as of 11:37, 30 June 2023

रिंग ऑसिलेटर एक रिंग में विषम संख्या में इन्वर्टर (लॉजिक गेट) से बना उपकरण है, जिसका आउटपुट दो वोल्टेज स्तरों के बीच दोलन करता है, जो 'सही' और 'गलत' का प्रतिनिधित्व करता है। नॉट गेट्स, या इनवर्टर, एक श्रृंखला में जुड़े होते हैं और अंतिम इन्वर्टर का आउटपुट वापस पहले में फीड किया जाता है।

विवरण

चूंकि इन्वर्टर अपने इनपुट के लॉजिकल नॉट की गणना करता है, यह दिखाया जा सकता है कि इनवर्टर की विषम संख्या की श्रृंखला का अंतिम आउटपुट पहले इनपुट का लॉजिकल नॉट है। पहले इनपुट पर जोर देने के बाद अंतिम आउटपुट को सीमित समय के लिए मुखर किया जाता है और इनपुट के अंतिम आउटपुट की प्रतिक्रिया दोलन का कारण बनती है।

इनवर्टर की सम संख्या से बनी गोलाकार श्रृंखला को रिंग ऑसिलेटर के रूप में उपयोग नहीं किया जा सकता है। इस स्थिति में अंतिम आउटपुट इनपुट के समान है। चूँकि, इन्वर्टर फीडबैक के इस कॉन्फ़िगरेशन को स्टोरेज एलिमेंट के रूप में उपयोग किया जा सकता है और यह स्टेटिक रैंडम एक्सेस मेमोरी या एसरैम का बेसिक बिल्डिंग ब्लॉक है।

रिंग ऑसिलेटर के चरण अधिकांश विभेदक चरण होते हैं, जो बाहरी गड़बड़ी के प्रति अधिक प्रतिरोधी होते हैं। यह नॉन-इनवर्टिंग स्टेज भी उपलब्ध कराता है। रिंग ऑसिलेटर को इनवर्टिंग और नॉन-इनवर्टिंग चरणों के मिश्रण से बनाया जा सकता है, परन्तु इनवर्टिंग चरणों की कुल संख्या विषम हो। ऑसिलेटर अवधि सभी स्थितियों में सभी चरणों की व्यक्तिगत देरी के योग के दोगुने के बराबर है।

रिंग ऑसिलेटर को संचालित करने के लिए केवल शक्ति की आवश्यकता होती है। निश्चित वोल्टेज के ऊपर, सामान्यतः उपयोग किए जाने वाले MOSFETs के थ्रेसहोल्ड वोल्टेज के नीचे, दोलन अनायास प्रारंभ हो जाते हैं। दोलन की आवृत्ति बढ़ाने के लिए सामान्यतः दो विधियों का उपयोग किया जाता है। सबसे पहले, कम संख्या में इनवर्टर से रिंग बनाने से दोलन की उच्च आवृत्ति होती है, जिसमें लगभग समान विद्युत की खपत होती है। दूसरा, आपूर्ति वोल्टेज बढ़ाया जा सकता है। उन परिपथों में जहां इस पद्धति को प्रायुक्त किया जा सकता है, यह चरणों की श्रृंखला के माध्यम से प्रसार विलंब को कम करता है, दोलन की आवृत्ति और उपभोग की गई धारा दोनों को बढ़ाता है।

ऑपरेशन

रिंग ऑसिलेटर के संचालन को समझने के लिए, पहले गेट विलंब को समझना चाहिए। भौतिक उपकरण में, कोई गेट तुरंत स्विच नहीं कर सकता हैं। उदाहरण के लिए, MOSFETs से निर्मित उपकरण में, स्रोत और अपवाह के बीच विद्युत प्रवाह प्रवाहित होने से पहले गेट संधारित्र को आवेशित किया जाना चाहिए। इस प्रकार, रिंग ऑसिलेटर में प्रत्येक इन्वर्टर का आउटपुट इनपुट बदलने के बाद सीमित समय के अन्दर बदल जाता है। यहाँ से, यह आसानी से देखा जा सकता है कि श्रृंखला में अधिक इनवर्टर जोड़ने से गेट की कुल देरी बढ़ जाती है, जिससे दोलन की आवृत्ति कम हो जाती है।

रिंग ऑसिलेटर टाइम-डिले ऑसिलेटर्स के वर्ग का सदस्य है। समय-विलंब ऑसिलेटर में प्रवर्धक आउटपुट और इसके इनपुट के बीच विलंब तत्व के साथ प्रत्यावर्ती प्रवर्धक होता है। प्रवर्धक का अभीष्ट दोलन आवृत्ति पर 1 से अधिक लाभ होना चाहिए। प्रारंभिक स्थिति पर विचार करें जहां एम्पलीफायर इनपुट और आउटपुट वोल्टेज स्थिर बिंदु पर क्षणिक रूप से संतुलित होते हैं। थोड़ी मात्रा में ध्वनि एम्पलीफायर आउटपुट को थोड़ा बढ़ा सकता है। समय-विलंब तत्व से निकलने के बाद, यह छोटा आउटपुट वोल्टेज परिवर्तन एम्पलीफायर इनपुट में प्रस्तुत किया जाएगा। एम्पलीफायर का ऋणात्मक लाभ 1 से अधिक है, इसलिए आउटपुट इस इनपुट वोल्टेज के विपरीत दिशा में बदल जाएगा। यह 1 से अधिक लाभ के लिए इनपुट मान से बड़ी राशि से बदल जाएगा। यह प्रवर्धित और व्युत्क्रम संकेत समय-देरी के माध्यम से आउटपुट से फैलता है और इनपुट पर वापस जाता है जहां इसे फिर से प्रवर्धित और व्युत्क्रम किया जाता है। इस अनुक्रमिक पाश का परिणाम एम्पलीफायर आउटपुट पर स्क्वायर-वेव सिग्नल होता है, जिसमें स्क्वायर वेव के प्रत्येक आधे की अवधि समय की देरी के बराबर होती है। स्क्वायर वेव तब तक बढ़ेगी जब तक एम्पलीफायर आउटपुट वोल्टेज अपनी सीमा तक नहीं पहुंच जाता, जहां यह स्थिर हो जाएगा। अधिक त्रुटिहीन विश्लेषण से पता चलेगा कि प्रारंभिक ध्वनि से बढ़ने वाली तरंग बढ़ने पर वर्गाकार नहीं हो सकती है, किन्तु यह वर्गाकार हो जाएगी क्योंकि एम्पलीफायर अपनी आउटपुट सीमा तक पहुंच जाता है।

रिंग ऑसिलेटर समय-विलंब ऑसिलेटर का वितरित संस्करण है। रिंग ऑसिलेटर एक से अधिक (चूंकि, एक लूप में एक एकल इन्वर्टर स्थिर होता है और एक लूप में विषम संख्या या इनवर्टर के साथ एक रिंग ऑसिलेटर नहीं होता है) के लाभ के साथ एकल प्रवर्धक प्रवर्धक का प्रभाव देने के लिए इनवर्टर की विषम संख्या का उपयोग करता है। एकल विलंब तत्व होने के अतिरिक्त, प्रत्येक इन्वर्टर इनवर्टर के रिंग के चारों ओर सिग्नल की देरी में योगदान देता है, इसलिए नाम रिंग ऑसिलेटर है। रिंग में इनवर्टर के जोड़े जोड़ने से कुल विलंब बढ़ जाता है और इस प्रकार ऑसिलेटर की आवृत्ति कम हो जाती है। आपूर्ति वोल्टेज को बदलने से प्रत्येक इन्वर्टर के माध्यम से देरी में परिवर्तन होता है, उच्च वोल्टेज के साथ सामान्यतः देरी कम हो जाती है और ऑसिलेटर आवृत्ति बढ़ जाती है। व्रातिस्लाव सीएमओएस रिंग-ऑसिलेटर की आवृत्ति-स्थिरता और विद्युत की व्यय में सुधार के कुछ प्रणालियों का वर्णन करता है।[1]

यदि t एकल इन्वर्टर के लिए समय की देरी का प्रतिनिधित्व करता है और n इन्वर्टर श्रृंखला में इनवर्टर की संख्या का प्रतिनिधित्व करता है, तो दोलन की आवृत्ति निम्न द्वारा दी जाती है:

- .[2]

जिटर

रिंग ऑसिलेटर की अवधि यादृच्छिक तरीके से T+T' के रूप में भिन्न होती है जहां T' यादृच्छिक मान है। उच्च-गुणवत्ता वाले परिपथ में, औसत अवधि T की तुलना में T' की सीमा अपेक्षाकृत कम होती है। ऑसिलेटर अवधि में इस भिन्नता को जिटर कहा जाता है।[3]

स्थानीय तापमान प्रभाव रिंग ऑसिलेटर की अवधि को लंबी अवधि की औसत अवधि के ऊपर और नीचे भटकने का कारण बनता है।[4]

जब स्थानीय सिलिकॉन ठंडा होता है, तो प्रसार विलंब थोड़ा कम होता है, जिससे रिंग ऑसिलेटर थोड़ी अधिक आवृत्ति पर चलता है, जो अंततः स्थानीय तापमान को बढ़ाता है। जब स्थानीय सिलिकॉन गर्म होता है, तो प्रसार में देरी थोड़ी लंबी होती है, जिससे रिंग ऑसिलेटर थोड़ी कम आवृत्ति पर चलता है, जो अंततः स्थानीय तापमान को कम करता है। इसलिए, सिलिकॉन रिंग ऑसिलेटर की आवृत्ति सामान्यतः स्थिर होगी, जब परिवेश का तापमान स्थिर होता है और उपकरण से परिवेश के वातावरण में गर्मी हस्तांतरण के कारक भिन्न नहीं होते हैं।

अनुप्रयोग

- अधिकांश चरण बंद लूप में वोल्टेज-नियंत्रित ऑसिलेटर रिंग ऑसिलेटर से बनाया गया है।[5]

- रिंग ऑसिलेटर्स का जिटर सामान्यतः हार्डवेयर यादृच्छिक संख्या जनरेटर में उपयोग किया जाता है।[3][4][6]

- रिंग ऑसिलेटर का उपयोग कभी-कभी नई हार्डवेयर विधि को प्रदर्शित करने के लिए किया जाता है, जिस तरह से हैलो वर्ल्ड प्रोग्राम का उपयोग अधिकांश नई सॉफ्टवेयर विधि को प्रदर्शित करने के लिए किया जाता है।[7][8]

- कई वेफर (इलेक्ट्रॉनिक्स) में स्क्राइब लाइन परीक्षण संरचनाओं के भाग के रूप में रिंग ऑसिलेटर सम्मिलित है। निर्माण प्रक्रिया विविधताओं के प्रभावों को मापने के लिए वेफर परीक्षण के सम्मिलित उनका उपयोग किया जाता है।[9]

- चिप पर वोल्टेज और तापमान के प्रभाव को मापने के लिए रिंग ऑसिलेटर्स का भी उपयोग किया जा सकता है।[10]

यह भी देखें

टिप्पणियाँ

- ↑ Vratislav MICHAL. "On the Low-power Design, Stability Improvement and Frequency Estimation of the CMOS Ring Oscillator". 2012.

- ↑ Mandal, M.K. & Sarkar, B.C."Ring oscillators: Characteristics and applications"

- ↑ 3.0 3.1 "सक्रिय हमलों के लिए अंतर्निहित सहिष्णुता के साथ एक प्रमाणित रूप से सुरक्षित ट्रू रैंडम नंबर जेनरेटर" (PDF). Archived from the original (PDF) on 2016-03-04. Retrieved 2012-05-12.

- ↑ 4.0 4.1 Andy Green. Whirlygig GPL Hardware RNG. 2010

- ↑ Takahito MIYAZAKI Masanori HASHIMOTO Hidetoshi ONODERA. "A Performance Prediction of Clock Generation PLLs: A Ring Oscillator Based PLL and an LC Oscillator Based PLL"[dubious ] [1]

- ↑ THE INTEL RANDOM NUMBER GENERATOR. CRYPTOGRAPHY RESEARCH, INC

- ↑ Slashdot Science: "IBM Creates Ring Oscillator on a Single Nanotube"

- ↑ Slashdot Hardware: "World's First Completely Transparent IC"

- ↑ "Ring oscillators for CMOS process tuning and variability control" Archived 2012-06-03 at the Wayback Machine by BHUSHAN Manjul; GATTIKER Anne; KETCHEN Mark B.; DAS Koushik K.

- ↑ "Analysis of a ring oscillator based on-chip thermal sensor" Archived 2014-03-28 at the Wayback Machine

[Category:Electronic oscillato