चार्ज-पंप फेज-लॉक लूप: Difference between revisions

No edit summary |

m (added Category:Vigyan Ready using HotCat) |

||

| Line 134: | Line 134: | ||

[[Category: Machine Translated Page]] | [[Category: Machine Translated Page]] | ||

[[Category:Created On 19/06/2023]] | [[Category:Created On 19/06/2023]] | ||

[[Category:Vigyan Ready]] | |||

Revision as of 16:21, 7 July 2023

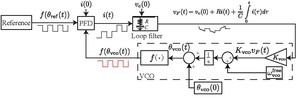

चार्ज-पंप चरण -लॉक लूप (सीपी-पीएलएल) चरण-आवृत्ति डिटेक्टर और वर्गाकार तरंग संकेतों के साथ चरण-लॉक लूप का एक संशोधन है।[1] सीपी-पीएलएल आने वाले संकेतों के चरण को त्वरित रूप से लॉक करने की अनुमति देता है, जिससे कम स्थिर अवस्था चरण त्रुटि प्राप्त होती है।[2]

चरण-आवृत्ति डिटेक्टर (पीएफडी)

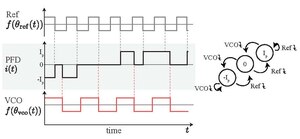

चरण-आवृत्ति डिटेक्टर (पीएफडी) को संदर्भ (रेफ) और नियंत्रित (वीसीओ) संकेतों के पिछला किनारों द्वारा रोका गया है। पीएफडी का आउटपुट संकेत में केवल तीन अवस्थाएँ हो सकती हैं: 0, , और . संदर्भ संकेत का पिछला किनारा पीएफडी को उच्च अवस्था में स्विच करने के लिए मजबूर करता है, जब तक कि वह पहले से ही इस अवस्था में न हो .वीसीओ संकेत का पिछला किनारा पीएफडी को निचले अवस्था में जाने के लिए मजबूर करता है, जब तक कि वह पहले से ही इस अवस्था में न हो .यदि दोनों पिछला किनारे एक ही समय में होते हैं, तो पीएफडी शून्य पर स्विच हो जाता है।

सीपी-पीएलएल के गणितीय मॉडल

दूसरे क्रम के सीपी-पीएलएल के पहला रैखिक गणितीय मॉडल 1980 में एफ. गार्डनर द्वारा सुझाव दिया गया था। [2] 1994 में एम. वैन पैमेल द्वारा वीसीओ अधिभार के बिना एक अरैखिक मॉडल का सुझाव दिया गया था [3] और फिर एन. कुज़नेत्सोव एट अल द्वारा परिष्कृत किया गया था। 2019 में।[4] वीसीओ अधिभार को ध्यान में रखते हुए सीपी-पीएलएल का बंद रूप गणितीय मॉडल प्राप्त किया गया है।[5]

सीपी-पीएलएल के ये गणितीय मॉडल होल्ड-इन रेंज (इनपुट संकेत अवधि की अधिकतम सीमा जैसे कि वहाँ एक बंद अवस्था मौजूद है जिस पर वीसीओ अतिभारित नहीं है) और पुल-इन रेंज (ए) के विश्लेषणात्मक अनुमान प्राप्त करने की अनुमति देते हैं। होल्ड-इन रेंज के भीतर इनपुट संकेत अवधि की अधिकतम सीमा, जैसे कि किसी भी प्रारंभिक स्थिति के लिए सीपी-पीएलएल लॉक स्थिति प्राप्त कर लेता है)।[6]

दूसरे क्रम सीपी-पीएलएल और गार्डनर के अनुमान का निरंतर समय रैखिक मॉडल

गार्डनर का विश्लेषण निम्नलिखित समीपता पर आधारित है[2] समय अंतराल जिस पर संदर्भ संकेत की प्रत्येक अवधि पर पीएफडी की गैर-शून्य स्थिति होती है

फिर चार्ज-पंप पीएफडी का औसत आउटपुट है

संगत स्थानांतरण कार्य के साथ

फ़िल्टर ट्रांसफर फ़ंक्शन का उपयोग करना और वीसीओ स्थानांतरण समारोह एक को दूसरे क्रम के सीपी-पीएलएल का गार्डनर का रैखिक अनुमानित औसत मॉडल मिलता है

1980 में, एम. गार्डनर ने उपरोक्त तर्क के आधार पर अनुमान लगाया कि व्यावहारिक चार्ज-पंप पीएलएल की क्षणिक प्रतिक्रिया समकक्ष शास्त्रीय पीएलएल की प्रतिक्रिया के लगभग समान होने की उम्मीद की जा सकती है।[2]1856 (सीपी-पीएलएल पर गार्डनर का अनुमान [7]) गार्डनर के परिणामों के बाद, टाइप 2 एपीएलएल की पुल-इन रेंज पर ईगन अनुमान के अनुरूप, अम्र एम. फहीम ने अपने पुस्तक में अनुमान लगाया[8] : 6 कि एक अनंत पुल-इन (कैप्चर) रेंज रखने के लिए, सीपी-पीएलएल में लूप फ़िल्टर के लिए सक्रिय फ़िल्टर का उपयोग किया जाना चाहिए ( टाइप II सीपी-पीएलएल के पुल-इन रेंज पर फहीम-ईगन का अनुमान)।

दूसरे क्रम के सीपी-पीएलएल का निरंतर समय अरैखिक मॉडल

व्यापकता के नुकसान के बिना यह माना जाता है कि वीसीओ और रेफ संकेतों के पिछला किनारे होते हैं जब संबंधित चरण पूर्णांक संख्या तक पहुँचता है। मान लीजिए कि रेफ संकेत के पहले पिछला किनारे का समय उदाहरण को इस रूप में परिभाषित किया गया है .पीएफडी अवस्था पीएफडी प्रारंभिक अवस्था द्वारा निर्धारित किया जाता है ,वीसीओ के प्रारंभिक चरण में बदलाव और रेफरी संकेत।

इनपुट करंट के बीच संबंध और आउटपुट वोल्टेज के लिए प्रतिरोधी और संधारित्र के आधार पर आनुपातिक रूप से एकीकृत (परिपूर्ण पीआई) फ़िल्टर के लिए इस प्रकार है

कहाँ प्रतिरोध है, धारिता है, और संधारित्र आवेश है। नियंत्रण संकेत वीसीओ आवृत्ति समायोजित करता है

कहाँ वीसीओ फ्री-रनिंग (शांत) आवृत्ति है (अर्थात ) के लिए, वीसीओ लाभ (संवेदनशीलता) है, और वीसीओ चरण है। अंत में, सीपी-पीएलएल का निरंतर समय अरेखीय गणितीय मॉडल इस प्रकार है

निम्नलिखित असंतत टुकड़ा-वार निरंतर रैखिकता के साथ

और प्रारंभिक शर्तें . यह मॉडल अरैखिक, गैर-स्वायत्त, असंतुलित, स्विचिंग प्रणाली है।

दूसरे क्रम के सीपी-पीएलएल का असतत समय अरेखीय मॉडल

संदर्भ संकेत आवृत्ति को स्थिर मानी जाती है:

जहाँ , और संदर्भ संकेत की एक अवधि, आवृत्ति और एक चरण है। होने देना . द्वारा निरूपित करें समय का पहला क्षण ऐसा है कि पीएफडी आउटपुट शून्य हो जाता है (यदि , तब ) और तक वीसीओ या Ref का पहला पिछला किनारा। आगे तदनुरूप बढ़ते क्रम और के लिए परिभाषित किया गया हैं। होने देना . तब के लिए एक गैर-शून्य स्थिरांक है (). द्वारा निरूपित करें पीएफडी पल्स चौड़ाई (समय अंतराल की लंबाई, जहां पीएफडी आउटपुट गैर-शून्य स्थिरांक है), पीएफडी आउटपुट के संकेत से गुणा किया जाता है अर्थात। के लिए और के लिए यदि वीसीओ ट्रेलिंग एज Ref ट्रेलिंग एज से पहले हिट करता है,तब और विपरीत अवस्था में हमारे पास है , अर्थात। दिखाता है कि कैसे एक संकेत दूसरे से पिछड़ जाता है। पीएफडी का शून्य उत्पादन अंतराल पर : के लिए . चर का परिवर्तन[9] को पैरामीटर की संख्या को दो तक कम करने की अनुमति देता है: यहाँ सामान्यीकृत चरण बदलाव है और वीसीओ आवृत्ति का अनुपात है संदर्भ आवृत्ति के लिए .अंत में, वीसीओ अधिभार के बिना दूसरे क्रम सीपी-पीएलएल का असतत-समय मॉडल[4][6]

कहाँ

इस असतत-समय मॉडल की एकमात्र स्थिर अवस्था है और होल्ड-इन और पुल-इन रेंज का अनुमान लगाने की अनुमति देता है।[6]

यदि वीसीओ अतिभारित है, अर्थात शून्य है, या समान है:

या

, फिर सीपी-पीएलएल गतिशीलता के अतिरिक्त मामलों को ध्यान में रखा जाना है।[5] किसी भी पैरामीटर के लिए वीसीओ अधिभार वीसीओ और संदर्भ संकेतों के बीच पर्याप्त रूप से बड़े आवृत्ति अंतर के लिए हो सकता है।व्यवहार में वीसीओ अधिभार से बचना चाहिए।

उच्च-क्रम सीपी-पीएलएल के अरैखिक मॉडल

उच्च-क्रम सीपी-पीएलएल के गैर-रैखिक गणितीय मॉडल की व्युत्पत्ति पारलौकिक चरण समीकरणों की ओर ले जाती है जिन्हें विश्लेषणात्मक रूप से हल नहीं किया जा सकता है और शास्त्रीय निश्चित-बिंदु विधि या न्यूटन-रैपसन दृष्टिकोण जैसे संख्यात्मक दृष्टिकोण की आवश्यकता होती है।[10]

संदर्भ

- ↑ USA US3714463A, Jon M. Laune, "Digital frequency and/or phase detector charge pump", published 1973-01-30

- ↑ 2.0 2.1 2.2 2.3 F. Gardner (1980). "चार्ज-पंप चरण-लॉक लूप". IEEE Transactions on Communications. 28 (11): 1849–1858. Bibcode:1980ITCom..28.1849G. doi:10.1109/TCOM.1980.1094619.

- ↑ M. van Paemel (1994). "Analysis of a charge-pump pll: A new model". IEEE Transactions on Communications. 42 (7): 2490–2498. doi:10.1109/26.297861.

- ↑ 4.0 4.1 N. Kuznetsov, M. Yuldashev, R. Yuldashev, M. Blagov, E. Kudryashova, O. Kuznetsova, and T. Mokaev (2019). "Comments on van Paemel's mathematical model of charge-pump phase-locked loop" (PDF). Differential Equations and Control Processes. 1: 109–120.

{{cite journal}}: CS1 maint: multiple names: authors list (link) - ↑ 5.0 5.1 N. Kuznetsov, M. Yuldashev, R. Yuldashev, M. Blagov, E. Kudryashova, O. Kuznetsova, T. Mokaev (2020). "Charge pump phase-locked loop with phase-frequency detector: closed form mathematical model". 1901 (1468). arXiv:1901.01468.

{{cite journal}}: Cite journal requires|journal=(help)CS1 maint: multiple names: authors list (link) - ↑ 6.0 6.1 6.2 N.V. Kuznetsov, A.S. Matveev, M.V. Yuldashev, R.V. Yuldashev (2020). "Nonlinear analysis of charge-pump phase-locked loop: the hold-in and pull-in ranges". IFAC World Congress. arXiv:2005.00864.

{{cite journal}}: CS1 maint: multiple names: authors list (link) - ↑ Kuznetsov, N.V.; Matveev, A.S.; Yuldashev, M.V.; Yuldashev, R.V. (2021). "Nonlinear Analysis of Charge-Pump Phase-Locked Loop: The Hold-In and Pull-In Ranges". IEEE Transactions on Circuits and Systems I: Regular Papers. 68 (10): 4049–4061. doi:10.1109/TCSI.2021.3101529.

- ↑ Fahim, Amr M. (2005). Clock Generators for SOC Processors: Circuits and Architecture. Boston-Dordrecht-London: Kluwer Academic Publishers.

- ↑ P. Curran, C. Bi, and O. Feely (2013). "चार्ज-पंप चरण-लॉक लूप की गतिशीलता". International Journal of Circuit Theory and Applications. 41 (11): 1109–1135. doi:10.1002/cta.1814. S2CID 3792988.

{{cite journal}}: CS1 maint: multiple names: authors list (link) - ↑ C. Hedayat, A. Hachem, Y. Leduc, and G. Benbassat (1999). "Modeling and characterization of the 3rd order charge-pump PLL: a fully event-driven approach". Analog Integrated Circuits and Signal Processing. 19 (1): 25–45. doi:10.1023/A:1008326315191. S2CID 58204942.

{{cite journal}}: CS1 maint: multiple names: authors list (link)