एनईसी V20: Difference between revisions

(Created page with "{{Short description|16-bit microprocessor introduced by NEC in 1984}} {{use dmy dates|date=January 2022|cs1-dates=y}} {{use list-defined references|date=January 2022}} {{Infob...") |

No edit summary |

||

| (11 intermediate revisions by 3 users not shown) | |||

| Line 3: | Line 3: | ||

{{use list-defined references|date=January 2022}} | {{use list-defined references|date=January 2022}} | ||

{{Infobox CPU | {{Infobox CPU | ||

| name = | | name = एनईसी वी20 (μPD70108) | ||

| image = KL NEC V20.jpg | | image = KL NEC V20.jpg | ||

| alt = | | alt = | ||

| caption = 8 MHz V20 in plastic DIP package | | caption = 8 MHz V20 in plastic DIP package | ||

<!----------------- General Info -----------------> | <!----------------- General Info -----------------> | ||

| produced-start = {{ | | produced-start = {{प्रारंभ तिथि और आयु|1984|03}}<ref name="x86guide-v20-5"/> | ||

| produced-end = <!-- {{End date and age|19yy|mm}} --> | | produced-end = <!-- {{End date and age|19yy|mm}} --> | ||

| soldby = | | soldby = | ||

| designfirm = | | designfirm = | ||

| manuf1 = [[ | | manuf1 = [[एनईसी]] (μPD70108) | ||

| manuf2 = [[ | | manuf2 = [[शार्प कॉर्पोरेशन|शार्प]] (एलएच70108) | ||

| manuf3 = [[ | | manuf3 = [[सोनी]] (CXQ70108) | ||

| manuf4 = [[ | | manuf4 = [[ज़िलॉग]] (Z70108) | ||

| cpuid = | | cpuid = | ||

| code = | | code = | ||

| Line 31: | Line 31: | ||

| dmi-slow-unit = | | dmi-slow-unit = | ||

| dmi-fast-unit = | | dmi-fast-unit = | ||

| data-width = [[16- | | data-width = [[16-बिट कंप्यूटिंग|16 बिट्स]] | ||

| address-width = | | address-width = | ||

| virtual-width = | | virtual-width = | ||

| Line 58: | Line 58: | ||

<!------------------ History -------------------> | <!------------------ History -------------------> | ||

| predecessor = | | predecessor = | ||

| successor = [[ | | successor = [[एनईसी वी60]] | ||

}} | }} | ||

'''एनईसी V20''' एक [[माइक्रोप्रोसेसर]] है जिसे एनईसी द्वारा डिजाइन और निर्मित किया गया था। यह [[इंटेल 8088]] के साथ पिन अनुकूल और ऑब्जेक्ट कोड दोनों अनुकूल है, कुछ एक्सटेंशन के साथ [[इंटेल 80188]] के समान एक निर्देश सेट आर्किटेक्चर (आईएसए) के साथ।<ref name="cpu-world"/> वी20 को मार्च 1984 में प्रस्तुत किया गया था।<ref name="x86guide-v20-5"/><ref name="cpu-world"/> | |||

== सुविधाएँ == | == सुविधाएँ == | ||

V20 के | V20 के पासे में 63,000 [[ट्रांजिस्टर]] सम्मिलित थे; 8088 सीपीयू के 29,000 से दोगुने से भी अधिक।<ref name="x86guide-v20-5"/> चिप को 8088 द्वारा प्रयुक्त 33% ड्यूटी चक्र की तुलना में 50% के क्लॉक ड्यूटी चक्र के लिए डिज़ाइन किया गया था।<ref name="pcm-dec1985"/> V20 में दो, 16-बिट विस्तृत आंतरिक डेटाबेस हैं, जो दो डेटा स्थानांतरण को एक साथ करने की अनुमति देते हैं।<ref name="ieeem-nov2021"/> इस तरह के अंतरों का मतलब है कि एक V20 सामान्यतः एक ही आवृत्ति पर चलने वाले इंटेल 8088 की तुलना में एक निश्चित समय में अधिक निर्देश पूरा कर सकता है।<ref name="cpu-world"/> | ||

V20 को 2-माइक्रोन | V20 को 2-माइक्रोन सीमॉस प्रौद्योगिकी में निर्मित किया गया था।<ref name="shmj"/><ref name="pcm-dec1985"/> प्रारंभिक संस्करण 5, 8, और 10 मेगाहर्ट्ज की गति पर चलते थे।<ref name="chipdb"/> 1990 में, निर्माण प्रक्रिया प्रौद्योगिकी के उन्नयन के परिणामस्वरूप बेहतर प्रदर्शन और कम बिजली की खपत के साथ V20H और V20HL का निर्माण हुआ।<ref name="shmj"/> बाद के संस्करणों में 12 और 16 मेगाहर्ट्ज की गति जोड़ी गयी। V20HL भी पूरी तरह से स्थिर थे, जिससे उनकी क्लॉक रुक गई थी। | ||

V20 को [[16-बिट कंप्यूटिंग | V20 को आंतरिक रूप से [[16-बिट कंप्यूटिंग|16-बिट]] वाइड बताया गया था। इसमें एक 8-बिट बाहरी डेटा बस का उपयोग किया गया था जिसे एड्रेस बस के लो बाइट के समान पिन पर मल्टीप्लेक्स किया गया था। इसकी 20-बिट वाइड एड्रेस बस 1 एमबी मेमोरी को संबोधित करने में सक्षम थी। | ||

V20 | बताया गया कि V20 इंटेल 8087 [[फ्लोटिंग-पॉइंट यूनिट]] (एफपीयू) कोप्रोसेसर के साथ अनुकूल था।<ref name="tpc-v20"/> एनईसी ने अपना स्वयं का एफपीयू, μPD72091 भी डिज़ाइन किया था, जिसे उत्पादन तक पहुंचने से पहले रद्द कर दिया गया था। उन्होंने एक संशोधित डिज़ाइन, μPD72191 के साथ इसका अनुसरण किया, लेकिन यह स्पष्ट नहीं है कि इस दूसरे भाग के कितने, यदि कोई थे, उत्पादित किए गए थे।<ref name="tcs-necfpu"/> | ||

V30, 16-बिट वाइड | V30, 16-बिट वाइड बाहरी डेटा बस वाला लगभग समान सीपीयू, 1 मार्च 1984 को प्रारम्भ हुआ।<ref name="x86guide-v30-10"/><ref name="shmj"/> यह पिन और ऑब्जेक्ट-कोड इंटेल 8086 के साथ अनुकूल था। | ||

== आईएसए एक्सटेंशन == | == आईएसए एक्सटेंशन == | ||

[[File:Sony CXQ70108D 8 1.jpg|thumb|सोनी CXQ70108D 8 मेगाहर्ट्ज]]V20 के | [[File:Sony CXQ70108D 8 1.jpg|thumb|सोनी CXQ70108D 8 मेगाहर्ट्ज]]V20 के आईएसए में बिट हेरफेर, पैक्ड बीसीडी संचालन, गुणा और भाग के निर्देशों के साथ कई निर्देश सम्मिलित हैं जो 8088 द्वारा निष्पादित नहीं किए गए हैं। उनमें इंटेल 80286 से नए वास्तविक-मोड निर्देश भी सम्मिलित हैं।<ref name="pcm-jun1988"/> | ||

एक अन्य | <code>ADD4S</code>, <code>SUB4S</code>, और <code>CMP4S</code> निर्देश मेमोरी में संग्रहीत विशाल पैक्ड बाइनरी-कोडेड दशमलव संख्याओं को जोड़ने, घटाने और तुलना करने में सक्षम थे। निर्देश <code>ROL4</code>और <code>ROR4</code>चार-बिट निबल्स को घुमाते हैं। एक अन्य परिवार में <code>TEST1</code>, <code>SET1</code>, <code>CLR1</code>, और <code>NOT1</code> निर्देश सम्मिलित हैं, जो अपने ऑपरेंड के एकल बिट्स का परीक्षण, सेट, स्पष्ट और उलटा करते हैं, लेकिन बाद के i80386 समकक्ष <code>[[BT (x86 instruction)|BT]]</code>, <code>[[BTS (x86 instruction)|BTS]]</code>, <code>[[BTR (x86 instruction)|BTR]]</code> और <code>[[BTC (x86 instruction)|BTC]]</code>की तुलना में बहुत कम कुशल हैं; न ही उनकी एनकोडिंग अनुकूल है। एकपक्षीय लंबाई (<code>EXT</code>, <code>INS</code>) के बिट फ़ील्ड निकालने और डालने के लिए दो निर्देश थे। और अंत में, दो अतिरिक्त दोहराव उपसर्ग, <code>[[REP (x86 instruction)|REPE]] और [[REP (x86 instruction)|REPNE]]</code>थे, जिन्होंने बाइट्स या शब्दों की एक स्ट्रिंग (निर्देश<code>[[SCAS (x86 instruction)|SCAS]]</code>और<code>[[CMPS (x86 instruction)|CMPS]]</code>के साथ) को स्कैन करने के लिए मूल आरईपीई और आरईपीएनई निर्देशों में संशोधन किया, जबकि कम या ज्यादा की स्थिति सही थी।<ref name="nec-um" /> | ||

V20 ने एक मोड की प्रस्ताव की जो इंटेल 8080 सीपीयू का अनुकरण करता था। 8080 अनुकरण प्रारंभ करने के लिए एक<code>BRKEM</code>अनुदेश जारी किया जाता है। निर्देश का ऑपरेंड एक इंटरप्ट संख्या निर्दिष्ट करता है जिसके वेक्टर में सेगमेंट:ऑफसेट होता है जहां अनुकरण प्रारम्भ होना है। समाप्त करने के लिए, 8080 कोड में एक<code>RETEM</code>निर्देश जारी किया जाता है। एक सुविधा जिसे प्रायः नियोजित नहीं किया जाता है वह है<code>CALLN</code>(कॉल नेटिव) जो 8086-प्रकार की इंटरप्ट कॉल जारी करती है जो x86 कोड (जो IRET का उपयोग करके वापस आती है) को 8080 कोड के साथ मिलाने में सक्षम बनाती है। | |||

एक अन्य मोड ने प्रोसेसर को <code>HALT</code> निर्देश के माध्यम से बिजली-बचत स्थिति में डाल दिया था।<ref name="chipdb"/><ref name="tpc-v20"/> | |||

== मुकदमे == | == मुकदमे == | ||

1982 में इंटेल ने | 1982 में इंटेल ने एनईसी पर उसके μPD8086 और μPD8088 को लेकर मुकदमा दायर किया। इस मुकदमे का निपटारा अदालत के बाहर ही कर दिया गया, जिसमें एनईसी इंटेल से डिजाइनों का लाइसेंस लेने पर सहमत हो गया था।<ref name="zdnet-jun1998"/> | ||

1984 के अंत में इंटेल ने एनईसी के खिलाफ फिर से मुकदमा दायर किया, जिसमें दावा किया गया कि वी20 और वी30 में माइक्रोकोड ने 8088 और 8086 प्रोसेसर के लिए अपने पेटेंट का उल्लंघन किया।<ref name="iw-fb1989"/>एनईसी सॉफ्टवेयर इंजीनियर हिरोकी कानेको ने इंटेल सीपीयू के हार्डवेयर डिजाइन और मूल इंटेल माइक्रोकोड दोनों का अध्ययन किया था। | 1984 के अंत में इंटेल ने एनईसी के खिलाफ फिर से मुकदमा दायर किया, जिसमें दावा किया गया कि वी20 और वी30 में माइक्रोकोड ने 8088 और 8086 प्रोसेसर के लिए अपने पेटेंट का उल्लंघन किया।<ref name="iw-fb1989"/> एनईसी सॉफ्टवेयर इंजीनियर हिरोकी कानेको ने इंटेल सीपीयू के हार्डवेयर डिजाइन और मूल इंटेल माइक्रोकोड दोनों का अध्ययन किया था। | ||

अपने फैसले में, अदालत ने निर्धारित किया कि नियंत्रण स्टोर में माइक्रोकोड एक कंप्यूटर प्रोग्राम का गठन करता है, और इसलिए कॉपीराइट द्वारा सुरक्षित है।<ref name="hjlt-spring1990"/>उन्होंने यह भी पाया कि इंटेल ने यह सुनिश्चित करने की उपेक्षा करके कि सभी द्वितीय-स्रोत चिप्स उपयुक्त रूप से चिह्नित किए गए थे, अपना कॉपीराइट जब्त कर लिया है। अदालत ने यह भी निर्धारित किया कि एनईसी ने केवल इंटेल के माइक्रोकोड की नकल नहीं की, और यह कि वी20 और वी30 में माइक्रोकोड इंटेल के पेटेंट का उल्लंघन नहीं करने के लिए इंटेल से पर्याप्त रूप से अलग था। | अपने फैसले में, अदालत ने निर्धारित किया कि नियंत्रण स्टोर में माइक्रोकोड एक कंप्यूटर प्रोग्राम का गठन करता है, और इसलिए कॉपीराइट द्वारा सुरक्षित है।<ref name="hjlt-spring1990"/> उन्होंने यह भी पाया कि इंटेल ने यह सुनिश्चित करने की उपेक्षा करके कि सभी द्वितीय-स्रोत चिप्स उपयुक्त रूप से चिह्नित किए गए थे, अपना कॉपीराइट जब्त कर लिया है। अदालत ने यह भी निर्धारित किया कि एनईसी ने केवल इंटेल के माइक्रोकोड की नकल नहीं की, और यह कि वी20 और वी30 में माइक्रोकोड इंटेल के पेटेंट का उल्लंघन नहीं करने के लिए इंटेल से पर्याप्त रूप से अलग था। | ||

इस स्तिथि में जज ने एनईसी के क्लीनरूम साक्ष्य को स्वीकार कर लिया। उन्होंने Rev.0 कोड के संबंध में कोई टिप्पणी किए बिना, एनईसी के Rev.2 माइक्रोकोड के निर्माण के संबंध में एनईसी द्वारा [[रिवर्स इंजीनियरिंग]] के उपयोग को भी मंजूरी दे दी।<ref name="hjlt-spring1990"/> | |||

== संस्करण और उत्तराधिकारी == | == संस्करण और उत्तराधिकारी == | ||

[[File:NEC V20 CPU chip.jpg|thumb| | [[File:NEC V20 CPU chip.jpg|thumb|मदरबोर्ड पर V20]] | ||

[[File:KL NEC V30.jpg|thumb|एनईसी वी30 (μPD70116), 10 मेगाहर्ट्ज]] | [[File:KL NEC V30.jpg|thumb|एनईसी वी30 (μPD70116), 10 मेगाहर्ट्ज]] | ||

[[File:NEC V40.png|thumb|एनईसी V40 (μPD70208)]] | [[File:NEC V40.png|thumb|एनईसी V40 (μPD70208)]] | ||

[[File:UPD70236 01.jpg|thumb|एनईसी V53A (µPD70236A)]] | [[File:UPD70236 01.jpg|thumb|एनईसी V53A (µPD70236A)]] | ||

{| class="wikitable" | {| class="wikitable" | ||

!उत्पाद | |||

!भाग नं. | |||

!विवरण | |||

|- | |- | ||

|'''एनईसी वी30''' | |||

|μPD70116 | |||

|अनिवार्य रूप से 16-बिट बाहरी डेटा बस के साथ एक NEC V20, V30 इंटेल 8086 के साथ पिन अनुकूल था । V30 GTD-5 EAX क्लास 5 सेंट्रल ऑफिस स्विच में उपयोग किए गए 8086 से एक फैक्ट्री अपग्रेड था । इसका उपयोग Psion सीरीज 3 , NEC PC-9801 VM, ओलिवेटी PCS86, Apple II सीरीज के कंप्यूटरों के लिए एप्लाइड इंजीनियरिंग "PC ट्रांसपोर्टर" कार्ड और विभिन्न आर्केड मशीनों (विशेष रूप से Irem द्वारा बनाई गई ) में भी किया गया था। 1980 के दशक के अंत में. वर्षों बाद, बंदाई के हैंडहेल्ड वंडरस्वान गेम कंसोल में एक लो-वोल्टेज V30 MZ संस्करण का उपयोग किया गया । | |||

|- | |- | ||

|''' | |'''एनईसी वी20एचएल''' | ||

| | |μPD70108H | ||

| | |V20 का हाई-स्पीड (16 मेगाहर्ट्ज तक), कम-शक्ति वाला संस्करण। | ||

|- | |- | ||

| ''' | |'''एनईसी वी30एचएल''' | ||

| | |μPD70116H | ||

| | |V30 का हाई-स्पीड (16 मेगाहर्ट्ज तक), कम-शक्ति वाला संस्करण। | ||

|- | |- | ||

| ''' | |'''एनईसी वी25''' | ||

| | |μPD70320 | ||

| | |NEC V20 का एक माइक्रोकंट्रोलर संस्करण। | ||

|- | |- | ||

| ''' | |'''एनईसी वी25एचएस''' | ||

| | |μPD79011 | ||

| | |आंतरिक ROM में RX116 RTOS के साथ V25 का एक संस्करण । | ||

|- | |- | ||

| ''' | |'''एनईसी वी25+''' | ||

| | |μPD70325 | ||

| | |V25 का हाई-स्पीड संस्करण। | ||

|- | |- | ||

| ''' | |'''एनईसी वी33''' | ||

| | |μPD70136 | ||

| | |अलग-अलग पते और डेटा बसों के साथ V30 का एक संस्करण और माइक्रोप्रोग्राम्ड कंट्रोल स्टोर के बजाय हार्डवेयर्ड लॉजिक द्वारा किए गए निर्देश डिकोड के साथ। समान घड़ी आवृत्ति के लिए थ्रूपुट V30 से दोगुना अधिक है। V33 का प्रदर्शन Intel 80286 के बराबर है । मेमोरी एड्रेस स्पेस को 16M बाइट्स तक बढ़ा दिया गया है। दो अतिरिक्त निर्देश, <code>BRKXA</code>और <code>RETXA</code>, विस्तारित एड्रेसिंग मोड का समर्थन करते हैं। 8080 इम्यूलेशन समर्थित नहीं है। | ||

|- | |- | ||

| ''' | |'''एनईसी वी33ए''' | ||

| | |μPD70136A | ||

| | |V33 से भिन्न है क्योंकि इसमें इंटेल के 80X86 प्रोसेसर के साथ अनुकूल इंटरप्ट वेक्टर नंबर हैं। | ||

|- | |- | ||

| ''' | |'''एनईसी वी35''' | ||

| | |μPD70330 | ||

| | |NEC V30 का एक माइक्रोकंट्रोलर संस्करण। | ||

|- | |- | ||

| ''' | |'''एनईसी वी35एचएस''' | ||

| | |μPD79021 | ||

| | |आंतरिक ROM में RX116 RTOS के साथ V35 का एक संस्करण। | ||

|- | |- | ||

| ''' | |'''एनईसी वी35+''' | ||

| | |μPD70335 | ||

| | |V35 का एक उच्च गति संस्करण। | ||

|- | |- | ||

| ''' | |'''एनईसी वी40''' | ||

| | |μPD70208 | ||

| | |V20 का एक एम्बेडेड संस्करण, एकीकृत इंटेल-अनुकूल 8251 USART , 8253 प्रोग्रामयोग्य अंतराल टाइमर और 8255 समानांतर पोर्ट इंटरफ़ेस। ओलिवेटी पीसी1, डिजीसिस्टम्स जेट्टा एक्सडी, शार्प पीसी-4500 और जेनिथ ईज़ी पीसी में उपयोग किया जाता है। | ||

|- | |- | ||

| ''' | |'''एनईसी वी40एचएल''' | ||

| | |μPD70208H | ||

| | |V40 का एक हाई-स्पीड, लो-वोल्टेज संस्करण। | ||

|- | |- | ||

| ''' | |'''एनईसी वी50''' | ||

| | |μPD70216 | ||

| | |V30 का एक एम्बेडेड संस्करण. यह Akai S1000 और S1100 और Korg M1 में मुख्य CPU है।<ref name="korgm1-sm" /><ref name="mz5606-korg-m1r" /> | ||

|- | |- | ||

| ''' | |'''एनईसी वी50एचएल''' | ||

| | |μPD70216H | ||

| | |V50 का एक हाई-स्पीड, लो-वोल्टेज संस्करण। | ||

|- | |- | ||

| ''' | |'''एनईसी वी41''' | ||

| | |μPD70270 | ||

| | |V30HL कोर और PC-XT बाह्य उपकरणों को एकीकृत करता है: 8255 समानांतर पोर्ट इंटरफ़ेस, 8254 प्रोग्रामयोग्य अंतराल टाइमर, 8259 PIC, 8237 DMA नियंत्रक और 8042 कीबोर्ड नियंत्रक। पूर्ण DRAM नियंत्रक को भी एकीकृत करता है। | ||

|- | |- | ||

| ''' | |'''एनईसी वी51''' | ||

| | |μPD70280 | ||

| | |V30HL कोर और PC-XT बाह्य उपकरणों को एकीकृत करता है: 8255 समानांतर पोर्ट इंटरफ़ेस, 8254 प्रोग्रामयोग्य अंतराल टाइमर, 8259 PIC, 8237 DMA नियंत्रक और 8042 कीबोर्ड नियंत्रक। पूर्ण DRAM नियंत्रक को भी एकीकृत करता है। ओलिवेटी क्वाडर्नो PT-XT-20 में उपयोग किया गया था । | ||

|- | |- | ||

| ''' | |'''एनईसी वी53''' | ||

| | |μPD70236 | ||

| | |4-चैनल DMA (μPD71087/i8237), UART (μPD71051/i8251), तीन टाइमर/काउंटर (μPD71054/ i8254 ) और इंटरप्ट कंट्रोलर (μPD71059/ i8259 ) के साथ V33 कोर को एकीकृत करता है। इसका उपयोग Akai MPC3000 और Akai SG01v में किया गया था।<ref name="MPC3000" /><ref name="aj-mpc3000" /> | ||

|- | |- | ||

| ''' | |'''एनईसी वी53ए''' | ||

| | |μPD70236A | ||

| | |कुछ बाह्य उपकरणों को V33A कोर के साथ एकीकृत करता है। शार्प ज़ौरस PI-B304/B308 में प्रयुक्त | ||

|- | |- | ||

| ''' | |'''एनईसी वी55PI''' | ||

|μPD70433 | |||

| μPD70433 | |||

| | | | ||

|- | |- | ||

| ''' | |'''वेडेम वीजी230''' | ||

| | | | ||

| | |एक सिंगल-चिप पीसी प्लेटफ़ॉर्म।<ref name="vadem-dm" /> वीजी230 में 16 मेगाहर्ट्ज एनईसी वी30एचएल प्रोसेसर और आईबीएम पीसी/एक्सटी-अनुकूल कोर लॉजिक, टच-प्लेन सपोर्ट के साथ एलसीडी कंट्रोलर (सीजीए/एटी&टी640x400), कीबोर्ड मैट्रिक्स स्कैनर, डुअल पीसीएमसीआईए 2.1 कार्ड कंट्रोलर, ईएमएस 4.0 हार्डवेयर सपोर्ट सम्मिलित था । 64 एमबी तक, और अंतर्निर्मित टाइमर, पीआईसी, डीएमए, यूएआरटी और आरटीसी नियंत्रक। इसका उपयोग एचपी ओम्निगो 100,120 और आईबीएम साइमन में किया गया था।<ref name="ibm-simon" /> | ||

|- | |- | ||

| ''' | |'''वेडेम वीजी330''' | ||

| | | | ||

| | |वीजी230 के उत्तराधिकारी, इसमें 32 मेगाहर्ट्ज एनईसी वी30एमएक्स प्रोसेसर और आईबीएम पीसी/एटी-अनुकूल कोर लॉजिक के साथ दोहरी पीआईसी, एलसीडी नियंत्रक (640x480), कीबोर्ड मैट्रिक्स स्कैनर, पीसी कार्ड एक्ससीए 2.1 नियंत्रक और एसआईआर पोर्ट सम्मिलित थे । | ||

|- | |- | ||

| ''' | |'''एनईसी वी60''' | ||

| μPD70616 | |μPD70616 | ||

| | |V60 प्रोसेसर के साथ, NEC ने x86 डिज़ाइन से प्रस्थान किया और एक नया, 32-बिट CISC आर्किटेक्चर लॉन्च किया। V60 और V70, जो मुख्य रूप से उनके संबंधित बाहरी पते और डेटा बसों की चौड़ाई में भिन्न थे, दोनों में V20/V30 इम्यूलेशन मोड सम्मिलित था।<ref name="V60-Prog-Ref-Man" />{{rp|§10}}<ref name="tcs-necfpu" /> | ||

|} | |} | ||

<gallery caption=" | |||

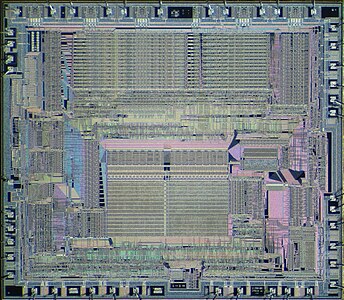

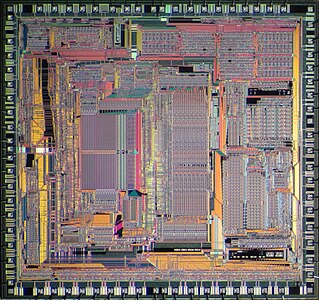

<gallery caption="डाई फोटोस" mode="packed" heights="200px"> | |||

Image:NEC_V30_die.JPG|एनईसी V30 | Image:NEC_V30_die.JPG|एनईसी V30 | ||

Image:NEC_V50_die.JPG|एनईसी V50 | Image:NEC_V50_die.JPG|एनईसी V50 | ||

| Line 207: | Line 203: | ||

== यह भी देखें == | == यह भी देखें == | ||

* | |||

* | * एनईसी आरएक्स116, समर्पित आईट्रॉन-1-आधारित 16-बिट आरटीओएस | ||

* | * एनईसी μPD9002, एक Z80 और x86 अनुकूल सीपीयू | ||

* वीआईए टेक्नोलॉजीज वैकल्पिक निर्देश सेट, एक सीपीयू वैकल्पिक निर्देश सेट मोड में प्रवेश करने और बाहर निकलने के लिए एक समान योजना लागू करता है। | |||

== संदर्भ == | == संदर्भ == | ||

| Line 270: | Line 267: | ||

{{NEC Corporation}} | {{NEC Corporation}} | ||

[[Category: | [[Category:16-बिट माइक्रोप्रोसेसर]] | ||

[[Category:Articles with invalid date parameter in template]] | |||

[[Category:CS1 location test]] | |||

[[Category:CS1 uses 日本語-language script (ja)]] | |||

[[Category:CS1 русский-language sources (ru)]] | |||

[[Category:CS1 日本語-language sources (ja)]] | |||

[[Category:Citation Style 1 templates|M]] | |||

[[Category:Collapse templates]] | |||

[[Category:Created On 19/06/2023]] | [[Category:Created On 19/06/2023]] | ||

[[Category:Lua-based templates]] | |||

[[Category:Machine Translated Page]] | |||

[[Category:NEC x86 माइक्रोप्रोसेसर|V20]] | |||

[[Category:Navigational boxes| ]] | |||

[[Category:Navigational boxes without horizontal lists]] | |||

[[Category:Pages with script errors]] | |||

[[Category:Sidebars with styles needing conversion]] | |||

[[Category:Template documentation pages|Documentation/doc]] | |||

[[Category:Templates Vigyan Ready]] | |||

[[Category:Templates based on the Citation/CS1 Lua module]] | |||

[[Category:Templates generating COinS|Cite magazine]] | |||

[[Category:Templates generating microformats]] | |||

[[Category:Templates that add a tracking category]] | |||

[[Category:Templates that are not mobile friendly]] | |||

[[Category:Templates that generate short descriptions]] | |||

[[Category:Templates using TemplateData]] | |||

[[Category:Use dmy dates from January 2022]] | |||

[[Category:Use list-defined references from January 2022]] | |||

[[Category:Wikipedia fully protected templates|Cite magazine]] | |||

[[Category:Wikipedia metatemplates]] | |||

Latest revision as of 11:42, 13 July 2023

8 MHz V20 in plastic DIP package | |

| General information | |

|---|---|

| Launched | [1] |

| Common manufacturer(s) | |

| Performance | |

| Data width | 16 बिट्स |

| Physical specifications | |

| Transistors |

|

| Cores |

|

| Co-processor |

|

| History | |

| Successor | एनईसी वी60 |

एनईसी V20 एक माइक्रोप्रोसेसर है जिसे एनईसी द्वारा डिजाइन और निर्मित किया गया था। यह इंटेल 8088 के साथ पिन अनुकूल और ऑब्जेक्ट कोड दोनों अनुकूल है, कुछ एक्सटेंशन के साथ इंटेल 80188 के समान एक निर्देश सेट आर्किटेक्चर (आईएसए) के साथ।[2] वी20 को मार्च 1984 में प्रस्तुत किया गया था।[1][2]

सुविधाएँ

V20 के पासे में 63,000 ट्रांजिस्टर सम्मिलित थे; 8088 सीपीयू के 29,000 से दोगुने से भी अधिक।[1] चिप को 8088 द्वारा प्रयुक्त 33% ड्यूटी चक्र की तुलना में 50% के क्लॉक ड्यूटी चक्र के लिए डिज़ाइन किया गया था।[3] V20 में दो, 16-बिट विस्तृत आंतरिक डेटाबेस हैं, जो दो डेटा स्थानांतरण को एक साथ करने की अनुमति देते हैं।[4] इस तरह के अंतरों का मतलब है कि एक V20 सामान्यतः एक ही आवृत्ति पर चलने वाले इंटेल 8088 की तुलना में एक निश्चित समय में अधिक निर्देश पूरा कर सकता है।[2]

V20 को 2-माइक्रोन सीमॉस प्रौद्योगिकी में निर्मित किया गया था।[5][3] प्रारंभिक संस्करण 5, 8, और 10 मेगाहर्ट्ज की गति पर चलते थे।[6] 1990 में, निर्माण प्रक्रिया प्रौद्योगिकी के उन्नयन के परिणामस्वरूप बेहतर प्रदर्शन और कम बिजली की खपत के साथ V20H और V20HL का निर्माण हुआ।[5] बाद के संस्करणों में 12 और 16 मेगाहर्ट्ज की गति जोड़ी गयी। V20HL भी पूरी तरह से स्थिर थे, जिससे उनकी क्लॉक रुक गई थी।

V20 को आंतरिक रूप से 16-बिट वाइड बताया गया था। इसमें एक 8-बिट बाहरी डेटा बस का उपयोग किया गया था जिसे एड्रेस बस के लो बाइट के समान पिन पर मल्टीप्लेक्स किया गया था। इसकी 20-बिट वाइड एड्रेस बस 1 एमबी मेमोरी को संबोधित करने में सक्षम थी।

बताया गया कि V20 इंटेल 8087 फ्लोटिंग-पॉइंट यूनिट (एफपीयू) कोप्रोसेसर के साथ अनुकूल था।[7] एनईसी ने अपना स्वयं का एफपीयू, μPD72091 भी डिज़ाइन किया था, जिसे उत्पादन तक पहुंचने से पहले रद्द कर दिया गया था। उन्होंने एक संशोधित डिज़ाइन, μPD72191 के साथ इसका अनुसरण किया, लेकिन यह स्पष्ट नहीं है कि इस दूसरे भाग के कितने, यदि कोई थे, उत्पादित किए गए थे।[8]

V30, 16-बिट वाइड बाहरी डेटा बस वाला लगभग समान सीपीयू, 1 मार्च 1984 को प्रारम्भ हुआ।[9][5] यह पिन और ऑब्जेक्ट-कोड इंटेल 8086 के साथ अनुकूल था।

आईएसए एक्सटेंशन

V20 के आईएसए में बिट हेरफेर, पैक्ड बीसीडी संचालन, गुणा और भाग के निर्देशों के साथ कई निर्देश सम्मिलित हैं जो 8088 द्वारा निष्पादित नहीं किए गए हैं। उनमें इंटेल 80286 से नए वास्तविक-मोड निर्देश भी सम्मिलित हैं।[10]

ADD4S, SUB4S, और CMP4S निर्देश मेमोरी में संग्रहीत विशाल पैक्ड बाइनरी-कोडेड दशमलव संख्याओं को जोड़ने, घटाने और तुलना करने में सक्षम थे। निर्देश ROL4और ROR4चार-बिट निबल्स को घुमाते हैं। एक अन्य परिवार में TEST1, SET1, CLR1, और NOT1 निर्देश सम्मिलित हैं, जो अपने ऑपरेंड के एकल बिट्स का परीक्षण, सेट, स्पष्ट और उलटा करते हैं, लेकिन बाद के i80386 समकक्ष BT, BTS, BTR और BTCकी तुलना में बहुत कम कुशल हैं; न ही उनकी एनकोडिंग अनुकूल है। एकपक्षीय लंबाई (EXT, INS) के बिट फ़ील्ड निकालने और डालने के लिए दो निर्देश थे। और अंत में, दो अतिरिक्त दोहराव उपसर्ग, REPE और REPNEथे, जिन्होंने बाइट्स या शब्दों की एक स्ट्रिंग (निर्देशSCASऔरCMPSके साथ) को स्कैन करने के लिए मूल आरईपीई और आरईपीएनई निर्देशों में संशोधन किया, जबकि कम या ज्यादा की स्थिति सही थी।[11]

V20 ने एक मोड की प्रस्ताव की जो इंटेल 8080 सीपीयू का अनुकरण करता था। 8080 अनुकरण प्रारंभ करने के लिए एकBRKEMअनुदेश जारी किया जाता है। निर्देश का ऑपरेंड एक इंटरप्ट संख्या निर्दिष्ट करता है जिसके वेक्टर में सेगमेंट:ऑफसेट होता है जहां अनुकरण प्रारम्भ होना है। समाप्त करने के लिए, 8080 कोड में एकRETEMनिर्देश जारी किया जाता है। एक सुविधा जिसे प्रायः नियोजित नहीं किया जाता है वह हैCALLN(कॉल नेटिव) जो 8086-प्रकार की इंटरप्ट कॉल जारी करती है जो x86 कोड (जो IRET का उपयोग करके वापस आती है) को 8080 कोड के साथ मिलाने में सक्षम बनाती है।

एक अन्य मोड ने प्रोसेसर को HALT निर्देश के माध्यम से बिजली-बचत स्थिति में डाल दिया था।[6][7]

मुकदमे

1982 में इंटेल ने एनईसी पर उसके μPD8086 और μPD8088 को लेकर मुकदमा दायर किया। इस मुकदमे का निपटारा अदालत के बाहर ही कर दिया गया, जिसमें एनईसी इंटेल से डिजाइनों का लाइसेंस लेने पर सहमत हो गया था।[12]

1984 के अंत में इंटेल ने एनईसी के खिलाफ फिर से मुकदमा दायर किया, जिसमें दावा किया गया कि वी20 और वी30 में माइक्रोकोड ने 8088 और 8086 प्रोसेसर के लिए अपने पेटेंट का उल्लंघन किया।[13] एनईसी सॉफ्टवेयर इंजीनियर हिरोकी कानेको ने इंटेल सीपीयू के हार्डवेयर डिजाइन और मूल इंटेल माइक्रोकोड दोनों का अध्ययन किया था।

अपने फैसले में, अदालत ने निर्धारित किया कि नियंत्रण स्टोर में माइक्रोकोड एक कंप्यूटर प्रोग्राम का गठन करता है, और इसलिए कॉपीराइट द्वारा सुरक्षित है।[14] उन्होंने यह भी पाया कि इंटेल ने यह सुनिश्चित करने की उपेक्षा करके कि सभी द्वितीय-स्रोत चिप्स उपयुक्त रूप से चिह्नित किए गए थे, अपना कॉपीराइट जब्त कर लिया है। अदालत ने यह भी निर्धारित किया कि एनईसी ने केवल इंटेल के माइक्रोकोड की नकल नहीं की, और यह कि वी20 और वी30 में माइक्रोकोड इंटेल के पेटेंट का उल्लंघन नहीं करने के लिए इंटेल से पर्याप्त रूप से अलग था।

इस स्तिथि में जज ने एनईसी के क्लीनरूम साक्ष्य को स्वीकार कर लिया। उन्होंने Rev.0 कोड के संबंध में कोई टिप्पणी किए बिना, एनईसी के Rev.2 माइक्रोकोड के निर्माण के संबंध में एनईसी द्वारा रिवर्स इंजीनियरिंग के उपयोग को भी मंजूरी दे दी।[14]

संस्करण और उत्तराधिकारी

| उत्पाद | भाग नं. | विवरण |

|---|---|---|

| एनईसी वी30 | μPD70116 | अनिवार्य रूप से 16-बिट बाहरी डेटा बस के साथ एक NEC V20, V30 इंटेल 8086 के साथ पिन अनुकूल था । V30 GTD-5 EAX क्लास 5 सेंट्रल ऑफिस स्विच में उपयोग किए गए 8086 से एक फैक्ट्री अपग्रेड था । इसका उपयोग Psion सीरीज 3 , NEC PC-9801 VM, ओलिवेटी PCS86, Apple II सीरीज के कंप्यूटरों के लिए एप्लाइड इंजीनियरिंग "PC ट्रांसपोर्टर" कार्ड और विभिन्न आर्केड मशीनों (विशेष रूप से Irem द्वारा बनाई गई ) में भी किया गया था। 1980 के दशक के अंत में. वर्षों बाद, बंदाई के हैंडहेल्ड वंडरस्वान गेम कंसोल में एक लो-वोल्टेज V30 MZ संस्करण का उपयोग किया गया । |

| एनईसी वी20एचएल | μPD70108H | V20 का हाई-स्पीड (16 मेगाहर्ट्ज तक), कम-शक्ति वाला संस्करण। |

| एनईसी वी30एचएल | μPD70116H | V30 का हाई-स्पीड (16 मेगाहर्ट्ज तक), कम-शक्ति वाला संस्करण। |

| एनईसी वी25 | μPD70320 | NEC V20 का एक माइक्रोकंट्रोलर संस्करण। |

| एनईसी वी25एचएस | μPD79011 | आंतरिक ROM में RX116 RTOS के साथ V25 का एक संस्करण । |

| एनईसी वी25+ | μPD70325 | V25 का हाई-स्पीड संस्करण। |

| एनईसी वी33 | μPD70136 | अलग-अलग पते और डेटा बसों के साथ V30 का एक संस्करण और माइक्रोप्रोग्राम्ड कंट्रोल स्टोर के बजाय हार्डवेयर्ड लॉजिक द्वारा किए गए निर्देश डिकोड के साथ। समान घड़ी आवृत्ति के लिए थ्रूपुट V30 से दोगुना अधिक है। V33 का प्रदर्शन Intel 80286 के बराबर है । मेमोरी एड्रेस स्पेस को 16M बाइट्स तक बढ़ा दिया गया है। दो अतिरिक्त निर्देश, BRKXAऔर RETXA, विस्तारित एड्रेसिंग मोड का समर्थन करते हैं। 8080 इम्यूलेशन समर्थित नहीं है।

|

| एनईसी वी33ए | μPD70136A | V33 से भिन्न है क्योंकि इसमें इंटेल के 80X86 प्रोसेसर के साथ अनुकूल इंटरप्ट वेक्टर नंबर हैं। |

| एनईसी वी35 | μPD70330 | NEC V30 का एक माइक्रोकंट्रोलर संस्करण। |

| एनईसी वी35एचएस | μPD79021 | आंतरिक ROM में RX116 RTOS के साथ V35 का एक संस्करण। |

| एनईसी वी35+ | μPD70335 | V35 का एक उच्च गति संस्करण। |

| एनईसी वी40 | μPD70208 | V20 का एक एम्बेडेड संस्करण, एकीकृत इंटेल-अनुकूल 8251 USART , 8253 प्रोग्रामयोग्य अंतराल टाइमर और 8255 समानांतर पोर्ट इंटरफ़ेस। ओलिवेटी पीसी1, डिजीसिस्टम्स जेट्टा एक्सडी, शार्प पीसी-4500 और जेनिथ ईज़ी पीसी में उपयोग किया जाता है। |

| एनईसी वी40एचएल | μPD70208H | V40 का एक हाई-स्पीड, लो-वोल्टेज संस्करण। |

| एनईसी वी50 | μPD70216 | V30 का एक एम्बेडेड संस्करण. यह Akai S1000 और S1100 और Korg M1 में मुख्य CPU है।[15][16] |

| एनईसी वी50एचएल | μPD70216H | V50 का एक हाई-स्पीड, लो-वोल्टेज संस्करण। |

| एनईसी वी41 | μPD70270 | V30HL कोर और PC-XT बाह्य उपकरणों को एकीकृत करता है: 8255 समानांतर पोर्ट इंटरफ़ेस, 8254 प्रोग्रामयोग्य अंतराल टाइमर, 8259 PIC, 8237 DMA नियंत्रक और 8042 कीबोर्ड नियंत्रक। पूर्ण DRAM नियंत्रक को भी एकीकृत करता है। |

| एनईसी वी51 | μPD70280 | V30HL कोर और PC-XT बाह्य उपकरणों को एकीकृत करता है: 8255 समानांतर पोर्ट इंटरफ़ेस, 8254 प्रोग्रामयोग्य अंतराल टाइमर, 8259 PIC, 8237 DMA नियंत्रक और 8042 कीबोर्ड नियंत्रक। पूर्ण DRAM नियंत्रक को भी एकीकृत करता है। ओलिवेटी क्वाडर्नो PT-XT-20 में उपयोग किया गया था । |

| एनईसी वी53 | μPD70236 | 4-चैनल DMA (μPD71087/i8237), UART (μPD71051/i8251), तीन टाइमर/काउंटर (μPD71054/ i8254 ) और इंटरप्ट कंट्रोलर (μPD71059/ i8259 ) के साथ V33 कोर को एकीकृत करता है। इसका उपयोग Akai MPC3000 और Akai SG01v में किया गया था।[17][18] |

| एनईसी वी53ए | μPD70236A | कुछ बाह्य उपकरणों को V33A कोर के साथ एकीकृत करता है। शार्प ज़ौरस PI-B304/B308 में प्रयुक्त |

| एनईसी वी55PI | μPD70433 | |

| वेडेम वीजी230 | एक सिंगल-चिप पीसी प्लेटफ़ॉर्म।[19] वीजी230 में 16 मेगाहर्ट्ज एनईसी वी30एचएल प्रोसेसर और आईबीएम पीसी/एक्सटी-अनुकूल कोर लॉजिक, टच-प्लेन सपोर्ट के साथ एलसीडी कंट्रोलर (सीजीए/एटी&टी640x400), कीबोर्ड मैट्रिक्स स्कैनर, डुअल पीसीएमसीआईए 2.1 कार्ड कंट्रोलर, ईएमएस 4.0 हार्डवेयर सपोर्ट सम्मिलित था । 64 एमबी तक, और अंतर्निर्मित टाइमर, पीआईसी, डीएमए, यूएआरटी और आरटीसी नियंत्रक। इसका उपयोग एचपी ओम्निगो 100,120 और आईबीएम साइमन में किया गया था।[20] | |

| वेडेम वीजी330 | वीजी230 के उत्तराधिकारी, इसमें 32 मेगाहर्ट्ज एनईसी वी30एमएक्स प्रोसेसर और आईबीएम पीसी/एटी-अनुकूल कोर लॉजिक के साथ दोहरी पीआईसी, एलसीडी नियंत्रक (640x480), कीबोर्ड मैट्रिक्स स्कैनर, पीसी कार्ड एक्ससीए 2.1 नियंत्रक और एसआईआर पोर्ट सम्मिलित थे । | |

| एनईसी वी60 | μPD70616 | V60 प्रोसेसर के साथ, NEC ने x86 डिज़ाइन से प्रस्थान किया और एक नया, 32-बिट CISC आर्किटेक्चर लॉन्च किया। V60 और V70, जो मुख्य रूप से उनके संबंधित बाहरी पते और डेटा बसों की चौड़ाई में भिन्न थे, दोनों में V20/V30 इम्यूलेशन मोड सम्मिलित था।[21]: §10 [8] |

- डाई फोटोस

यह भी देखें

- एनईसी आरएक्स116, समर्पित आईट्रॉन-1-आधारित 16-बिट आरटीओएस

- एनईसी μPD9002, एक Z80 और x86 अनुकूल सीपीयू

- वीआईए टेक्नोलॉजीज वैकल्पिक निर्देश सेट, एक सीपीयू वैकल्पिक निर्देश सेट मोड में प्रवेश करने और बाहर निकलने के लिए एक समान योजना लागू करता है।

संदर्भ

- ↑ 1.0 1.1 1.2 "8088 & V20". X86 CPU's Guide. 2018-11-17.

- ↑ 2.0 2.1 2.2 Gennadiy, Shvets. "NEC V20 processor family". CPU-World.

- ↑ 3.0 3.1 Davis, Stephen R. (1985-12-24). "Turbocharging Your PC with the V-Series". PC Magazine. pp. 181–186.

- ↑ Chodorek, Robert Ryszard (November–December 2021). "NEC V20: Inspiring, Inconspicuous". IEEE Micro. 41 (6): 158–159. doi:10.1109/MM.2021.3115870.

- ↑ 5.0 5.1 5.2 1983年 — 16bitマイクロプサッサV30の開発(NEC) [1983 — Development of the V30 16-bit Microprocessor (NEC)] (in 日本語). 2010-10-23. Archived from the original on 2019-07-13. Retrieved 2020-07-14.

- ↑ 6.0 6.1 µPD70108 — V20 16-/8-bit Microprocessor (PDF). NEC. June 1994.

- ↑ 7.0 7.1 Mahoney, Bob (1985-10-16). "Output of file: NECV20B.ALL contained in archive: NEC-V20.ZIP". The Programmer's Corner.

- ↑ 8.0 8.1 Culver, John (2021-09-01). "NEC's Forgotten FPUs". The CPU Shack.

- ↑ "Nec V30 D70116C-10". X86 CPUS' GUIDE. 2020-07-15.

- ↑ Hummel, Robert L. (1988-06-14). "PC Tutor — Mixing Processors". PC Magazine. pp. 377–378.

- ↑ "NEC User's Manual, 16-Bit V Series, 16-/8- and 16-bit microprocessors, Instruction" (PDF). September 2000. Retrieved 2014-11-25.

- ↑ Lemos, Robert (1998-06-08). "NEC case opened up market for cloning". ZDNet.

- ↑ Parker, Rachel (1989-02-13). "Judge Declares Microcode Copyrightable". InfoWorld. p. 8.

- ↑ 14.0 14.1 Contreras, Jorge; Handley, Laura; Yang, Terrence (March–May 1990). "NEC v. Intel: Breaking New Ground in the Law of Copyright" (PDF). Harvard Journal of Law and Technology. 3: 209–222.

- ↑ Korg M1 Service Manual

- ↑ Russ, Martin (July 1989). "Korg M1R". Sound On Sound. United Kingdom. pp. 48–52. Retrieved 2022-08-13.

- ↑ "Mame/Mpc3000.CPP at 251b11266dcd394741e6b48c00a5c9131ef68673 · mamedev/Mame". GitHub. 2022-11-23.

- ↑ "AKAI MPC 3000: The Best Drum Machine of All Time". Audio Jive. 2020-12-09.

- ↑ Vadem VG230 Developer's Manual

- ↑ Nochkin, Alexander (2013-07-10). "IBM Simon — первый в мире смартфон. Что внутри?" [The IBM Simon is the world's first smartphone. What is inside?]. habr.com (in русский).

- ↑ μPD70616 Programmer's Reference Manual (PRELIMINARY ed.). NEC. November 1986.

अग्रिम पठन

- V20/V30 User's Manual. NEC. October 1986. Archived from the original (PDF) on 2013-01-08.

- Davis, Randy (December 1985 – January 1986). Written at Greenville, Texas, USA. "The New NEC Microprocessors - 8080, 8086, Or 8088?" (PDF). Micro Cornucopia. No. 27. Bend, Oregon, USA. pp. 4–7. ISSN 0747-587X. Archived (PDF) from the original on 2020-02-11. Retrieved 2020-02-11.

बाहरी संबंध

- Buchty, Rainer. "Casiorama". www.buchty.net.

- "NEC V20". cpu-collection.de.

- Hinckley, Robert C. (January 1987). "NEC v. Intel: Will Hardware Be Drawn into the Black Hole of Copyright Editors'". Santa Clara High Technology Law Journal. Vol. 3, no. 1. pp. 23–72.