कारणीय प्रारूप: Difference between revisions

No edit summary |

No edit summary |

||

| Line 15: | Line 15: | ||

पावर MOSFET के डिज़ाइन की संभावना मॉसफेट और सीएमओएस प्रौद्योगिकी के विकास के द्वारा संभव बनी है, जो 1960 के दशक से एकीकृत परिप्रेक्ष्यों के निर्माण के लिए प्रयोग की जाती है। पावर MOSFET अपने कार्यसिद्धांत को अपने कम-बिजली संस्करण, लेटरल MOSFET के साथ साझा करता है। पावर MOSFET, जो आमतौर पर पावर इलेक्ट्रॉनिक्स में प्रयोग होता है, मानक MOSFET से अनुकूलित किया गया था और 1970 के दशक में वाणिज्यिक रूप से प्रस्तुत किया गया था।<ref>{{Cite book |last1=Irwin |first1=J. David |title=औद्योगिक इलेक्ट्रॉनिक्स हैंडबुक|date=1997 |publisher=[[CRC Press]] |isbn=9780849383434 |page=218 |url=https://books.google.com/books?id=s0k9kGs5bHYC&pg=PA218}}</ref> | पावर MOSFET के डिज़ाइन की संभावना मॉसफेट और सीएमओएस प्रौद्योगिकी के विकास के द्वारा संभव बनी है, जो 1960 के दशक से एकीकृत परिप्रेक्ष्यों के निर्माण के लिए प्रयोग की जाती है। पावर MOSFET अपने कार्यसिद्धांत को अपने कम-बिजली संस्करण, लेटरल MOSFET के साथ साझा करता है। पावर MOSFET, जो आमतौर पर पावर इलेक्ट्रॉनिक्स में प्रयोग होता है, मानक MOSFET से अनुकूलित किया गया था और 1970 के दशक में वाणिज्यिक रूप से प्रस्तुत किया गया था।<ref>{{Cite book |last1=Irwin |first1=J. David |title=औद्योगिक इलेक्ट्रॉनिक्स हैंडबुक|date=1997 |publisher=[[CRC Press]] |isbn=9780849383434 |page=218 |url=https://books.google.com/books?id=s0k9kGs5bHYC&pg=PA218}}</ref> | ||

पावर MOSFET | पावर MOSFET विश्व में सबसे आम पावर सेमीकंडक्टर उपकरण है, क्योंकि इसे कम गेट ड्राइव पावर, तेज स्विचिंग गति,<ref name="aosmd">{{Cite web |title=पावर MOSFET मूल बातें|url=http://www.aosmd.com/res/application_notes/mosfets/Power_MOSFET_Basics.pdf |website=Alpha & Omega Semiconductor |access-date=29 July 2019}}</ref> आसान परालेलिंग क्षमता,<ref name="aosmd" /><ref name="Duncan178">{{Cite book |last1=Duncan |first1=Ben |title=उच्च प्रदर्शन ऑडियो पावर एम्पलीफायर|date=1996 |publisher=[[Elsevier]] |isbn=9780080508047 |pages=[https://archive.org/details/highperfomanceau0000dunc/page/178 178–81] |url=https://archive.org/details/highperfomanceau0000dunc/page/178 }}</ref> व्यापक बैंडविड्थ, कठोरता, आसान ड्राइव, सरल बायसिंग, आवेदन करने में आसानी और मरम्मत करने में आसानी के कारण।<ref name="Duncan178" />विशेष रूप से, यह सबसे अधिक प्रयोग होने वाला कम वोल्टेज (200 V से कम) स्विच है। इसे विभिन्न अनुप्रयोगों में पाया जा सकता है, जैसे कि अधिकांश बिजली आपूर्ति, [[डीसी-टू-डीसी कनवर्टर]], लो-वोल्टेज [[मोटर नियंत्रक]], और बहुत सारे अन्य अनुप्रयोगों में। | ||

== इतिहास == | == इतिहास == | ||

Revision as of 21:50, 7 July 2023

Two power MOSFETs in the surface-mount package D2PAK. Each of these components can sustain a blocking voltage of 120 volts and a continuous current of 30 amperes with appropriate heatsinking. | |

| Working principle | Semiconductor |

|---|---|

एक पावर MOSFET एक विशेष प्रकार का मेटल-ऑक्साइड-सेमीकंडक्टर फ़ील्ड-इफ़ेक्ट ट्रांजिस्टर (MOSFET) है जो महत्वपूर्ण बिजली स्तरों को संभालने के लिए डिज़ाइन किया जाता है।अन्य पावर सेमीकंडक्टर उपकरणों की तुलना में, जैसे विद्युत रोधित गेट द्विध्रुवी ट्रांजिस्टर(आईजीबीटी) या थाइरिस्टर, इसका मुख्य लाभ उच्च स्विचिंग गति और कम वोल्टेज पर अच्छी दक्षता है।यह IGBT के साथ एक अलग गेट साझा करता है जिससे इसे आसानी से ड्राइव किया जा सकता है।कभी-कभी इन्हें कम गेन का सामना करना पड़ सकता है, कभी-कभी इतनी दर्जा तक कि गेट वोल्टेज नियंत्रण के तहत वोल्टेज से अधिक होनी चाहिए।

पावर MOSFET के डिज़ाइन की संभावना मॉसफेट और सीएमओएस प्रौद्योगिकी के विकास के द्वारा संभव बनी है, जो 1960 के दशक से एकीकृत परिप्रेक्ष्यों के निर्माण के लिए प्रयोग की जाती है। पावर MOSFET अपने कार्यसिद्धांत को अपने कम-बिजली संस्करण, लेटरल MOSFET के साथ साझा करता है। पावर MOSFET, जो आमतौर पर पावर इलेक्ट्रॉनिक्स में प्रयोग होता है, मानक MOSFET से अनुकूलित किया गया था और 1970 के दशक में वाणिज्यिक रूप से प्रस्तुत किया गया था।[2] पावर MOSFET विश्व में सबसे आम पावर सेमीकंडक्टर उपकरण है, क्योंकि इसे कम गेट ड्राइव पावर, तेज स्विचिंग गति,[3] आसान परालेलिंग क्षमता,[3][4] व्यापक बैंडविड्थ, कठोरता, आसान ड्राइव, सरल बायसिंग, आवेदन करने में आसानी और मरम्मत करने में आसानी के कारण।[4]विशेष रूप से, यह सबसे अधिक प्रयोग होने वाला कम वोल्टेज (200 V से कम) स्विच है। इसे विभिन्न अनुप्रयोगों में पाया जा सकता है, जैसे कि अधिकांश बिजली आपूर्ति, डीसी-टू-डीसी कनवर्टर, लो-वोल्टेज मोटर नियंत्रक, और बहुत सारे अन्य अनुप्रयोगों में।

इतिहास

MOSFET का आविष्कार 1959 में बेल लैब्स में मोहम्मद एम. अटाला और दावों कहंग द्वारा किया गया था। यह पावर इलेक्ट्रॉनिक्स में एक सफलता थी। MOSFETs की पीढ़ियों ने पावर डिजाइनरों को प्रदर्शन और घनत्व स्तर प्राप्त करने में सक्षम बनाया जो द्विध्रुवी ट्रांजिस्टर के साथ संभव नहीं है।[5] 1969 में, Hitachi ने पहली ऊर्ध्वाधर शक्ति MOSFET पेश की,[6] जिसे बाद में वीएमओएस (वी-ग्रूव एमओएसएफईटी) के नाम से जाना जाएगा।[7] उसी वर्ष, स्व-संरेखित गेट के साथ MOSFET#DMOS (डबल-डिफ्यूज्ड MOSFET) की रिपोर्ट सबसे पहले राष्ट्रीय उन्नत औद्योगिक विज्ञान और प्रौद्योगिकी संस्थान (ETL) के वाई. तारुई, वाई. हयाशी और तोशीहिरो सेकिगावा ने की थी।[8][9] 1974 में, तोहोकू विश्वविद्यालय में आदेश-स्थिति निशिजावा ने ऑडियो के लिए एक पावर MOSFET का आविष्कार किया, जिसे जल्द ही यामाहा कॉर्पोरेशन द्वारा उनके उच्च निष्ठा [[ऑडियो पावर एम्पलीफायर]] के लिए निर्मित किया गया था। JVC, पायनियर कॉर्पोरेशन, सोनी और तोशीबा ने भी 1974 में पावर MOSFETs के साथ एम्पलीफायरों का निर्माण शुरू किया।[10] सिलिकॉनिक्स ने 1975 में व्यावसायिक रूप से VMOS पेश किया।[7]

VMOS और DMOS विकसित होकर VDMOS (वर्टिकल DMOS) के नाम से जाने गए।[10]एचपी लैब्स में जॉन एल. मोल की अनुसंधान टीम ने 1977 में डीएमओएस प्रोटोटाइप तैयार किया, और वीएमओएस पर फायदे का प्रदर्शन किया, जिसमें कम ऑन-प्रतिरोध और उच्च ब्रेकडाउन वोल्टेज शामिल थे।[7]उसी वर्ष, हिताची ने एलडीएमओएस (पार्श्व डीएमओएस) पेश किया, जो डीएमओएस का एक समतल प्रकार है। हिताची 1977 और 1983 के बीच एकमात्र एलडीएमओएस निर्माता थी, उस दौरान एलडीएमओएस का उपयोग एचएच इलेक्ट्रॉनिक्स (वी-सीरीज़) और एशली ऑडियो जैसे निर्माताओं के ऑडियो पावर एम्पलीफायरों में किया जाता था, और संगीत और सार्वजनिक संबोधन प्रणालियों के लिए उपयोग किया जाता था।[10]1995 में 2जी डिजिटल सेल्युलर नेटवर्क की शुरुआत के साथ, एलडीएमओएस 2जी, 3जी जैसे मोबाइल नेटवर्क में सबसे व्यापक रूप से इस्तेमाल किया जाने वाला आरएफ पावर एम्पलीफायर बन गया।[11] और 4जी.[12] एलेक्स लिडो ने 1977 में स्टैनफोर्ड विश्वविद्यालय में हेक्सफेट, एक हेक्सागोनल प्रकार की पावर एमओएसएफईटी का सह-आविष्कार किया।[13] टॉम हरमन के साथ।[14] HexFET का 1978 में अंतर्राष्ट्रीय सुधारक द्वारा व्यावसायीकरण किया गया था।[7][14]इंसुलेटेड-गेट बाइपोलर ट्रांजिस्टर (IGBT), जो पावर MOSFET और द्विध्रुवी जंक्शन ट्रांजिस्टर (BJT) दोनों के तत्वों को जोड़ता है, 1977 और 1979 के बीच सामान्य विद्युतीय में बी. जयंत बालिगा द्वारा विकसित किया गया था।[15] सुपरजंक्शन MOSFET एक प्रकार का पावर MOSFET है जो P+ कॉलम का उपयोग करता है जो N-एपिटैक्सी परत में प्रवेश करता है। पी और एन परतों को ढेर करने का विचार पहली बार 1978 में ओसाका विश्वविद्यालय में शोज़ो शिरोटा और शिगियो कनेडा द्वारा प्रस्तावित किया गया था।[16] फिलिप्स में डेविड जे. कोए ने 1984 में एक यूएस पेटेंट दाखिल करके वैकल्पिक पी-टाइप और एन-टाइप परतों के साथ सुपरजंक्शन एमओएसएफईटी का आविष्कार किया, जिसे 1988 में प्रदान किया गया था।[17]

अनुप्रयोग

पावर MOSFET दुनिया में सबसे अधिक इस्तेमाल किया जाने वाला पावर सेमीकंडक्टर उपकरण है।[3] As of 2010[update], पावर सेमीकंडक्टर डिवाइस बाजार में पावर MOSFET की हिस्सेदारी 53% है, जो इंसुलेटेड-गेट बाइपोलर ट्रांजिस्टर (27%), आरएफ पावर एम्पलीफायर (11%) और बाइपोलर जंक्शन ट्रांजिस्टर (9%) से आगे है।[18] As of 2018[update], प्रतिवर्ष 50 बिलियन से अधिक पावर MOSFETs भेजे जाते हैं।[19] इनमें ट्रेंच पावर MOSFET शामिल है, जिसकी फरवरी 2017 तक 100 बिलियन से अधिक इकाइयाँ बिकीं।[20] और STMicroelectronics का MDmesh (सुपरजंक्शन MOSFET) जिसने 5 बिलियन यूनिट्स बेची हैं as of 2019[update].[16]

पावर MOSFETs का उपयोग आमतौर पर उपभोक्ता इलेक्ट्रॉनिक्स की एक विस्तृत श्रृंखला के लिए किया जाता है।[21][22] आरएफ डीएमओएस, जिसे आरएफ पावर एमओएसएफईटी के रूप में भी जाना जाता है, आकाशवाणी आवृति (आरएफ) अनुप्रयोगों के लिए डिज़ाइन किया गया एक प्रकार का डीएमओएस पावर ट्रांजिस्टर है। इसका उपयोग विभिन्न रेडियो और आरएफ अनुप्रयोगों में किया जाता है।[23][24] पावर MOSFETs का व्यापक रूप से परिवहन प्रौद्योगिकी में उपयोग किया जाता है,[25][26][27] जिसमें वाहनों की एक विस्तृत श्रृंखला शामिल है।

ऑटोमोटिव उद्योग में,[28][29][30] ऑटोमोटिव इलेक्ट्रॉनिक्स में पावर MOSFETs का व्यापक रूप से उपयोग किया जाता है।[31][32][21]

पावर MOSFETs (DMOS, LDMOS और VMOS सहित) आमतौर पर अन्य अनुप्रयोगों की एक विस्तृत श्रृंखला के लिए उपयोग किए जाते हैं।

मूल संरचना

1970 के दशक में कई संरचनाओं की खोज की गई थी, जब पहली वाणिज्यिक पावर एमओएसएफईटी पेश की गई थी। हालाँकि, उनमें से अधिकांश को वर्टिकल डिफ्यूज्ड एमओएस (वीडीएमओएस) संरचना (जिसे डबल-डिफ्यूज्ड एमओएस या बस डीएमओएस भी कहा जाता है) और एलडीएमओएस (लेटरली डिफ्यूज्ड एमओएस) संरचना के पक्ष में छोड़ दिया गया है (कम से कम हाल तक)।

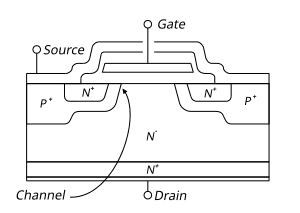

वीडीएमओएस का क्रॉस सेक्शन (चित्र 1 देखें) डिवाइस की ऊर्ध्वाधरता को दर्शाता है: यह देखा जा सकता है कि स्रोत इलेक्ट्रोड को नाली के ऊपर रखा गया है, जिसके परिणामस्वरूप ट्रांजिस्टर चालू स्थिति में होने पर मुख्य रूप से ऊर्ध्वाधर धारा उत्पन्न होती है। वीडीएमओएस में प्रसार विनिर्माण प्रक्रिया को संदर्भित करता है: पी कुएं (चित्र 1 देखें) एक प्रसार प्रक्रिया द्वारा प्राप्त किए जाते हैं (वास्तव में पी और एन प्राप्त करने के लिए एक दोहरी प्रसार प्रक्रिया)+क्षेत्र, इसलिए नाम डबल डिफ्यूज्ड)।

पावर MOSFETs की संरचना पार्श्व MOSFET से भिन्न होती है: अधिकांश बिजली उपकरणों की तरह, उनकी संरचना ऊर्ध्वाधर होती है न कि समतलीय। एक तलीय संरचना में, वर्तमान और ब्रेकडाउन वोल्टेज रेटिंग दोनों चैनल आयामों (क्रमशः चैनल की चौड़ाई और लंबाई) के कार्य हैं, जिसके परिणामस्वरूप सिलिकॉन रियल एस्टेट का अकुशल उपयोग होता है। एक ऊर्ध्वाधर संरचना के साथ, ट्रांजिस्टर की वोल्टेज रेटिंग डोपिंग (अर्धचालक) और एन एपिटैक्सियल परत की मोटाई (क्रॉस सेक्शन देखें) का एक कार्य है, जबकि वर्तमान रेटिंग चैनल की चौड़ाई का एक कार्य है। इससे ट्रांजिस्टर के लिए सिलिकॉन के एक कॉम्पैक्ट टुकड़े के भीतर उच्च अवरोधक वोल्टेज और उच्च धारा दोनों को बनाए रखना संभव हो जाता है।

एलडीएमओएस पार्श्व संरचना वाले पावर एमओएसएफईटी हैं। इनका उपयोग मुख्य रूप से हाई-एंड ऑडियो पावर एम्पलीफायरों में किया जाता है,[10]और वायरलेस सेल्युलर नेटवर्क में आरएफ पावर एम्पलीफायर, जैसे 2जी, 3जी,[11]और 4जी.[12]उनका लाभ ऊर्ध्वाधर MOSFETs की तुलना में संतृप्त क्षेत्र (द्विध्रुवी जंक्शन ट्रांजिस्टर के रैखिक क्षेत्र के अनुरूप) में बेहतर व्यवहार है। वर्टिकल MOSFETs को अनुप्रयोगों को स्विच करने के लिए डिज़ाइन किया गया है, इसलिए उनका उपयोग केवल चालू या बंद स्थिति में किया जाता है।

ऑन-स्टेट प्रतिरोध

जब पावर MOSFET ऑन-स्टेट में होता है (ऑपरेशन मोड पर चर्चा के लिए MOSFET देखें), तो यह ड्रेन और स्रोत टर्मिनलों के बीच एक प्रतिरोधक व्यवहार प्रदर्शित करता है। चित्र 2 में देखा जा सकता है कि यह प्रतिरोध (जिसे R कहा जाता है)DSon ऑन-स्टेट में ड्रेन टू सोर्स प्रतिरोध के लिए) कई प्राथमिक योगदानों का योग है:

- आरS स्रोत प्रतिरोध है. यह पैकेज के स्रोत टर्मिनल से MOSFET के चैनल के बीच सभी प्रतिरोधों का प्रतिनिधित्व करता है: तार का जोड़ का प्रतिरोध, स्रोत धातुकरण का, और एन का प्रतिरोध+कुएँ;

- आरch. यह चैनल प्रतिरोध है. यह चैनल की चौड़ाई और किसी दिए गए डाई आकार के लिए चैनल घनत्व के व्युत्क्रमानुपाती होता है। चैनल प्रतिरोध आर के मुख्य योगदानकर्ताओं में से एक हैDSon कम वोल्टेज वाले MOSFETs, और चैनल घनत्व को बढ़ाने के लिए उनके सेल आकार को कम करने के लिए गहन कार्य किया गया है;

- आरa पहुँच प्रतिरोध है. यह सीधे गेट इलेक्ट्रोड के नीचे एपिटैक्सियल ज़ोन के प्रतिरोध का प्रतिनिधित्व करता है, जहां वर्तमान की दिशा क्षैतिज (चैनल में) से ऊर्ध्वाधर (नाली संपर्क तक) में बदलती है;

- आरJFET ऊपर उल्लिखित सेल आकार में कमी का हानिकारक प्रभाव है: पी इम्प्लांटेशन (चित्र 1 देखें) एक परजीवी जेएफईटी ट्रांजिस्टर के द्वार बनाते हैं जो वर्तमान प्रवाह की चौड़ाई को कम करते हैं;

- आरn एपिटैक्सियल परत का प्रतिरोध है। चूंकि इस परत की भूमिका अवरोधक वोल्टेज, आर को बनाए रखना हैn यह सीधे डिवाइस की वोल्टेज रेटिंग से संबंधित है। एक उच्च वोल्टेज MOSFET के लिए एक मोटी, कम-डोप्ड परत की आवश्यकता होती है, यानी, अत्यधिक प्रतिरोधी, जबकि कम-वोल्टेज ट्रांजिस्टर को केवल उच्च डोपिंग स्तर, यानी, कम प्रतिरोधी के साथ एक पतली परत की आवश्यकता होती है। परिणामस्वरूप, आरn उच्च-वोल्टेज MOSFETs के प्रतिरोध के लिए जिम्मेदार मुख्य कारक है;

- आरD R के समतुल्य हैS नाली के लिए. यह ट्रांजिस्टर सब्सट्रेट के प्रतिरोध का प्रतिनिधित्व करता है (चित्रा 1 में क्रॉस सेक्शन स्केल पर नहीं है, निचला एन+परत वास्तव में सबसे मोटी है) और पैकेज कनेक्शन की।

ब्रेकडाउन वोल्टेज/ऑन-स्टेट प्रतिरोध ट्रेड-ऑफ

जब ऑफ-स्टेट में, पावर MOSFET एक पिन डायोड (पी द्वारा गठित) के बराबर होता है+प्रसार, एन−एपिटैक्सियल परत और एन+सब्सट्रेट). जब यह अत्यधिक गैर-सममित संरचना रिवर्स-बायस्ड होती है, तो स्पेस-चार्ज क्षेत्र मुख्य रूप से प्रकाश-डोप्ड पक्ष पर, यानी एन के ऊपर फैलता है।−परत. इसका मतलब यह है कि इस परत को MOSFET के अधिकांश ऑफ-स्टेट ड्रेन-टू-सोर्स वोल्टेज का सामना करना पड़ता है।

हालाँकि, जब MOSFET चालू स्थिति में होता है, तो यह N−परत का कोई कार्य नहीं है। इसके अलावा, चूंकि यह हल्का डोप किया गया क्षेत्र है, इसकी आंतरिक प्रतिरोधकता नगण्य है और MOSFET के ऑन-स्टेट ड्रेन-टू-सोर्स प्रतिरोध (R) में जुड़ जाती है।DSon) (यह आर हैn चित्र 2 में प्रतिरोध)।

दो मुख्य पैरामीटर ब्रेकडाउन वोल्टेज और आर दोनों को नियंत्रित करते हैंDSon ट्रांजिस्टर का: डोपिंग स्तर और एन की मोटाई−एपिटैक्सियल परत. परत जितनी मोटी होगी और इसका डोपिंग स्तर जितना कम होगा, ब्रेकडाउन वोल्टेज उतना ही अधिक होगा। इसके विपरीत, परत जितनी पतली होगी और डोपिंग स्तर जितना अधिक होगा, आर उतना ही कम होगाDSon (और इसलिए MOSFET की चालन हानि जितनी कम होगी)। इसलिए, यह देखा जा सकता है कि MOSFET के डिज़ाइन में इसकी वोल्टेज रेटिंग और इसके ऑन-स्टेट प्रतिरोध के बीच एक समझौता है।[citation needed] यह चित्र 3 में कथानक द्वारा प्रदर्शित किया गया है।

बॉडी डायोड

चित्र 1 में देखा जा सकता है कि स्रोत धातुकरण दोनों एन को जोड़ता है+और पी+प्रत्यारोपण, हालांकि MOSFET के संचालन सिद्धांत के लिए केवल स्रोत को N से कनेक्ट करने की आवश्यकता होती है+ज़ोन. हालाँकि, यदि ऐसा होता, तो इसके परिणामस्वरूप एन-डोप्ड स्रोत और ड्रेन के बीच एक फ्लोटिंग पी ज़ोन बन जाता, जो एक गैर-कनेक्टेड बेस वाले बाइपोलर जंक्शन ट्रांजिस्टर#एनपीएन के बराबर है। कुछ शर्तों के तहत (उच्च ड्रेन करंट के तहत, जब ऑन-स्टेट ड्रेन टू सोर्स वोल्टेज कुछ वोल्ट के क्रम में होता है), यह परजीवी एनपीएन ट्रांजिस्टर चालू हो जाएगा, जिससे एमओएसएफईटी अनियंत्रित हो जाएगा। स्रोत धातुकरण के लिए पी इम्प्लांटेशन का कनेक्शन परजीवी ट्रांजिस्टर के आधार को उसके उत्सर्जक (एमओएसएफईटी के स्रोत) से छोटा कर देता है और इस प्रकार नकली लैचिंग को रोकता है। हालाँकि, यह समाधान MOSFET के ड्रेन (कैथोड) और स्रोत (एनोड) के बीच एक डायोड बनाता है, जिससे यह केवल एक दिशा में करंट को अवरुद्ध करने में सक्षम होता है।

बॉडी डायोड का उपयोग एच ब्रिज या हाफ ब्रिज जैसे कॉन्फ़िगरेशन में आगमनात्मक भार के लिए फ्लाईबैक डायोड के रूप में किया जा सकता है। हालांकि इन डायोडों में आम तौर पर उच्च फॉरवर्ड वोल्टेज ड्रॉप होता है, वे बड़ी धाराओं को संभाल सकते हैं और कई अनुप्रयोगों में पर्याप्त होते हैं, जिससे भाग की संख्या कम हो जाती है, और इस प्रकार, डिवाइस की लागत और बोर्ड स्थान कम हो जाता है। दक्षता बढ़ाने के लिए, बॉडी डायोड द्वारा करंट प्रवाहित करने के समय को कम करने के लिए अक्सर तुल्यकालिक सुधार का उपयोग किया जाता है।

स्विचिंग ऑपरेशन

उनकी एकध्रुवीय प्रकृति के कारण, पावर MOSFET बहुत तेज़ गति से स्विच कर सकता है। वास्तव में, द्विध्रुवी उपकरणों की तरह अल्पसंख्यक वाहकों को हटाने की कोई आवश्यकता नहीं है। कम्यूटेशन गति में एकमात्र आंतरिक सीमा MOSFET की आंतरिक कैपेसिटेंस के कारण है (चित्र 4 देखें)। ट्रांजिस्टर स्विच होने पर इन कैपेसिटेंस को चार्ज या डिस्चार्ज किया जाना चाहिए। यह अपेक्षाकृत धीमी प्रक्रिया हो सकती है क्योंकि गेट कैपेसिटेंस के माध्यम से प्रवाहित होने वाली धारा बाहरी ड्राइवर सर्किट द्वारा सीमित होती है। यह सर्किट वास्तव में ट्रांजिस्टर की कम्यूटेशन गति को निर्देशित करेगा (यह मानते हुए कि पावर सर्किट में पर्याप्त रूप से कम प्रेरकत्व है)।

धारिता

MOSFET डेटा शीट में, कैपेसिटेंस को अक्सर C नाम दिया जाता हैiss (इनपुट कैपेसिटेंस, ड्रेन और सोर्स टर्मिनल छोटा), सीoss (आउटपुट कैपेसिटेंस, गेट और स्रोत छोटा), और सीrss (रिवर्स ट्रांसफर कैपेसिटेंस, जमीन से जुड़ा स्रोत)। इन कैपेसिटेंस और नीचे वर्णित कैपेसिटेंस के बीच संबंध है:

गेट टू सोर्स कैपेसिटेंस

सीGS कैपेसिटेंस का गठन C के समानांतर कनेक्शन से होता हैoxN+, सीoxP और सीoxm (चित्र 4 देखें)। जैसा कि एन+ और पी क्षेत्र अत्यधिक डोप किए गए हैं, दो पूर्व कैपेसिटेंस को स्थिर माना जा सकता है। सीoxm (पॉलीसिलिकॉन) गेट और (धातु) स्रोत इलेक्ट्रोड के बीच की धारिता है, इसलिए यह भी स्थिर है। इसलिए, सी पर विचार करना आम बात हैGS एक स्थिर धारिता के रूप में, अर्थात इसका मान ट्रांजिस्टर की स्थिति पर निर्भर नहीं करता है।

गेट टू ड्रेन कैपेसिटेंस

सीGD कैपेसिटेंस को दो प्राथमिक कैपेसिटेंस की श्रृंखला में कनेक्शन के रूप में देखा जा सकता है। पहला है ऑक्साइड कैपेसिटेंस (CoxD), गेट इलेक्ट्रोड, सिलिकॉन डाइऑक्साइड और एन एपिटैक्सियल परत के शीर्ष द्वारा गठित। इसका एक स्थिर मूल्य है. दूसरी धारिता (CGDj) जब MOSFET ऑफ-स्टेट में होता है तो डिप्लेशन क्षेत्र|स्पेस-चार्ज ज़ोन के विस्तार के कारण होता है। इसलिए, यह ड्रेन टू गेट वोल्टेज पर निर्भर है। इससे C का मान ज्ञात होता हैGD है:

निकास से स्रोत धारिता

चूंकि स्रोत धातुकरण पी-कुओं को ओवरलैप करता है (चित्र 1 देखें), नाली और स्रोत टर्मिनलों को पी-एन जंक्शन द्वारा अलग किया जाता है। इसलिए, सीDS जंक्शन धारिता है. यह एक गैर-रैखिक धारिता है, और इसके मान की गणना C के समान समीकरण का उपयोग करके की जा सकती हैGDj.

अन्य गतिशील तत्व

पैकेजिंग अधिष्ठापन

संचालित करने के लिए, MOSFET को बाहरी सर्किट से जोड़ा जाना चाहिए, ज्यादातर समय वायर बॉन्डिंग का उपयोग करते हुए (हालांकि वैकल्पिक तकनीकों की जांच की जाती है)। ये कनेक्शन एक परजीवी अधिष्ठापन प्रदर्शित करते हैं, जो किसी भी तरह से MOSFET तकनीक के लिए विशिष्ट नहीं है, लेकिन उच्च कम्यूटेशन गति के कारण इसका महत्वपूर्ण प्रभाव पड़ता है। परजीवी अधिष्ठापन अपने वर्तमान स्थिरांक को बनाए रखते हैं और ट्रांजिस्टर बंद होने के दौरान ओवरवॉल्टेज उत्पन्न करते हैं, जिसके परिणामस्वरूप कम्यूटेशन घाटे में वृद्धि होती है।

MOSFET के प्रत्येक टर्मिनल के साथ एक परजीवी अधिष्ठापन जोड़ा जा सकता है। उनके अलग-अलग प्रभाव हैं:

- गेट इंडक्शन का बहुत कम प्रभाव होता है (यह मानते हुए कि यह कुछ सैकड़ों नैनोहेनरीज़ से कम है), क्योंकि गेट पर वर्तमान ग्रेडिएंट अपेक्षाकृत धीमे हैं। हालाँकि, कुछ मामलों में, गेट इंडक्शन और ट्रांजिस्टर की इनपुट कैपेसिटेंस एक इलेक्ट्रॉनिक थरथरानवाला का निर्माण कर सकते हैं। इससे बचना चाहिए, क्योंकि इसके परिणामस्वरूप बहुत अधिक कम्यूटेशन हानि (डिवाइस के नष्ट होने तक) होती है। एक विशिष्ट डिज़ाइन पर, इस घटना को रोकने के लिए परजीवी अधिष्ठापन को काफी कम रखा जाता है;

- MOSFET चालू होने पर ड्रेन इंडक्शन ड्रेन वोल्टेज को कम कर देता है, इसलिए यह टर्न ऑन घाटे को कम करता है। हालाँकि, चूंकि यह टर्न-ऑफ के दौरान ओवरवॉल्टेज पैदा करता है, इससे टर्न-ऑफ नुकसान बढ़ जाता है;

- स्रोत परजीवी इंडक्शन का व्यवहार ड्रेन इंडक्शन के समान होता है, साथ ही एक प्रतिक्रिया प्रभाव होता है जो कम्यूटेशन को लंबे समय तक बनाए रखता है, जिससे कम्यूटेशन हानि बढ़ जाती है।

- तेज़ टर्न-ऑन की शुरुआत में, स्रोत अधिष्ठापन के कारण, स्रोत पर वोल्टेज (डाई पर) गेट वोल्टेज के साथ-साथ ऊपर कूदने में सक्षम होगा; आंतरिक वीGS वोल्टेज लंबे समय तक कम रहेगा, इसलिए चालू करने में देरी होगी।

- तेजी से टर्न-ऑफ की शुरुआत में, जैसे ही स्रोत इंडक्शन के माध्यम से करंट तेजी से घटता है, परिणामी वोल्टेज नकारात्मक हो जाता है (पैकेज के बाहर लीड के संबंध में) आंतरिक वी बढ़ जाता हैGS वोल्टेज, MOSFET को चालू रखता है, और इसलिए टर्न-ऑफ में देरी करता है।

संचालन की सीमाएं

गेट ऑक्साइड टूटना

गेट ऑक्साइड बहुत पतला (100 एनएम या उससे कम) है, इसलिए यह केवल सीमित वोल्टेज ही बनाए रख सकता है। डेटाशीट में, निर्माता अक्सर अधिकतम गेट टू सोर्स वोल्टेज, लगभग 20 वी बताते हैं, और इस सीमा से अधिक होने पर घटक नष्ट हो सकता है। इसके अलावा, उच्च गेट टू सोर्स वोल्टेज MOSFET के जीवनकाल को काफी कम कर देता है, जिससे R पर कोई लाभ नहीं होता हैDSon कमी।

इस समस्या से निपटने के लिए अक्सर गेट ड्राइवर सर्किट का उपयोग किया जाता है।

स्रोत वोल्टेज के लिए अधिकतम निकास

पावर MOSFETs में अधिकतम निर्दिष्ट ड्रेन टू सोर्स वोल्टेज (बंद होने पर) होता है, जिसके परे हिमस्खलन टूटना हो सकता है। ब्रेकडाउन वोल्टेज से अधिक होने से उपकरण संचालन में बाधा उत्पन्न करता है, संभावित रूप से अत्यधिक बिजली अपव्यय के कारण इसे और अन्य सर्किट तत्वों को नुकसान पहुंचता है।

अधिकतम नाली धारा

ड्रेन करंट आम तौर पर एक निश्चित निर्दिष्ट मान (अधिकतम निरंतर ड्रेन करंट) से नीचे रहना चाहिए। यह बहुत कम समय के लिए उच्च मूल्यों तक पहुंच सकता है (अधिकतम स्पंदित नाली धारा, कभी-कभी विभिन्न पल्स अवधि के लिए निर्दिष्ट)। वायर बॉन्डिंग जैसे आंतरिक घटकों में जूल तापन और धातु की परत में इलेक्ट्रोमाइग्रेशन जैसी अन्य घटनाओं के कारण ड्रेन करंट सीमित होता है।

अधिकतम तापमान

जंक्शन तापमान (टीJ) डिवाइस के विश्वसनीय रूप से कार्य करने के लिए MOSFET का एक निर्दिष्ट अधिकतम मान के अंतर्गत रहना चाहिए, जो MOSFET डाई लेआउट और पैकेजिंग सामग्री द्वारा निर्धारित किया जाता है। मोल्डिंग कंपाउंड और (जहां उपयोग किया जाता है) एपॉक्सी विशेषताओं के कारण पैकेजिंग अक्सर अधिकतम जंक्शन तापमान को सीमित करती है।

अधिकतम परिचालन तापमान का तापमान बिजली अपव्यय और थर्मल प्रतिरोध द्वारा निर्धारित किया जाता है। जंक्शन-टू-केस थर्मल प्रतिरोध डिवाइस और पैकेज के लिए आंतरिक है; केस-टू-एम्बिएंट थर्मल प्रतिरोध काफी हद तक बोर्ड/माउंटिंग लेआउट, हीटसिंकिंग क्षेत्र और वायु/द्रव प्रवाह पर निर्भर है।

बिजली अपव्यय का प्रकार, चाहे निरंतर या स्पंदित, थर्मल द्रव्यमान विशेषताओं के कारण अधिकतम ऑपरेटिंग तापमान को प्रभावित करता है; सामान्य तौर पर, किसी दिए गए बिजली अपव्यय के लिए दालों की आवृत्ति जितनी कम होगी, डिवाइस को ठंडा होने के लिए लंबे अंतराल की अनुमति के कारण अधिकतम ऑपरेटिंग परिवेश का तापमान उतना अधिक होगा। मॉडल, जैसे कि फोस्टर की प्रतिक्रिया प्रमेय, का उपयोग शक्ति क्षणकों से तापमान की गतिशीलता का विश्लेषण करने के लिए किया जा सकता है।

सुरक्षित परिचालन क्षेत्र

सुरक्षित परिचालन क्षेत्र ड्रेन करंट और ड्रेन टू सोर्स वोल्टेज की संयुक्त रेंज को परिभाषित करता है जिसे पावर MOSFET बिना किसी क्षति के संभालने में सक्षम है। इसे इन दो मापदंडों द्वारा परिभाषित विमान में एक क्षेत्र के रूप में रेखांकन द्वारा दर्शाया गया है। ड्रेन करंट और ड्रेन-टू-सोर्स वोल्टेज दोनों को उनके संबंधित अधिकतम मूल्यों से नीचे रहना चाहिए, लेकिन उनका उत्पाद उस अधिकतम बिजली अपव्यय से भी नीचे रहना चाहिए जिसे डिवाइस संभालने में सक्षम है। इस प्रकार, डिवाइस को उसके अधिकतम करंट और अधिकतम वोल्टेज पर एक साथ संचालित नहीं किया जा सकता है।[34]

लैच-अप

पावर MOSFET के समतुल्य सर्किट में एक परजीवी BJT के समानांतर एक MOSFET होता है। यदि BJT चालू हो जाता है, तो इसे बंद नहीं किया जा सकता, क्योंकि गेट का इस पर कोई नियंत्रण नहीं है। इस घटना को लैच-अप के रूप में जाना जाता है, जिससे उपकरण नष्ट हो सकता है। पी-टाइप बॉडी क्षेत्र में वोल्टेज ड्रॉप के कारण BJT को चालू किया जा सकता है। लैच-अप से बचने के लिए, डिवाइस पैकेज के भीतर बॉडी और स्रोत को आमतौर पर शॉर्ट-सर्किट किया जाता है।

प्रौद्योगिकी

लेआउट

सेलुलर संरचना

जैसा कि ऊपर बताया गया है, पावर MOSFET की वर्तमान हैंडलिंग क्षमता उसके गेट चैनल की चौड़ाई से निर्धारित होती है। गेट चैनल की चौड़ाई चित्रित क्रॉस-सेक्शन का तीसरा (जेड-अक्ष) आयाम है।

लागत और आकार को कम करने के लिए, ट्रांजिस्टर के डाई क्षेत्र के आकार को यथासंभव छोटा रखना मूल्यवान है। इसलिए, चैनल सतह क्षेत्र की चौड़ाई बढ़ाने, यानी चैनल घनत्व बढ़ाने के लिए अनुकूलन विकसित किए गए हैं। इनमें मुख्य रूप से MOSFET डाई के पूरे क्षेत्र में दोहराई जाने वाली सेलुलर संरचनाएं बनाना शामिल है। इन कोशिकाओं के लिए कई आकार प्रस्तावित किए गए हैं, जिनमें से सबसे प्रसिद्ध अंतर्राष्ट्रीय रेक्टिफायर के HEXFET उपकरणों में उपयोग किया जाने वाला हेक्सागोनल आकार है।

चैनल घनत्व बढ़ाने का दूसरा तरीका प्राथमिक संरचना के आकार को कम करना है। यह किसी दिए गए सतह क्षेत्र में अधिक कोशिकाओं की अनुमति देता है, और इसलिए अधिक चैनल चौड़ाई। हालाँकि, जैसे-जैसे कोशिका का आकार सिकुड़ता है, प्रत्येक कोशिका का उचित संपर्क सुनिश्चित करना अधिक कठिन हो जाता है। इसे दूर करने के लिए अक्सर एक पट्टी संरचना का उपयोग किया जाता है (चित्र देखें)। यह चैनल घनत्व के संदर्भ में समकक्ष रिज़ॉल्यूशन की सेलुलर संरचना से कम कुशल है, लेकिन छोटी पिच का सामना कर सकता है। समतल धारी संरचना का एक अन्य लाभ यह है कि यह हिमस्खलन टूटने की घटनाओं के दौरान विफलता के प्रति कम संवेदनशील होता है जिसमें परजीवी द्विध्रुवी ट्रांजिस्टर पर्याप्त आगे के पूर्वाग्रह से चालू होता है। सेलुलर संरचना में, यदि किसी एक कोशिका के स्रोत टर्मिनल से खराब तरीके से संपर्क किया जाता है, तो यह अधिक संभावना हो जाती है कि हिमस्खलन टूटने की घटना के दौरान परजीवी द्विध्रुवी ट्रांजिस्टर बंद हो जाता है। इस वजह से, तलीय धारी संरचना का उपयोग करने वाले MOSFETs केवल अत्यधिक थर्मल तनाव के कारण हिमस्खलन टूटने के दौरान विफल हो सकते हैं।[35]

संरचनाएं

पी-सब्सट्रेट पावर एमओएसएफईटी

एक पी-सब्सट्रेट एमओएसएफईटी (अक्सर पीएमओएस कहा जाता है) एक एमओएसएफईटी है जिसमें विपरीत डोपिंग प्रकार होते हैं (चित्र 1 में क्रॉस-सेक्शन में पी के बजाय एन और एन के बजाय पी)। यह MOSFET P के साथ P-प्रकार सब्सट्रेट का उपयोग करके बनाया गया है−एपिटैक्सी. जैसे ही चैनल एन-क्षेत्र में बैठता है, यह ट्रांजिस्टर एक नकारात्मक गेट टू सोर्स वोल्टेज द्वारा चालू हो जाता है। यह इसे हिरन कनवर्टर में वांछनीय बनाता है, जहां स्विच का एक टर्मिनल इनपुट वोल्टेज के उच्च पक्ष से जुड़ा होता है: एन-एमओएसएफईटी के साथ, इस कॉन्फ़िगरेशन के लिए गेट पर बराबर वोल्टेज लागू करने की आवश्यकता होती है , जबकि कोई वोल्टेज खत्म नहीं हुआ P-MOSFET के साथ आवश्यक है।

इस प्रकार के MOSFET का मुख्य नुकसान खराब ऑन-स्टेट प्रदर्शन है, क्योंकि यह चार्ज वाहक के रूप में छेद का उपयोग करता है, जिसमें इलेक्ट्रॉनों की तुलना में बहुत कम इलेक्ट्रॉन गतिशीलता होती है। चूंकि विद्युत प्रतिरोधकता और चालकता सीधे गतिशीलता से संबंधित है, किसी दिए गए पीएमओएस डिवाइस में एक होगा समान आयाम वाले N-MOSFET से तीन गुना अधिक।

वीएमओएस

वीएमओएस संरचना में गेट क्षेत्र पर एक वी-ग्रूव है और इसका उपयोग पहले वाणिज्यिक उपकरणों के लिए किया गया था।[36]

यूएमओएस

इस पावर MOSFET संरचना में, जिसे ट्रेंच-एमओएस भी कहा जाता है, गेट इलेक्ट्रोड को सिलिकॉन में खोदी गई खाई में दफनाया जाता है। इसका परिणाम एक ऊर्ध्वाधर चैनल होता है। संरचना का मुख्य हित जेएफईटी प्रभाव की अनुपस्थिति है। संरचना का नाम खाई के यू-आकार से आता है।

सुपर-जंक्शन डीप-ट्रेंच तकनीक

विशेष रूप से 500 वी से अधिक वोल्टेज के लिए, कुछ निर्माताओं, जिनमें इसके CoolMOS उत्पादों के साथ Infineon Technologies शामिल हैं, ने चार्ज क्षतिपूर्ति सिद्धांत का उपयोग करना शुरू कर दिया है। इस तकनीक के साथ, एपिटैक्सियल परत का प्रतिरोध, जो उच्च-वोल्टेज MOSFETs के डिवाइस प्रतिरोध में सबसे बड़ा योगदानकर्ता (95% से अधिक) है, को 5 से अधिक के कारक से कम किया जा सकता है।

सुपर-जंक्शन एमओएसएफईटी की विनिर्माण दक्षता और विश्वसनीयता में सुधार करने की मांग करते हुए, रेनेसा इलेक्ट्रॉनिक्स ने एक गहरी-ट्रेंच प्रक्रिया तकनीक के साथ एक सुपर-जंक्शन संरचना विकसित की। इस तकनीक में पी-प्रकार के क्षेत्र बनाने के लिए कम अशुद्धता वाले एन-प्रकार की सामग्री में खाइयां खोदना शामिल है। यह प्रक्रिया बहु-स्तरीय एपिटैक्सियल विकास दृष्टिकोण में निहित समस्याओं पर काबू पाती है और इसके परिणामस्वरूप बेहद कम प्रतिरोध और कम आंतरिक क्षमता होती है।

बढ़े हुए पी-एन जंक्शन क्षेत्र के कारण, एक सुपर-जंक्शन संरचना में पारंपरिक प्लानर पावर MOSFET की तुलना में कम रिवर्स रिकवरी समय होता है, लेकिन बड़ा रिवर्स रिकवरी करंट होता है।

यह भी देखें

- विद्युत रोधित गेट द्विध्रुवी ट्रांजिस्टर

- मॉसफेट

- बिजली के इलेक्ट्रॉनिक्स

- पावर सेमीकंडक्टर डिवाइस

संदर्भ

- ↑ IRLZ24N, 55V N-Channel Power MOSFET, TO-220AB package; Infineon.

- ↑ Irwin, J. David (1997). औद्योगिक इलेक्ट्रॉनिक्स हैंडबुक. CRC Press. p. 218. ISBN 9780849383434.

- ↑ 3.0 3.1 3.2 "पावर MOSFET मूल बातें" (PDF). Alpha & Omega Semiconductor. Retrieved 29 July 2019.

- ↑ 4.0 4.1 Duncan, Ben (1996). उच्च प्रदर्शन ऑडियो पावर एम्पलीफायर. Elsevier. pp. 178–81. ISBN 9780080508047.

- ↑ "GaN के साथ पावर घनत्व पर पुनर्विचार करें". Electronic Design. 21 April 2017. Retrieved 23 July 2019.

- ↑ Oxner, E. S. (1988). Fet प्रौद्योगिकी और अनुप्रयोग. CRC Press. p. 18. ISBN 9780824780500.

- ↑ 7.0 7.1 7.2 7.3 "असतत अर्धचालकों में प्रगति जारी है". Power Electronics Technology. Informa: 52–6. September 2005. Archived (PDF) from the original on 22 March 2006. Retrieved 31 July 2019.

- ↑ Tarui, Y.; Hayashi, Y.; Sekigawa, Toshihiro (September 1969). "Diffusion Self-Aligned MOST; A New Approach for High Speed Device". Proceedings of the 1st Conference on Solid State Devices. doi:10.7567/SSDM.1969.4-1. S2CID 184290914.

- ↑ McLintock, G. A.; Thomas, R. E. (December 1972). स्व-संरेखित द्वारों के साथ डबल-डिफ्यूज्ड MOST की मॉडलिंग. 1972 International Electron Devices Meeting. pp. 24–26. doi:10.1109/IEDM.1972.249241.

- ↑ 10.0 10.1 10.2 10.3 Duncan, Ben (1996). उच्च प्रदर्शन ऑडियो पावर एम्पलीफायर. Elsevier. pp. 177–8, 406. ISBN 9780080508047.

- ↑ 11.0 11.1 Baliga, B. Jayant (2005). सिलिकॉन आरएफ पावर मॉसफेट्स. World Scientific. ISBN 9789812561213.

- ↑ 12.0 12.1 Asif, Saad (2018). 5G Mobile Communications: Concepts and Technologies. CRC Press. p. 134. ISBN 9780429881343.

- ↑ "उत्तरी अमेरिका के लिए SEMI पुरस्कार". SEMI. Archived from the original on 5 August 2016. Retrieved 5 August 2016.

- ↑ 14.0 14.1 "इंटरनेशनल रेक्टिफायर के एलेक्स लिडो और टॉम हरमन को इंजीनियरिंग हॉल ऑफ फेम में शामिल किया गया". Business Wire. 14 September 2004. Retrieved 31 July 2019.

- ↑ Baliga, B. Jayant (2015). The IGBT Device: Physics, Design and Applications of the Insulated Gate Bipolar Transistor. William Andrew. pp. xxviii, 5–11. ISBN 9781455731534.

- ↑ 16.0 16.1 "MDmesh: 20 Years of Superjunction STPOWER MOSFETs, A Story About Innovation". STMicroelectronics. 11 September 2019. Retrieved 2 November 2019.

- ↑ US Patent 4,754,310

- ↑ "Power Transistor Market Will Cross $13.0 Billion in 2011". IC Insights. June 21, 2011. Retrieved 15 October 2019.

- ↑ Carbone, James (September–October 2018). "Buyers can expect 30-week lead times and higher tags to continue for MOSFETs" (PDF). Electronics Sourcing: 18–19.

- ↑ Williams, Richard K.; Darwish, Mohamed N.; Blanchard, Richard A.; Siemieniec, Ralf; Rutter, Phil; Kawaguchi, Yusuke (23 February 2017). "The Trench Power MOSFET: Part I—History, Technology, and Prospects". IEEE Transactions on Electron Devices. 64 (3): 674–691. Bibcode:2017ITED...64..674W. doi:10.1109/TED.2017.2653239. S2CID 20730536.

- ↑ 21.0 21.1 "MOSFET". Infineon Technologies. Retrieved 24 December 2019.

- ↑ "Infineon EiceDRIVER गेट ड्राइवर ICs" (PDF). Infineon. August 2019. Retrieved 26 December 2019.

- ↑ "आरएफ डीएमओएस ट्रांजिस्टर". STMicroelectronics. Retrieved 22 December 2019.

- ↑ "AN1256: Application note – High-power RF MOSFET targets VHF applications" (PDF). ST Microelectronics. July 2007. Retrieved 22 December 2019.

- ↑ Emadi, Ali (2017). ऑटोमोटिव पावर इलेक्ट्रॉनिक्स और मोटर ड्राइव की हैंडबुक. CRC Press. p. 117. ISBN 9781420028157.

- ↑ "परिवहन के लिए इन्फिनियॉन समाधान" (PDF). Infineon. June 2013. Retrieved 23 December 2019.

- ↑ "HITFETs: Smart, Protected MOSFETs" (PDF). Infineon. Retrieved 23 December 2019.

- ↑ "सीएमओएस सेंसर फोन कैमरे, एचडी वीडियो को सक्षम करते हैं". NASA Spinoff. NASA. Retrieved 6 November 2019.

- ↑ Veendrick, Harry J. M. (2017). Nanometer CMOS ICs: From Basics to ASICs. Springer. p. 245. ISBN 9783319475974.

- ↑ Korec, Jacek (2011). Low Voltage Power MOSFETs: Design, Performance and Applications. Springer Science+Business Media. pp. 9–14. ISBN 978-1-4419-9320-5.

- ↑ "ऑटोमोटिव पावर MOSFETs" (PDF). Fuji Electric. Retrieved 10 August 2019.

- ↑ Williams, R. K.; Darwish, M. N.; Blanchard, R. A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. (2017). "The Trench Power MOSFET—Part II: Application Specific VDMOS, LDMOS, Packaging, Reliability". IEEE Transactions on Electron Devices. 64 (3): 692–712. Bibcode:2017ITED...64..692W. doi:10.1109/TED.2017.2655149. ISSN 0018-9383. S2CID 38550249.

- ↑ Simon M. Sze, Modern semiconductor device physics, John Wiley and Sons, Inc 1998 ISBN 0-471-15237-4

- ↑ Pierre Aloïsi, Les transistors MOS de puissance in Interrupteurs électroniques de puissance, traite EGEM, under the direction of Robert Perret, Lavoisier, Paris, 2003 [in French] ISBN 2-7462-0671-4

- ↑ Murray, Anthony F. J.; McDonald, Tim; Davis, Harold; Cao, Joe; Spring, Kyle. "Extremely Rugged MOSFET Technology with Ultra-low RDS(on) Specified for A Broad Range of EAR Conditions" (PDF). International Rectifier. Retrieved 26 April 2022.

- ↑ Duncan A. Grant, John Gowar POWER MOSFETS: Theory and Applications John Wiley and Sons, Inc ISBN 0-471-82867-X , 1989

अग्रिम पठन

- Baliga, B. Jayant (1996). Power Semiconductor Devices. PWS Publishing. ISBN 9780534940980.