डबल-प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट: Difference between revisions

No edit summary |

No edit summary |

||

| (3 intermediate revisions by 3 users not shown) | |||

| Line 2: | Line 2: | ||

'''डबल-प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट''' (जिसे कभी-कभी '''एफपी64''' या '''फ्लोट64''' भी कहा जाता है) एक [[फ़्लोटिंग-पॉइंट अंकगणित|फ़्लोटिंग-पॉइंट]] [[कंप्यूटर नंबर प्रारूप|नंबर फॉर्मेट]] है, जो प्रायः कंप्यूटर मेमोरी में 64[[ अंश | बिट्स]] रखता है; यह एक फ़्लोटिंग [[मूलांक बिंदु|रेडिक्स बिंदु]] का उपयोग करके संख्यात्मक मानों की एक विस्तृत डायनामिक श्रृंखला का निरूपण करता है। | '''डबल-प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट''' (जिसे कभी-कभी '''एफपी64''' या '''फ्लोट64''' भी कहा जाता है) एक [[फ़्लोटिंग-पॉइंट अंकगणित|फ़्लोटिंग-पॉइंट]] [[कंप्यूटर नंबर प्रारूप|नंबर फॉर्मेट]] है, जो प्रायः कंप्यूटर मेमोरी में 64[[ अंश | बिट्स]] रखता है; यह एक फ़्लोटिंग [[मूलांक बिंदु|रेडिक्स बिंदु]] का उपयोग करके संख्यात्मक मानों की एक विस्तृत डायनामिक श्रृंखला का निरूपण करता है। | ||

फ़्लोटिंग पॉइंट का उपयोग भिन्नात्मक मानों को दर्शाने के लिए किया जाता है, या जब [[निश्चित-बिंदु अंकगणित|निश्चित-बिंदु]] (समान बिट | फ़्लोटिंग पॉइंट का उपयोग भिन्नात्मक मानों को दर्शाने के लिए किया जाता है, या जब [[निश्चित-बिंदु अंकगणित|निश्चित-बिंदु]] (समान बिट विड्थ) द्वारा प्रदान की जाने वाली व्यापक रेंज की आवश्यकता होती है, भले ही प्रिसिजन की लागत पर हो। डबल प्रिसिजन को तब चुना जा सकता है जब [[एकल-परिशुद्धता फ़्लोटिंग-पॉइंट प्रारूप|एकल-प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट]] की रेंज या प्रिसिजन अपर्याप्त होगी। | ||

[[आईईईई 754-2008|आईईई 754-2008]] [[मानकीकरण]] में, 64-बिट बेस-2 फॉर्मेट को आधिकारिक रूप से '''बाइनरी64''' कहा जाता है; आईईईई 754-1985 में इसे '''डबल''' कहा गया। आईईईई 754 अतिरिक्त फ़्लोटिंग-पॉइंट फॉर्मेट निर्दिष्ट करता है, जिसमें 32-बिट बेस-2 ''एकल प्रिसिजन'' और, हाल ही में, बेस-10 निरूपण सम्मिलित हैं। | [[आईईईई 754-2008|आईईई 754-2008]] [[मानकीकरण]] में, 64-बिट बेस-2 फॉर्मेट को आधिकारिक रूप से '''बाइनरी64''' कहा जाता है; आईईईई 754-1985 में इसे '''डबल''' कहा गया। आईईईई 754 अतिरिक्त फ़्लोटिंग-पॉइंट फॉर्मेट निर्दिष्ट करता है, जिसमें 32-बिट बेस-2 ''एकल प्रिसिजन'' और, हाल ही में, बेस-10 निरूपण सम्मिलित हैं। | ||

सिंगल और डबल-प्रिसिजन फ़्लोटिंग-पॉइंट डेटा | सिंगल और डबल-प्रिसिजन फ़्लोटिंग-पॉइंट डेटा टाइप प्रदान करने वाली पहली [[प्रोग्रामिंग भाषा]]ओं में से एक [[फोरट्रान]] थी। [[आईईईई 754-1985]] को व्यापक रूप से अपनाने से पहले, फ्लोटिंग-पॉइंट डेटा टाइप का निरूपण और गुण [[कंप्यूटर निर्माता]] और कंप्यूटर मॉडल और प्रोग्रामिंग-भाषा कार्यान्वयनकर्ताओं द्वारा किए गए निर्णयों पर निर्भर थे। उदाहरण के लिए, [[GW-BASIC|जीडब्ल्यू-बेसिक]] का डबल-प्रिसिजन डेटा टाइप 64-बिट एमबीएफ फ़्लोटिंग-पॉइंट फॉर्मेट था। | ||

{{Floating-point}} | {{Floating-point}} | ||

| Line 14: | Line 14: | ||

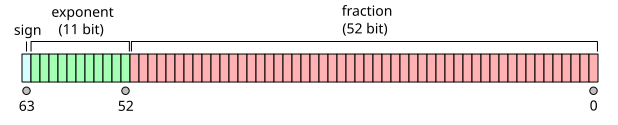

* [[प्रतिपादक|घातांक]]: 11 बिट्स | * [[प्रतिपादक|घातांक]]: 11 बिट्स | ||

* [[महत्व|अपूर्णांश]] [[परिशुद्धता (अंकगणित)|प्रिसिजन]]: 53 बिट्स (52 स्पष्ट रूप से संग्रहीत) | * [[महत्व|अपूर्णांश]] [[परिशुद्धता (अंकगणित)|प्रिसिजन]]: 53 बिट्स (52 स्पष्ट रूप से संग्रहीत) | ||

साइन बिट संख्या का | साइन बिट संख्या का साइन निर्धारित करता है (इसमें यह भी सम्मिलित है कि जब यह संख्या जीरो है, जो साइन्ड है)। | ||

घातांक क्षेत्र पूर्वाग्रहित रूप में 0 से 2047 तक 11-बिट | घातांक क्षेत्र पूर्वाग्रहित रूप में 0 से 2047 तक 11-बिट अनसाइन्ड इन्टिजर है: 1023 का घातांक मान वास्तविक जीरो का निरूपण करता है। घातांक -1022 से +1023 तक होते हैं क्योंकि -1023 (सभी 0s) और +1024 (सभी 1s) के घातांक विशेष संख्याओं के लिए आरक्षित होते हैं। | ||

53-बिट अपूर्णांश प्रिसिजन 15 से 17 सार्थक | 53-बिट अपूर्णांश प्रिसिजन 15 से 17 सार्थक डेसीमल अंकों की प्रिसिजन (2<sup>−53</sup> ≈ 1.11 × 10<sup>−16</sup>) देती है। यदि अधिकतम 15 सार्थक अंकों वाली एक डेसीमल स्ट्रिंग को सामान्य संख्या देते हुए आईईईई 754 डबल-प्रिसिजन फॉर्मेट में परिवर्तित किया जाता है, और फिर समान अंकों की संख्या के साथ डेसीमल स्ट्रिंग में परिवर्तित किया जाता है, तो अंतिम परिणाम मूल स्ट्रिंग से सुमेलित होना चाहिए। यदि आईईईई 754 डबल-प्रिसिजन संख्या को कम से कम 17 सार्थक अंकों के साथ डेसीमल स्ट्रिंग में परिवर्तित किया जाता है, और फिर वापस डबल-प्रिसिजन निरूपण में परिवर्तित किया जाता है, तो अंतिम परिणाम मूल संख्या से सुमेलित होना चाहिए।<ref name="whyieee">{{cite web|url=http://www.cs.berkeley.edu/~wkahan/ieee754status/IEEE754.PDF|title=Lecture Notes on the Status of IEEE Standard 754 for Binary Floating-Point Arithmetic|author=William Kahan|date=1 October 1997|url-status=live|archive-url=https://web.archive.org/web/20120208075518/http://www.cs.berkeley.edu/~wkahan/ieee754status/IEEE754.PDF|archive-date=8 February 2012}}</ref> | ||

फॉर्मेट को अपूर्णांश के साथ लिखा गया है और इसमें मान 1 का एक अंतर्निहित इन्टिजर बिट है (विशेष डेटा को छोड़कर, नीचे घातांक एन्कोडिंग देखें)। फ्रैक्शन (एफ) के 52 बिट्स के मेमोरी फॉर्मेट में प्रदर्शित होने के साथ, कुल प्रिसिजन 53 बिट्स (लगभग 16 | फॉर्मेट को अपूर्णांश के साथ लिखा गया है और इसमें मान 1 का एक अंतर्निहित इन्टिजर बिट है (विशेष डेटा को छोड़कर, नीचे घातांक एन्कोडिंग देखें)। फ्रैक्शन (एफ) के 52 बिट्स के मेमोरी फॉर्मेट में प्रदर्शित होने के साथ, कुल प्रिसिजन 53 बिट्स (लगभग 16 डेसीमल अंक, 53 log<sub>10</sub>(2) ≈ 15.955) है। बिट्स को इस प्रकार रखा गया है: | ||

[[File:IEEE 754 Double Floating Point Format.svg]]किसी दिए गए | [[File:IEEE 754 Double Floating Point Format.svg]]किसी दिए गए एक्सपोनेंट पूर्वाग्रह <math>e</math> और एक 52-बिट फ्रैक्शन के साथ दिए गए 64-बिट डबल-प्रिसिजन डेटम द्वारा ग्रहण किया गया वास्तविक मान है | ||

: <math> (-1)^{\text{sign}}(1.b_{51}b_{50}...b_{0})_2 \times 2^{e-1023} </math> | : <math> (-1)^{\text{sign}}(1.b_{51}b_{50}...b_{0})_2 \times 2^{e-1023} </math> | ||

या | या | ||

: <math> (-1)^{\text{sign}}\left(1 + \sum_{i=1}^{52} b_{52-i} 2^{-i} \right)\times 2^{e-1023} </math> | : <math> (-1)^{\text{sign}}\left(1 + \sum_{i=1}^{52} b_{52-i} 2^{-i} \right)\times 2^{e-1023} </math> | ||

2<sup>52</sup>=4,503,599,627,370,496 और 2<sup>53</sup>=9,007,199,254,740,992 के बीच निरूपण योग्य संख्याएँ बिल्कुल इन्टिजर हैं। अगली | 2<sup>52</sup>=4,503,599,627,370,496 और 2<sup>53</sup>=9,007,199,254,740,992 के बीच निरूपण योग्य संख्याएँ बिल्कुल इन्टिजर हैं। अगली रेंज के लिए, 2<sup>53</sup> से 2<sup>54</sup> तक, हर संख्या को 2 से गुणा किया जाता है, इसलिए निरूपण योग्य संख्याएँ सम संख्याएँ हैं, आदि। इसके विपरीत, 2<sup>51</sup>से 2<sup>52</sup> तक की पिछली रेंज के लिए, अंतर 0.5 है, आदि। | ||

2<sup>n</sup>से 2<sup>n+1</sup> की | 2<sup>n</sup>से 2<sup>n+1</sup> की रेंज में संख्याओं के अंश के रूप में अंतर 2<sup>n−52</sup> है। किसी संख्या को निकटतम निरूपण योग्य संख्या ([[मशीन ईपीएसलॉन|मशीन एप्सिलॉन]]) में पूर्णांकित करते समय अधिकतम रिलेटिव रॉउंडिंग त्रुटि 2<sup>−53</sup> होती है। | ||

घातांक की 11 बिट | घातांक की 11 बिट विड्थ पूर्ण 15-17 डेसीमल अंकों की प्रिसिजन के साथ 10<sup>−308</sup>और 10<sup>308</sup> के बीच संख्याओं के निरूपण की अनुमति देती है। प्रिसिजन से सन्धि करके, असामान्य निरूपण लगभग 5 × 10<sup>−324</sup> तक के छोटे मानों की भी अनुमति देता है। | ||

===घातांक एन्कोडिंग=== | ===घातांक एन्कोडिंग=== | ||

डबल-प्रिसिजन बाइनरी फ़्लोटिंग-पॉइंट एक्सपोनेंट को [[ऑफसेट-बाइनरी]] प्रतिरूपण का उपयोग करके एन्कोड किया गया है, जिसमें | डबल-प्रिसिजन बाइनरी फ़्लोटिंग-पॉइंट एक्सपोनेंट को [[ऑफसेट-बाइनरी]] प्रतिरूपण का उपयोग करके एन्कोड किया गया है, जिसमें जीरो ऑफसेट 1023 है; आईईईई 754 मानक में एक्सपोनेंट पूर्वाग्रह के रूप में भी जाना जाता है। ऐसे अभ्यावेदन के उदाहरण होंगे: | ||

{| | {| | ||

|- | |- | ||

| Line 44: | Line 44: | ||

| | | | ||

|<math>2^{1023-1023}=2^0</math> | |<math>2^{1023-1023}=2^0</math> | ||

|( | |(जीरो ऑफसेट) | ||

|- | |- | ||

|''e'' =<code>10000000101<sub>2</sub></code>=<code>405<sub>16</sub></code>=1029: | |''e'' =<code>10000000101<sub>2</sub></code>=<code>405<sub>16</sub></code>=1029: | ||

| Line 57: | Line 57: | ||

|} | |} | ||

घातांक<code>000<sub>16</sub></code> और <code>7ff<sub>16</sub></code> का एक विशेष अर्थ है: | घातांक<code>000<sub>16</sub></code> और <code>7ff<sub>16</sub></code> का एक विशेष अर्थ है: | ||

* <code>00000000000<sub>2</sub></code>=<code>000<sub>16</sub></code> का उपयोग एक | * <code>00000000000<sub>2</sub></code>=<code>000<sub>16</sub></code> का उपयोग एक साइन्ड जीरो (यदि ''F'' = 0) और [[असामान्य संख्या]]ओं (यदि ''F'' ≠ 0) को दर्शाने के लिए किया जाता है; और | ||

* <code>11111111111<sub>2</sub></code>=<code>7ff<sub>16</sub></code> का उपयोग ∞ (यदि F = 0) और [[NaN|एनएएन]] (यदि F ≠ 0) को दर्शाने के लिए किया जाता है, | * <code>11111111111<sub>2</sub></code>=<code>7ff<sub>16</sub></code> का उपयोग ∞ (यदि F = 0) और [[NaN|एनएएन]] (यदि F ≠ 0) को दर्शाने के लिए किया जाता है, | ||

जहाँ F अपूर्णांश का भिन्नात्मक भाग है। सभी बिट पैटर्न वैध एन्कोडिंग हैं। | जहाँ F अपूर्णांश का भिन्नात्मक भाग है। सभी बिट पैटर्न वैध एन्कोडिंग हैं। | ||

| Line 72: | Line 72: | ||

हालांकि कई प्रोसेसर सभी प्रकार के डेटा (इन्टिजर, फ़्लोटिंग पॉइंट) के लिए छोटे-एंडियन स्टोरेज का उपयोग करते हैं, ऐसे कई हार्डवेयर आर्किटेक्चर हैं जहां फ़्लोटिंग-पॉइंट संख्याओं को बड़े-एंडियन रूप में दर्शाया जाता है जबकि इन्टिजर को छोटे-एंडियन रूप में दर्शाया जाता है। ऐसे एआरएम प्रोसेसर हैं जिनमें डबल-प्रिसिजन संख्याओं के लिए मिश्रित-एंडियन फ़्लोटिंग-पॉइंट निरूपण होता है: दो 32-बिट शब्दों में से प्रत्येक को छोटे-एंडियन के रूप में संग्रहीत किया जाता है, लेकिन सबसे महत्वपूर्ण शब्द पहले संग्रहीत किया जाता है। वीएएक्स फ़्लोटिंग पॉइंट छोटे-एंडियन 16-बिट शब्दों को बड़े-एंडियन क्रम में संग्रहीत करता है। चूँकि ऐसे कई फ़्लोटिंग-पॉइंट फॉर्मेट हैं जिनके लिए कोई नेटवर्क मानक निरूपण नहीं है, एक्सडीआर मानक इसके निरूपण के रूप में बिग-एंडियन आईईईई 754 का उपयोग करता है। इसलिए यह अजीब लग सकता है कि व्यापक आईईईई 754फ़्लोटिंग-पॉइंट मानक एंडियननेस निर्दिष्ट नहीं करता है। सैद्धांतिक रूप से, इसका मतलब यह है कि एक मशीन द्वारा लिखा गया मानक आईईईई फ़्लोटिंग-पॉइंट डेटा भी दूसरे द्वारा पढ़ने योग्य नहीं हो सकता है। हालाँकि, आधुनिक मानक कंप्यूटरों पर (यानी, आईईईई 754 को कार्यान्वित करते हुए), कोई सुरक्षित रूप से मान सकता है कि फ़्लोटिंग-पॉइंट संख्याओं के लिए एंडियननेस इन्टिजर के समान ही है, जिससे डेटा टाइप की परवाह किए बिना रूपांतरण सीधा हो जाता है। विशेष फ़्लोटिंग-पॉइंट फॉर्मेटों का उपयोग करने वाले छोटे एम्बेडेड सिस्टम एक और विषय हो सकता हैं। | हालांकि कई प्रोसेसर सभी प्रकार के डेटा (इन्टिजर, फ़्लोटिंग पॉइंट) के लिए छोटे-एंडियन स्टोरेज का उपयोग करते हैं, ऐसे कई हार्डवेयर आर्किटेक्चर हैं जहां फ़्लोटिंग-पॉइंट संख्याओं को बड़े-एंडियन रूप में दर्शाया जाता है जबकि इन्टिजर को छोटे-एंडियन रूप में दर्शाया जाता है। ऐसे एआरएम प्रोसेसर हैं जिनमें डबल-प्रिसिजन संख्याओं के लिए मिश्रित-एंडियन फ़्लोटिंग-पॉइंट निरूपण होता है: दो 32-बिट शब्दों में से प्रत्येक को छोटे-एंडियन के रूप में संग्रहीत किया जाता है, लेकिन सबसे महत्वपूर्ण शब्द पहले संग्रहीत किया जाता है। वीएएक्स फ़्लोटिंग पॉइंट छोटे-एंडियन 16-बिट शब्दों को बड़े-एंडियन क्रम में संग्रहीत करता है। चूँकि ऐसे कई फ़्लोटिंग-पॉइंट फॉर्मेट हैं जिनके लिए कोई नेटवर्क मानक निरूपण नहीं है, एक्सडीआर मानक इसके निरूपण के रूप में बिग-एंडियन आईईईई 754 का उपयोग करता है। इसलिए यह अजीब लग सकता है कि व्यापक आईईईई 754फ़्लोटिंग-पॉइंट मानक एंडियननेस निर्दिष्ट नहीं करता है। सैद्धांतिक रूप से, इसका मतलब यह है कि एक मशीन द्वारा लिखा गया मानक आईईईई फ़्लोटिंग-पॉइंट डेटा भी दूसरे द्वारा पढ़ने योग्य नहीं हो सकता है। हालाँकि, आधुनिक मानक कंप्यूटरों पर (यानी, आईईईई 754 को कार्यान्वित करते हुए), कोई सुरक्षित रूप से मान सकता है कि फ़्लोटिंग-पॉइंट संख्याओं के लिए एंडियननेस इन्टिजर के समान ही है, जिससे डेटा टाइप की परवाह किए बिना रूपांतरण सीधा हो जाता है। विशेष फ़्लोटिंग-पॉइंट फॉर्मेटों का उपयोग करने वाले छोटे एम्बेडेड सिस्टम एक और विषय हो सकता हैं। | ||

=== | ===डबल-प्रिसिजन उदाहरण=== | ||

{| style="background-color: #f8f9fa; margin: 1em 0; border: 1px solid #eaecf0; font-family:monospace; white-space:nowrap;" | {| style="background-color: #f8f9fa; margin: 1em 0; border: 1px solid #eaecf0; font-family:monospace; white-space:nowrap;" | ||

|- | |- | ||

| Line 139: | Line 139: | ||

क्यूएनएएन और एसएनएएन की एन्कोडिंग [[आईईईई फ़्लोटिंग पॉइंट|आईईईई 754]] में पूरी तरह से निर्दिष्ट नहीं हैं और प्रोसेसर पर निर्भर करती हैं। अधिकांश प्रोसेसर, जैसे कि x[[86]] फैमिली और [[एआरएम वास्तुकला|एआरएम]] फैमिली प्रोसेसर, एक क्वाइट एनएएन को इंगित करने के लिए अपूर्णांश क्षेत्र के सबसे महत्वपूर्ण बिट का उपयोग करते हैं; आईईईई 754 द्वारा इसकी अनुशंसा की जाती है। [[PA-RISC|पीए-आरआईएससी]] प्रोसेसर सिग्नलिंग एनएएन को इंगित करने के लिए बिट का उपयोग करते हैं। | क्यूएनएएन और एसएनएएन की एन्कोडिंग [[आईईईई फ़्लोटिंग पॉइंट|आईईईई 754]] में पूरी तरह से निर्दिष्ट नहीं हैं और प्रोसेसर पर निर्भर करती हैं। अधिकांश प्रोसेसर, जैसे कि x[[86]] फैमिली और [[एआरएम वास्तुकला|एआरएम]] फैमिली प्रोसेसर, एक क्वाइट एनएएन को इंगित करने के लिए अपूर्णांश क्षेत्र के सबसे महत्वपूर्ण बिट का उपयोग करते हैं; आईईईई 754 द्वारा इसकी अनुशंसा की जाती है। [[PA-RISC|पीए-आरआईएससी]] प्रोसेसर सिग्नलिंग एनएएन को इंगित करने के लिए बिट का उपयोग करते हैं। | ||

डिफ़ॉल्ट रूप से, अपूर्णांश में बिट्स की विषम संख्या के कारण, [[एकल परिशुद्धता|एकल प्रिसिजन]] की तरह ऊपर की | डिफ़ॉल्ट रूप से, अपूर्णांश में बिट्स की विषम संख्या के कारण, [[एकल परिशुद्धता|एकल प्रिसिजन]] की तरह ऊपर की बदले <sup>1</sup>/<sub>3</sub> राउंड नीचे होता है। | ||

और अधिक विस्तार में: | और अधिक विस्तार में: | ||

हेक्साडेसिमल निरूपण को देखते हुए 3FD5 5555 5555 5555<sub>16</sub>, | हेक्साडेसिमल निरूपण को देखते हुए 3FD5 5555 5555 5555<sub>16</sub>, | ||

साइन = 0 | |||

घातांक = 3FD<sub>16</sub> =1021 | घातांक = 3FD<sub>16</sub> =1021 | ||

घातांक पूर्वाग्रह = 1023 (स्थिर मान; ऊपर देखें) | घातांक पूर्वाग्रह = 1023 (स्थिर मान; ऊपर देखें) | ||

भिन्न = 5 5555 5555 5555<sub>16</sub> | भिन्न = 5 5555 5555 5555<sub>16</sub> | ||

मान = 2<sup>(घातांक - घातांक पूर्वाग्रह)</sup> × 1.अंश - ध्यान दें कि भिन्न को यहां | मान = 2<sup>(घातांक - घातांक पूर्वाग्रह)</sup> × 1.अंश - ध्यान दें कि भिन्न को यहां डेसीमल में परिवर्तित नहीं किया जाना चाहिए | ||

= 2<sup>−2</sup> × (15 5555 5555 5555<sub>16</sub> × 2<sup>−52</sup>) | = 2<sup>−2</sup> × (15 5555 5555 5555<sub>16</sub> × 2<sup>−52</sup>) | ||

= 2<sup>−54</sup> × 15 5555 5555 5555<sub>16</sub> | = 2<sup>−54</sup> × 15 5555 5555 5555<sub>16</sub> | ||

| Line 156: | Line 156: | ||

डबल-प्रिसिजन फ़्लोटिंग-पॉइंट वेरिएबल्स का उपयोग प्रायः उनके एकल प्रिसिजन समकक्षों के साथ काम करने की तुलना में धीमा होता है। कंप्यूटिंग का एक क्षेत्र जहां यह एक विशेष विषय है, जीपीयू पर चलने वाला समानांतर कोड है। उदाहरण के लिए,[[ NVIDIA | एनवीडिया]] के [[CUDA|क्यूडा]] प्लेटफ़ॉर्म का उपयोग करते समय, हार्डवेयर के आधार पर, सिंगल-प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट का उपयोग करके की गई गणनाओं की तुलना में डबल प्रिसिजन वाली गणनाओं को पूरा होने में 2 से 32 गुना अधिक समय लग सकता है।<ref>{{Cite news|url=https://www.tomshardware.com/news/nvidia-titan-v-110-teraflops,36085.html|title=Nvidia’s New Titan V Pushes 110 Teraflops From A Single Chip|date=2017-12-08|work=Tom's Hardware|access-date=2018-11-05|language=en}}</ref> | डबल-प्रिसिजन फ़्लोटिंग-पॉइंट वेरिएबल्स का उपयोग प्रायः उनके एकल प्रिसिजन समकक्षों के साथ काम करने की तुलना में धीमा होता है। कंप्यूटिंग का एक क्षेत्र जहां यह एक विशेष विषय है, जीपीयू पर चलने वाला समानांतर कोड है। उदाहरण के लिए,[[ NVIDIA | एनवीडिया]] के [[CUDA|क्यूडा]] प्लेटफ़ॉर्म का उपयोग करते समय, हार्डवेयर के आधार पर, सिंगल-प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट का उपयोग करके की गई गणनाओं की तुलना में डबल प्रिसिजन वाली गणनाओं को पूरा होने में 2 से 32 गुना अधिक समय लग सकता है।<ref>{{Cite news|url=https://www.tomshardware.com/news/nvidia-titan-v-110-teraflops,36085.html|title=Nvidia’s New Titan V Pushes 110 Teraflops From A Single Chip|date=2017-12-08|work=Tom's Hardware|access-date=2018-11-05|language=en}}</ref> | ||

इसके अतिरिक्त, कई गणितीय फलनों (उदाहरण के लिए, साइन, कॉस, एटैन2, लॉग, एक्सपी और एसक्यूआरटी) को | इसके अतिरिक्त, कई गणितीय फलनों (उदाहरण के लिए, साइन, कॉस, एटैन2, लॉग, एक्सपी और एसक्यूआरटी) को यथार्थ डबल-यथार्थ परिणाम देने के लिए अधिक गणना की आवश्यकता होती है, और इसलिए धीमी होती है। | ||

=== इन्टिजर मानों पर प्रिसिजन सीमाएँ === | === इन्टिजर मानों पर प्रिसिजन सीमाएँ === | ||

* -2<sup>53</sup>से 2<sup>53</sup> (−9,007,199,254,740,992 से 9,007,199,254,740,992) तक के इंटिजर्स को | * -2<sup>53</sup>से 2<sup>53</sup> (−9,007,199,254,740,992 से 9,007,199,254,740,992) तक के इंटिजर्स को यथार्थ रूप से दर्शाया जा सकता है | ||

* 2<sup>53</sup>और 2<sup>54</sup> के बीच इन्टिजर = 18,014,398,509,481,984, 2 के गुणज तक (सम संख्या) | * 2<sup>53</sup>और 2<sup>54</sup> के बीच इन्टिजर = 18,014,398,509,481,984, 2 के गुणज तक (सम संख्या) | ||

* 2<sup>54</sup>और 2<sup>55</sup> के बीच इन्टिजर = 36,028,797,018,963,968, 4 के गुणज तक इन्टिजर | * 2<sup>54</sup>और 2<sup>55</sup> के बीच इन्टिजर = 36,028,797,018,963,968, 4 के गुणज तक इन्टिजर | ||

| Line 167: | Line 167: | ||

===सी और सी++=== | ===सी और सी++=== | ||

C और C++ विभिन्न प्रकार के अंकगणितीय प्रकार प्रदान करते हैं। मानकों द्वारा डबल प्रिसिजन की आवश्यकता नहीं है (आईईईई 754 अंकगणित को कवर करने वाले सी99 के वैकल्पिक अनुबंध एफ को छोड़कर), लेकिन अधिकांश प्रणालियों पर, <code>डबल</code> प्रकार डबल प्रिसिजन से मेल खाता है। हालाँकि, डिफ़ॉल्ट रूप से विस्तारित प्रिसिजन के साथ 32-बिट x86 पर, कुछ कंपाइलर सी मानक के अनुरूप नहीं हो सकते हैं या अंकगणित डबल राउंडिंग से | C और C++ विभिन्न प्रकार के अंकगणितीय प्रकार प्रदान करते हैं। मानकों द्वारा डबल प्रिसिजन की आवश्यकता नहीं है (आईईईई 754 अंकगणित को कवर करने वाले सी99 के वैकल्पिक अनुबंध एफ को छोड़कर), लेकिन अधिकांश प्रणालियों पर, <code>डबल</code> प्रकार डबल प्रिसिजन से मेल खाता है। हालाँकि, डिफ़ॉल्ट रूप से विस्तारित प्रिसिजन के साथ 32-बिट x86 पर, कुछ कंपाइलर सी मानक के अनुरूप नहीं हो सकते हैं या अंकगणित डबल राउंडिंग से प्रभावित हो सकता है।<ref>{{cite web|url=https://gcc.gnu.org/bugzilla/show_bug.cgi?id=323|title=Bug 323 – optimized code gives strange floating point results|website=gcc.gnu.org|access-date=30 April 2018|url-status=live|archive-url=https://web.archive.org/web/20180430012629/https://gcc.gnu.org/bugzilla/show_bug.cgi?id=323|archive-date=30 April 2018}}</ref> | ||

| Line 174: | Line 174: | ||

===[[सामान्य लिस्प|कॉमन लिस्प]]=== | ===[[सामान्य लिस्प|कॉमन लिस्प]]=== | ||

कॉमन लिस्प शॉर्ट-फ्लोट, सिंगल-फ्लोट, डबल-फ्लोट और लॉन्ग-फ्लोट टाइप प्रदान करता है। अधिकांश कार्यान्वयन अन्य प्रकार के उपयुक्त पर्यायवाची शब्दों के साथ सिंगल-फ्लोट्स और डबल-फ्लोट्स प्रदान करते हैं। आईईईई 754 के अनुसार, सामान्य लिस्प फ़्लोटिंग-पॉइंट अंडरफ्लो और ओवरफ़्लो और | कॉमन लिस्प शॉर्ट-फ्लोट, सिंगल-फ्लोट, डबल-फ्लोट और लॉन्ग-फ्लोट टाइप प्रदान करता है। अधिकांश कार्यान्वयन अन्य प्रकार के उपयुक्त पर्यायवाची शब्दों के साथ सिंगल-फ्लोट्स और डबल-फ्लोट्स प्रदान करते हैं। आईईईई 754 के अनुसार, सामान्य लिस्प फ़्लोटिंग-पॉइंट अंडरफ्लो और ओवरफ़्लो और यथार्थ फ़्लोटिंग-पॉइंट एक्सेप्शन को पकड़ने के लिए एक्सेप्शन प्रदान करता है। एएनएसआई मानक में कोई अनंतता और एनएएन का वर्णन नहीं किया गया है, हालांकि, कई कार्यान्वयन इन्हें एक्सटेंशन के रूप में प्रदान करते हैं। | ||

===जावा=== | ===जावा=== | ||

संस्करण 1.2 से पहले [[जावा (प्रोग्रामिंग भाषा)|जावा]] पर, प्रत्येक कार्यान्वयन को आईईईई 754 के अनुरूप होना था। संस्करण 1.2 ने [[x87]] जैसे प्लेटफार्मों के लिए मध्यवर्ती गणनाओं में अतिरिक्त | संस्करण 1.2 से पहले [[जावा (प्रोग्रामिंग भाषा)|जावा]] पर, प्रत्येक कार्यान्वयन को आईईईई 754 के अनुरूप होना था। संस्करण 1.2 ने [[x87]] जैसे प्लेटफार्मों के लिए मध्यवर्ती गणनाओं में अतिरिक्त प्रिसिजन लाने के लिए कार्यान्वयन की अनुमति दी। इस प्रकार स्ट्रिक्ट आईईईई 754 संगणनाओं को कार्यान्वित करने के लिए एक संशोधक [[strictfp|स्ट्रिक्टएफपी]] प्रस्तुत किया गया था। जावा 17 में स्ट्रिक्ट फ़्लोटिंग पॉइंट पुनःस्थापित कर दिया गया है।<ref>{{cite web|first=Joseph D. |last=Darcy |title=JEP 306: Restore Always-Strict Floating-Point Semantics |url=http://openjdk.java.net/jeps/306 |access-date=2021-09-12}}</ref> | ||

| Line 186: | Line 186: | ||

<br /> | <br /> | ||

===[[JSON|जेसन]] === | ===[[JSON|जेसन]] === | ||

जेसन डेटा एन्कोडिंग फॉर्मेट संख्यात्मक मानों का समर्थन करता है, और जिस व्याकरण के लिए संख्यात्मक अभिव्यक्तियाँ अनुरूप होनी चाहिए, उसमें एन्कोड किए गए संख्याओं की | जेसन डेटा एन्कोडिंग फॉर्मेट संख्यात्मक मानों का समर्थन करता है, और जिस व्याकरण के लिए संख्यात्मक अभिव्यक्तियाँ अनुरूप होनी चाहिए, उसमें एन्कोड किए गए संख्याओं की प्रिसिजन या रेंज पर कोई रेंज नहीं है। हालाँकि, आरएफसी 8259 सूचना देता है कि, चूंकि आईईईई 754 बाइनरी64 नंबर व्यापक रूप से कार्यान्वित हैं, इसलिए जेसन प्रसंस्करण कार्यान्वयन द्वारा अच्छी अंतरसंचालनीयता प्राप्त की जा सकती है यदि वे बाइनरी64 ऑफ़र की तुलना में अधिक प्रिसिजन या रेंज की अपेक्षा नहीं करते हैं।<ref>{{cite web |url=https://datatracker.ietf.org/doc/html/rfc8259 |title=जावास्क्रिप्ट ऑब्जेक्ट नोटेशन (JSON) डेटा इंटरचेंज प्रारूप|date=December 2017 |publisher=Internet Engineering Task Force |access-date=2022-02-01}}</ref> | ||

| Line 199: | Line 199: | ||

{{data types}} | {{data types}} | ||

रेंज:बाइनरी अंकगणित | |||

रेंज:कंप्यूटर अंकगणित | |||

रेंज:फ़्लोटिंग पॉइंट प्रकार | |||

[[Category:CS1 English-language sources (en)]] | |||

[[Category: | [[Category:Collapse templates]] | ||

[[Category:Created On 11/07/2023]] | [[Category:Created On 11/07/2023]] | ||

[[Category:Lua-based templates]] | |||

[[Category:Machine Translated Page]] | |||

[[Category:Navigational boxes| ]] | |||

[[Category:Navigational boxes without horizontal lists]] | |||

[[Category:Pages with script errors]] | |||

[[Category:Sidebars with styles needing conversion]] | |||

[[Category:Template documentation pages|Documentation/doc]] | |||

[[Category:Templates Vigyan Ready]] | |||

[[Category:Templates generating microformats]] | |||

[[Category:Templates that add a tracking category]] | |||

[[Category:Templates that are not mobile friendly]] | |||

[[Category:Templates that generate short descriptions]] | |||

[[Category:Templates using TemplateData]] | |||

[[Category:Wikipedia metatemplates]] | |||

Latest revision as of 11:02, 27 July 2023

डबल-प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट (जिसे कभी-कभी एफपी64 या फ्लोट64 भी कहा जाता है) एक फ़्लोटिंग-पॉइंट नंबर फॉर्मेट है, जो प्रायः कंप्यूटर मेमोरी में 64 बिट्स रखता है; यह एक फ़्लोटिंग रेडिक्स बिंदु का उपयोग करके संख्यात्मक मानों की एक विस्तृत डायनामिक श्रृंखला का निरूपण करता है।

फ़्लोटिंग पॉइंट का उपयोग भिन्नात्मक मानों को दर्शाने के लिए किया जाता है, या जब निश्चित-बिंदु (समान बिट विड्थ) द्वारा प्रदान की जाने वाली व्यापक रेंज की आवश्यकता होती है, भले ही प्रिसिजन की लागत पर हो। डबल प्रिसिजन को तब चुना जा सकता है जब एकल-प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट की रेंज या प्रिसिजन अपर्याप्त होगी।

आईईई 754-2008 मानकीकरण में, 64-बिट बेस-2 फॉर्मेट को आधिकारिक रूप से बाइनरी64 कहा जाता है; आईईईई 754-1985 में इसे डबल कहा गया। आईईईई 754 अतिरिक्त फ़्लोटिंग-पॉइंट फॉर्मेट निर्दिष्ट करता है, जिसमें 32-बिट बेस-2 एकल प्रिसिजन और, हाल ही में, बेस-10 निरूपण सम्मिलित हैं।

सिंगल और डबल-प्रिसिजन फ़्लोटिंग-पॉइंट डेटा टाइप प्रदान करने वाली पहली प्रोग्रामिंग भाषाओं में से एक फोरट्रान थी। आईईईई 754-1985 को व्यापक रूप से अपनाने से पहले, फ्लोटिंग-पॉइंट डेटा टाइप का निरूपण और गुण कंप्यूटर निर्माता और कंप्यूटर मॉडल और प्रोग्रामिंग-भाषा कार्यान्वयनकर्ताओं द्वारा किए गए निर्णयों पर निर्भर थे। उदाहरण के लिए, जीडब्ल्यू-बेसिक का डबल-प्रिसिजन डेटा टाइप 64-बिट एमबीएफ फ़्लोटिंग-पॉइंट फॉर्मेट था।

| Floating-point formats |

|---|

| IEEE 754 |

|

| Other |

आईईईई 754 डबल-प्रिसिजन बाइनरी फ़्लोटिंग-पॉइंट फॉर्मेट: बाइनरी64

इसके प्रदर्शन और बैंडविड्थ लागत के बाद भी, सिंगल-प्रिसिजन फ़्लोटिंग पॉइंट पर इसकी व्यापक रेंज के कारण डबल-प्रिसिजन बाइनरी फ़्लोटिंग-पॉइंट पीसी पर साधारणतः उपयोग किया जाने वाला फॉर्मेट है। इसे प्रायः डबल के नाम से जाना जाता है। आईईईई 754 मानक एक बाइनरी64 को इस प्रकार निर्दिष्ट करता है:

साइन बिट संख्या का साइन निर्धारित करता है (इसमें यह भी सम्मिलित है कि जब यह संख्या जीरो है, जो साइन्ड है)।

घातांक क्षेत्र पूर्वाग्रहित रूप में 0 से 2047 तक 11-बिट अनसाइन्ड इन्टिजर है: 1023 का घातांक मान वास्तविक जीरो का निरूपण करता है। घातांक -1022 से +1023 तक होते हैं क्योंकि -1023 (सभी 0s) और +1024 (सभी 1s) के घातांक विशेष संख्याओं के लिए आरक्षित होते हैं।

53-बिट अपूर्णांश प्रिसिजन 15 से 17 सार्थक डेसीमल अंकों की प्रिसिजन (2−53 ≈ 1.11 × 10−16) देती है। यदि अधिकतम 15 सार्थक अंकों वाली एक डेसीमल स्ट्रिंग को सामान्य संख्या देते हुए आईईईई 754 डबल-प्रिसिजन फॉर्मेट में परिवर्तित किया जाता है, और फिर समान अंकों की संख्या के साथ डेसीमल स्ट्रिंग में परिवर्तित किया जाता है, तो अंतिम परिणाम मूल स्ट्रिंग से सुमेलित होना चाहिए। यदि आईईईई 754 डबल-प्रिसिजन संख्या को कम से कम 17 सार्थक अंकों के साथ डेसीमल स्ट्रिंग में परिवर्तित किया जाता है, और फिर वापस डबल-प्रिसिजन निरूपण में परिवर्तित किया जाता है, तो अंतिम परिणाम मूल संख्या से सुमेलित होना चाहिए।[1]

फॉर्मेट को अपूर्णांश के साथ लिखा गया है और इसमें मान 1 का एक अंतर्निहित इन्टिजर बिट है (विशेष डेटा को छोड़कर, नीचे घातांक एन्कोडिंग देखें)। फ्रैक्शन (एफ) के 52 बिट्स के मेमोरी फॉर्मेट में प्रदर्शित होने के साथ, कुल प्रिसिजन 53 बिट्स (लगभग 16 डेसीमल अंक, 53 log10(2) ≈ 15.955) है। बिट्स को इस प्रकार रखा गया है:

किसी दिए गए एक्सपोनेंट पूर्वाग्रह और एक 52-बिट फ्रैक्शन के साथ दिए गए 64-बिट डबल-प्रिसिजन डेटम द्वारा ग्रहण किया गया वास्तविक मान है

किसी दिए गए एक्सपोनेंट पूर्वाग्रह और एक 52-बिट फ्रैक्शन के साथ दिए गए 64-बिट डबल-प्रिसिजन डेटम द्वारा ग्रहण किया गया वास्तविक मान है

या

252=4,503,599,627,370,496 और 253=9,007,199,254,740,992 के बीच निरूपण योग्य संख्याएँ बिल्कुल इन्टिजर हैं। अगली रेंज के लिए, 253 से 254 तक, हर संख्या को 2 से गुणा किया जाता है, इसलिए निरूपण योग्य संख्याएँ सम संख्याएँ हैं, आदि। इसके विपरीत, 251से 252 तक की पिछली रेंज के लिए, अंतर 0.5 है, आदि।

2nसे 2n+1 की रेंज में संख्याओं के अंश के रूप में अंतर 2n−52 है। किसी संख्या को निकटतम निरूपण योग्य संख्या (मशीन एप्सिलॉन) में पूर्णांकित करते समय अधिकतम रिलेटिव रॉउंडिंग त्रुटि 2−53 होती है।

घातांक की 11 बिट विड्थ पूर्ण 15-17 डेसीमल अंकों की प्रिसिजन के साथ 10−308और 10308 के बीच संख्याओं के निरूपण की अनुमति देती है। प्रिसिजन से सन्धि करके, असामान्य निरूपण लगभग 5 × 10−324 तक के छोटे मानों की भी अनुमति देता है।

घातांक एन्कोडिंग

डबल-प्रिसिजन बाइनरी फ़्लोटिंग-पॉइंट एक्सपोनेंट को ऑफसेट-बाइनरी प्रतिरूपण का उपयोग करके एन्कोड किया गया है, जिसमें जीरो ऑफसेट 1023 है; आईईईई 754 मानक में एक्सपोनेंट पूर्वाग्रह के रूप में भी जाना जाता है। ऐसे अभ्यावेदन के उदाहरण होंगे:

e =000000000012=00116=1:

|

(सामान्य संख्याओं के लिए सबसे छोटा घातांक) | ||

e =011111111112=3ff16=1023:

|

(जीरो ऑफसेट) | ||

e =100000001012=40516=1029:

|

|||

e =111111111102=7fe16=2046:

|

(उच्चतम घातांक) |

घातांक00016 और 7ff16 का एक विशेष अर्थ है:

000000000002=00016का उपयोग एक साइन्ड जीरो (यदि F = 0) और असामान्य संख्याओं (यदि F ≠ 0) को दर्शाने के लिए किया जाता है; और111111111112=7ff16का उपयोग ∞ (यदि F = 0) और एनएएन (यदि F ≠ 0) को दर्शाने के लिए किया जाता है,

जहाँ F अपूर्णांश का भिन्नात्मक भाग है। सभी बिट पैटर्न वैध एन्कोडिंग हैं।

उपरोक्त अपवादों को छोड़कर, संपूर्ण डबल-प्रिसिजन संख्या का वर्णन इस प्रकार किया गया है:

असामान्य संख्याओं (e = 0) की स्थिति में डबल-प्रिसिजन संख्या का वर्णन इस प्रकार किया गया है:

एंडियननेस

हालांकि कई प्रोसेसर सभी प्रकार के डेटा (इन्टिजर, फ़्लोटिंग पॉइंट) के लिए छोटे-एंडियन स्टोरेज का उपयोग करते हैं, ऐसे कई हार्डवेयर आर्किटेक्चर हैं जहां फ़्लोटिंग-पॉइंट संख्याओं को बड़े-एंडियन रूप में दर्शाया जाता है जबकि इन्टिजर को छोटे-एंडियन रूप में दर्शाया जाता है। ऐसे एआरएम प्रोसेसर हैं जिनमें डबल-प्रिसिजन संख्याओं के लिए मिश्रित-एंडियन फ़्लोटिंग-पॉइंट निरूपण होता है: दो 32-बिट शब्दों में से प्रत्येक को छोटे-एंडियन के रूप में संग्रहीत किया जाता है, लेकिन सबसे महत्वपूर्ण शब्द पहले संग्रहीत किया जाता है। वीएएक्स फ़्लोटिंग पॉइंट छोटे-एंडियन 16-बिट शब्दों को बड़े-एंडियन क्रम में संग्रहीत करता है। चूँकि ऐसे कई फ़्लोटिंग-पॉइंट फॉर्मेट हैं जिनके लिए कोई नेटवर्क मानक निरूपण नहीं है, एक्सडीआर मानक इसके निरूपण के रूप में बिग-एंडियन आईईईई 754 का उपयोग करता है। इसलिए यह अजीब लग सकता है कि व्यापक आईईईई 754फ़्लोटिंग-पॉइंट मानक एंडियननेस निर्दिष्ट नहीं करता है। सैद्धांतिक रूप से, इसका मतलब यह है कि एक मशीन द्वारा लिखा गया मानक आईईईई फ़्लोटिंग-पॉइंट डेटा भी दूसरे द्वारा पढ़ने योग्य नहीं हो सकता है। हालाँकि, आधुनिक मानक कंप्यूटरों पर (यानी, आईईईई 754 को कार्यान्वित करते हुए), कोई सुरक्षित रूप से मान सकता है कि फ़्लोटिंग-पॉइंट संख्याओं के लिए एंडियननेस इन्टिजर के समान ही है, जिससे डेटा टाइप की परवाह किए बिना रूपांतरण सीधा हो जाता है। विशेष फ़्लोटिंग-पॉइंट फॉर्मेटों का उपयोग करने वाले छोटे एम्बेडेड सिस्टम एक और विषय हो सकता हैं।

डबल-प्रिसिजन उदाहरण

| 0 01111111111 00000000000000000000000000000000000000000000000000002 ≙ 3FF0 0000 0000 000016 ≙ +20 × 1 = 1 |

| 0 01111111111 00000000000000000000000000000000000000000000000000012 ≙ 3FF0 0000 0000 000116 ≙ +20 × (1 + 2−52) ≈ 1.0000000000000002, सबसे छोटी संख्या > 1 |

| 0 01111111111 00000000000000000000000000000000000000000000000000102 ≙ 3FF0 0000 0000 000216 ≙ +20 × (1 + 2−51) ≈ 1.0000000000000004 |

| 0 10000000000 00000000000000000000000000000000000000000000000000002 ≙ 4000 0000 0000 000016 ≙ +21 × 1 = 2 |

| 1 10000000000 00000000000000000000000000000000000000000000000000002 ≙ C000 0000 0000 000016 ≙ −21 × 1 = −2 |

| 0 10000000000 10000000000000000000000000000000000000000000000000002 ≙ 4008 0000 0000 000016 ≙ +21 × 1.12 = 112 = 3 |

| 0 10000000001 00000000000000000000000000000000000000000000000000002 ≙ 4010 0000 0000 000016 ≙ +22 × 1 = 1002 = 4 |

| 0 10000000001 01000000000000000000000000000000000000000000000000002 ≙ 4014 0000 0000 000016 ≙ +22 × 1.012 = 1012 = 5 |

| 0 10000000001 10000000000000000000000000000000000000000000000000002 ≙ 4018 0000 0000 000016 ≙ +22 × 1.12 = 1102 = 6 |

| 0 10000000011 01110000000000000000000000000000000000000000000000002 ≙ 4037 0000 0000 000016 ≙ +24 × 1.01112 = 101112 = 23 |

| 0 01111111000 10000000000000000000000000000000000000000000000000002 ≙ 3F88 0000 0000 000016 ≙ +2−7 × 1.12 = 0.000000112 = 0.01171875 (3/256) |

| 0 00000000000 00000000000000000000000000000000000000000000000000012 ≙ 0000 0000 0000 000116 ≙ +2−1022 × 2−52 = 2−1074 ≈ 4.9406564584124654 × 10−324 (न्यूनतम असामान्य धनात्मक डबल) |

| 0 00000000000 11111111111111111111111111111111111111111111111111112 ≙ 000F FFFF FFFF FFFF16 ≙ +2−1022 × (1 − 2−52) ≈ 2.2250738585072009 × 10−308 (अधिकतम असामान्य डबल) |

| 0 00000000001 00000000000000000000000000000000000000000000000000002 ≙ 0010 0000 0000 000016 ≙ +2−1022 × 1 ≈ 2.2250738585072014 × 10−308 (न्यूनतम सामान्य धनात्मक डबल) |

| 0 11111111110 11111111111111111111111111111111111111111111111111112 ≙ 7FEF FFFF FFFF FFFF16 ≙ +21023 × (1 + (1 − 2−52)) ≈ 1.7976931348623157 × 10308 (अधिकतम डबल) |

| 0 00000000000 00000000000000000000000000000000000000000000000000002 ≙ 0000 0000 0000 000016 ≙ +0 |

| 1 00000000000 00000000000000000000000000000000000000000000000000002 ≙ 8000 0000 0000 000016 ≙ −0 |

| 0 11111111111 00000000000000000000000000000000000000000000000000002 ≙ 7FF0 0000 0000 000016 ≙ +∞ (धनात्मक इनफिनिटी) |

| 1 11111111111 00000000000000000000000000000000000000000000000000002 ≙ FFF0 0000 0000 000016 ≙ −∞ (ऋणात्मक इनफिनिटी) |

| 0 11111111111 00000000000000000000000000000000000000000000000000012 ≙ 7FF0 0000 0000 000116 ≙ एनएएन (अधिकांश प्रोसेसर पर एसएनएएन, जैसे x86 और एआरएम) |

| 0 11111111111 10000000000000000000000000000000000000000000000000012 ≙ 7FF8 0000 0000 000116 ≙ एनएएन (अधिकांश प्रोसेसर पर क्यूएनएएन, जैसे x86 और एआरएम) |

| 0 11111111111 11111111111111111111111111111111111111111111111111112 ≙ 7FFF FFFF FFFF FFFF16 ≙ एनएएन (एनएएन का एक वैकल्पिक एन्कोडिंग) |

| 0 01111111101 01010101010101010101010101010101010101010101010101012 = 3FD5 5555 5555 555516 ≙ +2−2 × (1 + 2−2 + 2−4 + ... + 2−52) ≈ 1/3 |

| 0 10000000000 10010010000111111011010101000100010000101101000110002 = 4009 21FB 5444 2D1816 ≈ pi |

क्यूएनएएन और एसएनएएन की एन्कोडिंग आईईईई 754 में पूरी तरह से निर्दिष्ट नहीं हैं और प्रोसेसर पर निर्भर करती हैं। अधिकांश प्रोसेसर, जैसे कि x86 फैमिली और एआरएम फैमिली प्रोसेसर, एक क्वाइट एनएएन को इंगित करने के लिए अपूर्णांश क्षेत्र के सबसे महत्वपूर्ण बिट का उपयोग करते हैं; आईईईई 754 द्वारा इसकी अनुशंसा की जाती है। पीए-आरआईएससी प्रोसेसर सिग्नलिंग एनएएन को इंगित करने के लिए बिट का उपयोग करते हैं।

डिफ़ॉल्ट रूप से, अपूर्णांश में बिट्स की विषम संख्या के कारण, एकल प्रिसिजन की तरह ऊपर की बदले 1/3 राउंड नीचे होता है।

और अधिक विस्तार में:

हेक्साडेसिमल निरूपण को देखते हुए 3FD5 5555 5555 555516, साइन = 0 घातांक = 3FD16 =1021 घातांक पूर्वाग्रह = 1023 (स्थिर मान; ऊपर देखें) भिन्न = 5 5555 5555 555516

मान = 2(घातांक - घातांक पूर्वाग्रह) × 1.अंश - ध्यान दें कि भिन्न को यहां डेसीमल में परिवर्तित नहीं किया जाना चाहिए

= 2−2 × (15 5555 5555 555516 × 2−52)

= 2−54 × 15 5555 5555 555516

= 0.333333333333333314829616256247390992939472198486328125

≈ 1/3

डबल-प्रिसिजन अंकगणित के साथ निष्पादन गति

डबल-प्रिसिजन फ़्लोटिंग-पॉइंट वेरिएबल्स का उपयोग प्रायः उनके एकल प्रिसिजन समकक्षों के साथ काम करने की तुलना में धीमा होता है। कंप्यूटिंग का एक क्षेत्र जहां यह एक विशेष विषय है, जीपीयू पर चलने वाला समानांतर कोड है। उदाहरण के लिए, एनवीडिया के क्यूडा प्लेटफ़ॉर्म का उपयोग करते समय, हार्डवेयर के आधार पर, सिंगल-प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट का उपयोग करके की गई गणनाओं की तुलना में डबल प्रिसिजन वाली गणनाओं को पूरा होने में 2 से 32 गुना अधिक समय लग सकता है।[2]

इसके अतिरिक्त, कई गणितीय फलनों (उदाहरण के लिए, साइन, कॉस, एटैन2, लॉग, एक्सपी और एसक्यूआरटी) को यथार्थ डबल-यथार्थ परिणाम देने के लिए अधिक गणना की आवश्यकता होती है, और इसलिए धीमी होती है।

इन्टिजर मानों पर प्रिसिजन सीमाएँ

- -253से 253 (−9,007,199,254,740,992 से 9,007,199,254,740,992) तक के इंटिजर्स को यथार्थ रूप से दर्शाया जा सकता है

- 253और 254 के बीच इन्टिजर = 18,014,398,509,481,984, 2 के गुणज तक (सम संख्या)

- 254और 255 के बीच इन्टिजर = 36,028,797,018,963,968, 4 के गुणज तक इन्टिजर

कार्यान्वयन

डबल्स को कई प्रोग्रामिंग भाषाओं में अलग-अलग तरीकों से कार्यान्वित किया जाता है जैसे कि निम्नलिखित में किया गया है। केवल डायनामिक प्रिसिजन वाले प्रोसेसर पर, जैसे कि एसएसई2 के बिना x86 (या जब संगतता उद्देश्य के लिए एसएसई2 का उपयोग नहीं किया जाता है) और डिफ़ॉल्ट रूप से उपयोग की जाने वाली विस्तारित प्रिसिजन के साथ, सॉफ़्टवेयर को कुछ आवश्यकताओं को पूरा करने में कठिनाई हो सकती है।

सी और सी++

C और C++ विभिन्न प्रकार के अंकगणितीय प्रकार प्रदान करते हैं। मानकों द्वारा डबल प्रिसिजन की आवश्यकता नहीं है (आईईईई 754 अंकगणित को कवर करने वाले सी99 के वैकल्पिक अनुबंध एफ को छोड़कर), लेकिन अधिकांश प्रणालियों पर, डबल प्रकार डबल प्रिसिजन से मेल खाता है। हालाँकि, डिफ़ॉल्ट रूप से विस्तारित प्रिसिजन के साथ 32-बिट x86 पर, कुछ कंपाइलर सी मानक के अनुरूप नहीं हो सकते हैं या अंकगणित डबल राउंडिंग से प्रभावित हो सकता है।[3]

फोरट्रान

फोरट्रान कई इंटिजर्स और रियल टाइप प्रदान करता है, और 64-बिट प्रकार रियल64प्रदान करता है, जो फोरट्रान के आंतरिक मॉड्यूल आईएसओ_फोरट्रान_ईएनवीके माध्यम से पहुंच योग्य है, जो डबल प्रिसिजन से मेल खाता है।

कॉमन लिस्प

कॉमन लिस्प शॉर्ट-फ्लोट, सिंगल-फ्लोट, डबल-फ्लोट और लॉन्ग-फ्लोट टाइप प्रदान करता है। अधिकांश कार्यान्वयन अन्य प्रकार के उपयुक्त पर्यायवाची शब्दों के साथ सिंगल-फ्लोट्स और डबल-फ्लोट्स प्रदान करते हैं। आईईईई 754 के अनुसार, सामान्य लिस्प फ़्लोटिंग-पॉइंट अंडरफ्लो और ओवरफ़्लो और यथार्थ फ़्लोटिंग-पॉइंट एक्सेप्शन को पकड़ने के लिए एक्सेप्शन प्रदान करता है। एएनएसआई मानक में कोई अनंतता और एनएएन का वर्णन नहीं किया गया है, हालांकि, कई कार्यान्वयन इन्हें एक्सटेंशन के रूप में प्रदान करते हैं।

जावा

संस्करण 1.2 से पहले जावा पर, प्रत्येक कार्यान्वयन को आईईईई 754 के अनुरूप होना था। संस्करण 1.2 ने x87 जैसे प्लेटफार्मों के लिए मध्यवर्ती गणनाओं में अतिरिक्त प्रिसिजन लाने के लिए कार्यान्वयन की अनुमति दी। इस प्रकार स्ट्रिक्ट आईईईई 754 संगणनाओं को कार्यान्वित करने के लिए एक संशोधक स्ट्रिक्टएफपी प्रस्तुत किया गया था। जावा 17 में स्ट्रिक्ट फ़्लोटिंग पॉइंट पुनःस्थापित कर दिया गया है।[4]

जावा स्क्रिप्ट

जैसा कि ईसीएमएस्क्रिप्ट मानक द्वारा निर्दिष्ट किया गया है, जावास्क्रिप्ट में सभी अंकगणित डबल-प्रिसिजन फ़्लोटिंग-पॉइंट अंकगणित का उपयोग करके किया जाएगा।[5]

जेसन

जेसन डेटा एन्कोडिंग फॉर्मेट संख्यात्मक मानों का समर्थन करता है, और जिस व्याकरण के लिए संख्यात्मक अभिव्यक्तियाँ अनुरूप होनी चाहिए, उसमें एन्कोड किए गए संख्याओं की प्रिसिजन या रेंज पर कोई रेंज नहीं है। हालाँकि, आरएफसी 8259 सूचना देता है कि, चूंकि आईईईई 754 बाइनरी64 नंबर व्यापक रूप से कार्यान्वित हैं, इसलिए जेसन प्रसंस्करण कार्यान्वयन द्वारा अच्छी अंतरसंचालनीयता प्राप्त की जा सकती है यदि वे बाइनरी64 ऑफ़र की तुलना में अधिक प्रिसिजन या रेंज की अपेक्षा नहीं करते हैं।[6]

यह भी देखें

- आईईईई 754, फ्लोटिंग-पॉइंट अंकगणित के लिए आईईईई मानक

- डी संकेतन (वैज्ञानिक संकेतन)

नोट्स और संदर्भ

- ↑ William Kahan (1 October 1997). "Lecture Notes on the Status of IEEE Standard 754 for Binary Floating-Point Arithmetic" (PDF). Archived (PDF) from the original on 8 February 2012.

- ↑ "Nvidia's New Titan V Pushes 110 Teraflops From A Single Chip". Tom's Hardware (in English). 2017-12-08. Retrieved 2018-11-05.

- ↑ "Bug 323 – optimized code gives strange floating point results". gcc.gnu.org. Archived from the original on 30 April 2018. Retrieved 30 April 2018.

- ↑ Darcy, Joseph D. "JEP 306: Restore Always-Strict Floating-Point Semantics". Retrieved 2021-09-12.

- ↑ ECMA-262 ECMAScript Language Specification (PDF) (5th ed.). Ecma International. p. 29, §8.5 The Number Type. Archived (PDF) from the original on 2012-03-13.

- ↑ "जावास्क्रिप्ट ऑब्जेक्ट नोटेशन (JSON) डेटा इंटरचेंज प्रारूप". Internet Engineering Task Force. December 2017. Retrieved 2022-02-01.

रेंज:बाइनरी अंकगणित रेंज:कंप्यूटर अंकगणित रेंज:फ़्लोटिंग पॉइंट प्रकार