एमिटर टर्न ऑफ थाइरिस्टर: Difference between revisions

(Created page with "एमिटर टर्न ऑफ thyristor (ईटीओ) एक प्रकार का थाइरिस्टर है जो चालू और बंद क...") |

(text) |

||

| Line 1: | Line 1: | ||

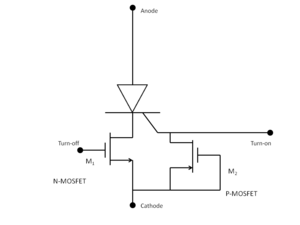

एमिटर टर्न ऑफ [[thyristor]] (ईटीओ) एक प्रकार का थाइरिस्टर है जो | '''एमिटर टर्न ऑफ [[thyristor|थाइरिस्टर]] (ईटीओ)''' एक प्रकार का थाइरिस्टर है जो टर्न ऑन और टर्न ऑफ के लिए [[MOSFET|मॉसफेट]] का उपयोग करता है। यह [[गेट टर्न-ऑफ थाइरिस्टर]] और मॉसफेट दोनों के बढ़त को जोड़ता है। इसमें दो गेट हैं - टर्न ऑन करने के लिए सामान्य गेट और दूसरा टर्न ऑफ के लिए श्रृंखला मॉसफेट के साथ हैं।<ref name="rashid">Rashid, Muhammad H.(2011); ''Power Electronics (3rd ed.)''. Pearson, {{ISBN|978-81-317-0246-8}}</ref> | ||

==इतिहास== | ==इतिहास== | ||

[[File:ETO..png|thumb|ईटीओ का सर्किट प्रतीक]] | [[File:ETO..png|thumb|ईटीओ का सर्किट प्रतीक]] | ||

[[File:Eto EQ CKT.png|thumb|ईटीओ का समतुल्य सर्किट]]पहली पीढ़ी के ईटीओ को 1996 में सेंटर फॉर पावर इलेक्ट्रॉनिक्स, वर्जीनिया टेक में प्रोफेसर एलेक्स क्यू हुआंग द्वारा विकसित किया गया था। हालांकि ईटीओ अवधारणा का प्रदर्शन किया गया था, पहली पीढ़ी के ईटीओ में सीमाएं थीं जो उच्च-शक्ति अनुप्रयोगों को रोकती थीं। बाद में | [[File:Eto EQ CKT.png|thumb|ईटीओ का समतुल्य सर्किट]]पहली पीढ़ी के ईटीओ को 1996 में सेंटर फॉर पावर इलेक्ट्रॉनिक्स, वर्जीनिया टेक में प्रोफेसर एलेक्स क्यू हुआंग द्वारा विकसित किया गया था। हालांकि ईटीओ अवधारणा का प्रदर्शन किया गया था, पहली पीढ़ी के ईटीओ में सीमाएं थीं जो उच्च-शक्ति अनुप्रयोगों को रोकती थीं। बाद में उपकरण दर को सुधार कर 4500V/4000A कर दिया गया था। <ref>{{cite web|url=http://hdl.handle.net/10919/26095|title=उन्नत एमिटर टर्न-ऑफ (ईटीओ) थाइरिस्टर का विकास|author=Zhang,Bin}}</ref> | ||

==उपकरण विवरण== | |||

[[File:PN structure of ETO.png|thumb|400px|left|एक उत्सर्जक की पीएन संरचना थाइरिस्टर को टर्न ऑफ देती है]] | |||

== | |||

[[File:PN structure of ETO.png|thumb|400px|left|एक उत्सर्जक की पीएन संरचना थाइरिस्टर को | |||

===टर्न ऑन=== | |||

[[गेट (ट्रांजिस्टर)]], गेट 1 और गेट 2 पर निश्चित वोल्टेज लागू करके ईटीओ को टर्न ऑन किया जाता है। जब गेट 2 पर निश्चित वोल्टेज लागू किया जाता है, तो यह मॉसफेट को टर्न ऑन करता है जो पीएनपीएन थाइरिस्टर संरचना के [[कैथोड]] टर्मिनल के साथ श्रृंखला में जुड़ा होता है। गेट 1 पर लगाया गया निश्चित वोल्टेज थाइरिस्टर के गेट टर्मिनल से जुड़े मॉसफेट को टर्न ऑफ देता है।<ref name="rashid"/> | |||

===टर्न ऑफ=== | |||

जब कैथोड से जुड़े मॉसफेट पर टर्न-ऑफ निषेधात्मक वोल्टेज संकेतक लगाया जाता है, तो यह टर्न ऑफ हो जाता है और कैथोड (थाइरिस्टर में एनपीएन [[ट्रांजिस्टर]] का N-एमिटर) से दूर सभी विद्युत प्रवाह को थाइरिस्टर के गेट से जुड़े मॉसफेट के माध्यम से बेस गेट में स्थानांतरित कर देता है। यह [[पुनर्योजी प्रक्रिया]] [[ कुंडी (इलेक्ट्रॉनिक्स) |(इलेक्ट्रॉनिक्स)]] को रोक देता है और परिणामस्वरूप तेजी से टर्न ऑफ हो जाता है। कैथोड से जुड़े मॉसफेट और थाइरिस्टर के गेट से जुड़े मॉसफेट दोनों [[पी-एन जंक्शन]] वाले थाइरिस्टर की आंतरिक संरचना के कारण ईटीओ पर वोल्टेज के परिमाण के बावजूद उच्च-वोल्टेज दबाव के अधीन नहीं हैं। मॉसफेट को श्रृंखला में जोड़ने का कमी यह है कि इसमें मुख्य थाइरिस्टर विद्युत प्रवाह को ले जाना होता है, और यह कुल वोल्टेज घटाव को लगभग 0.3 से 0.5V और इसके संबंधित नुकसान को भी बढ़ाता है। गेट टर्न-ऑफ थाइरिस्टर के समान, ईटीओ में टर्न-ऑफ के अंत में विद्युत प्रवाह प्रतिकूल टर्न-ऑफ अतः होती है और अगले टर्न-ऑन को तब तक इंतजार करना होगा जब तक कि [[एनोड]] पक्ष पर अवशिष्ट चार्ज पुनर्संयोजन प्रक्रिया के माध्यम से समाप्त न हो जाए।<ref name="rashid"/> | |||

==यह भी देखें== | ==यह भी देखें== | ||

* थाइरिस्टर | * थाइरिस्टर | ||

Revision as of 10:59, 31 July 2023

एमिटर टर्न ऑफ थाइरिस्टर (ईटीओ) एक प्रकार का थाइरिस्टर है जो टर्न ऑन और टर्न ऑफ के लिए मॉसफेट का उपयोग करता है। यह गेट टर्न-ऑफ थाइरिस्टर और मॉसफेट दोनों के बढ़त को जोड़ता है। इसमें दो गेट हैं - टर्न ऑन करने के लिए सामान्य गेट और दूसरा टर्न ऑफ के लिए श्रृंखला मॉसफेट के साथ हैं।[1]

इतिहास

पहली पीढ़ी के ईटीओ को 1996 में सेंटर फॉर पावर इलेक्ट्रॉनिक्स, वर्जीनिया टेक में प्रोफेसर एलेक्स क्यू हुआंग द्वारा विकसित किया गया था। हालांकि ईटीओ अवधारणा का प्रदर्शन किया गया था, पहली पीढ़ी के ईटीओ में सीमाएं थीं जो उच्च-शक्ति अनुप्रयोगों को रोकती थीं। बाद में उपकरण दर को सुधार कर 4500V/4000A कर दिया गया था। [2]

उपकरण विवरण

टर्न ऑन

गेट (ट्रांजिस्टर), गेट 1 और गेट 2 पर निश्चित वोल्टेज लागू करके ईटीओ को टर्न ऑन किया जाता है। जब गेट 2 पर निश्चित वोल्टेज लागू किया जाता है, तो यह मॉसफेट को टर्न ऑन करता है जो पीएनपीएन थाइरिस्टर संरचना के कैथोड टर्मिनल के साथ श्रृंखला में जुड़ा होता है। गेट 1 पर लगाया गया निश्चित वोल्टेज थाइरिस्टर के गेट टर्मिनल से जुड़े मॉसफेट को टर्न ऑफ देता है।[1]

टर्न ऑफ

जब कैथोड से जुड़े मॉसफेट पर टर्न-ऑफ निषेधात्मक वोल्टेज संकेतक लगाया जाता है, तो यह टर्न ऑफ हो जाता है और कैथोड (थाइरिस्टर में एनपीएन ट्रांजिस्टर का N-एमिटर) से दूर सभी विद्युत प्रवाह को थाइरिस्टर के गेट से जुड़े मॉसफेट के माध्यम से बेस गेट में स्थानांतरित कर देता है। यह पुनर्योजी प्रक्रिया (इलेक्ट्रॉनिक्स) को रोक देता है और परिणामस्वरूप तेजी से टर्न ऑफ हो जाता है। कैथोड से जुड़े मॉसफेट और थाइरिस्टर के गेट से जुड़े मॉसफेट दोनों पी-एन जंक्शन वाले थाइरिस्टर की आंतरिक संरचना के कारण ईटीओ पर वोल्टेज के परिमाण के बावजूद उच्च-वोल्टेज दबाव के अधीन नहीं हैं। मॉसफेट को श्रृंखला में जोड़ने का कमी यह है कि इसमें मुख्य थाइरिस्टर विद्युत प्रवाह को ले जाना होता है, और यह कुल वोल्टेज घटाव को लगभग 0.3 से 0.5V और इसके संबंधित नुकसान को भी बढ़ाता है। गेट टर्न-ऑफ थाइरिस्टर के समान, ईटीओ में टर्न-ऑफ के अंत में विद्युत प्रवाह प्रतिकूल टर्न-ऑफ अतः होती है और अगले टर्न-ऑन को तब तक इंतजार करना होगा जब तक कि एनोड पक्ष पर अवशिष्ट चार्ज पुनर्संयोजन प्रक्रिया के माध्यम से समाप्त न हो जाए।[1]

यह भी देखें

- थाइरिस्टर

- मॉसफेट

- गेट टर्न-ऑफ थाइरिस्टर

संदर्भ

- ↑ 1.0 1.1 1.2 Rashid, Muhammad H.(2011); Power Electronics (3rd ed.). Pearson, ISBN 978-81-317-0246-8

- ↑ Zhang,Bin. "उन्नत एमिटर टर्न-ऑफ (ईटीओ) थाइरिस्टर का विकास".