नॉर(NOR) फ़्लैश प्रतिस्थापन: Difference between revisions

(Created page with "जबकि फ्लैश मेमोरी अपनी गैर-अस्थिरता, शॉक-प्रतिरोध, छोटे आकार और क...") |

No edit summary |

||

| Line 1: | Line 1: | ||

जबकि [[फ्लैश मेमोरी]] अपनी गैर-अस्थिरता, शॉक-प्रतिरोध, छोटे आकार और कम ऊर्जा खपत के कारण [[अंतः स्थापित प्रणालियाँ]] में सबसे लोकप्रिय स्टोरेज में से | जबकि [[फ्लैश मेमोरी]] अपनी गैर-अस्थिरता, शॉक-प्रतिरोध, छोटे आकार और कम ऊर्जा खपत के कारण [[अंतः स्थापित प्रणालियाँ]] में सबसे लोकप्रिय स्टोरेज में से बनी हुई है, इसका अनुप्रयोग इसके मूल डिजाइन से कहीं अधिक बढ़ गया है। अपने मूल डिजाइन के आधार पर, NOR फ्लैश मेमोरी को प्रोग्राम के बाइनरी कोड को स्टोर करने के लिए डिज़ाइन किया गया है क्योंकि यह [[XIP]] (eXecute-In-Place) और रीड ऑपरेशंस में उच्च प्रदर्शन का समर्थन करता है, जबकि NAND फ्लैश मेमोरी का उपयोग इसकी कम कीमत के कारण डेटा स्टोरेज के रूप में किया जाता है। और NOR फ़्लैश की तुलना में लिखने/मिटाने के कार्यों में उच्च प्रदर्शन। हाल के वर्षों में, NAND फ़्लैश की कीमत NOR फ़्लैश की तुलना में बहुत तेज़ी से कम हुई है। इस प्रकार, अंततः हार्डवेयर लागत को कम करने के लिए, NOR फ्लैश को बदलने के लिए NAND फ्लैश का उपयोग करना (मजबूत बाजार मांग से प्रेरित) एम्बेडेड-सिस्टम डिजाइन में नया चलन बन गया है, खासकर [[मोबाइल फोन]] और [[आर्केड खेल]] पर। | ||

== सिंहावलोकन == | == सिंहावलोकन == | ||

प्रतिस्थापन फ़्लैश मेमोरी के अच्छी तरह से डिज़ाइन किए गए प्रबंधन पर निर्भर करता है, जो या तो होस्ट सिस्टम पर सॉफ़्टवेयर (एक कच्चे माध्यम के रूप में) या उसके उपकरणों के अंदर हार्डवेयर सर्किट/फर्मवेयर द्वारा किया जाता है। यहां, सीमित मेमोरी-स्पेस आवश्यकताओं और | प्रतिस्थापन फ़्लैश मेमोरी के अच्छी तरह से डिज़ाइन किए गए प्रबंधन पर निर्भर करता है, जो या तो होस्ट सिस्टम पर सॉफ़्टवेयर (एक कच्चे माध्यम के रूप में) या उसके उपकरणों के अंदर हार्डवेयर सर्किट/फर्मवेयर द्वारा किया जाता है। यहां, सीमित मेमोरी-स्पेस आवश्यकताओं और कुशल कार्यान्वयन के साथ कुशल भविष्यवाणी तंत्र प्रस्तावित है। भविष्यवाणी तंत्र कार्यशील सेट अवधारणा को अपनाकर भविष्यवाणी ग्राफ बनाने के लिए कार्यक्रम निष्पादन के पहुंच पैटर्न एकत्र करता है। पूर्वानुमान ग्राफ़ के अनुसार, पूर्वानुमान तंत्र डेटा (/कोड) को [[स्थैतिक रैंडम-एक्सेस मेमोरी]] कैश में प्रीफ़ेच करता है, ताकि कैश मिस रेट को कम किया जा सके। इसलिए, प्रोग्राम निष्पादन के प्रदर्शन में सुधार होता है और NAND और NOR के बीच पढ़ने के प्रदर्शन का अंतर प्रभावी ढंग से भर जाता है। बूट कोड के लिए NAND फ़्लैश का उपयोग करने के लिए कोड को छाया देने के लिए [[DRAM]] के उपयोग की आवश्यकता होती है।<ref>[https://www.macronix.com/Lists/ApplicationNote/Attachments/1908/AN0270V1-Booting%20from%20NAND%20App%20Note-1212-new.pdf Booting from NAND Flash Memory]</ref> | ||

== एक प्रभावी प्रीफ़ेचिंग रणनीति == | == एक प्रभावी प्रीफ़ेचिंग रणनीति == | ||

मेमोरी पदानुक्रम में लोकप्रिय [[कैश (कंप्यूटिंग)]] विचारों से अलग, इस दृष्टिकोण का लक्ष्य | मेमोरी पदानुक्रम में लोकप्रिय [[कैश (कंप्यूटिंग)]] विचारों से अलग, इस दृष्टिकोण का लक्ष्य एप्लिकेशन-उन्मुख कैशिंग तंत्र है, जो अनुप्रयोगों के दिए गए निष्पादन निशान के आधार पर भविष्यवाणी-सहायता प्रीफ़ेचिंग को अपनाता है। एम्बेडेड सिस्टम के डिज़ाइन को अनुप्रयोगों के सीमित सेट के साथ माना जाता है, जैसे मोबाइल फोन में चयनित सिस्टम प्रोग्राम का सेट या मनोरंजन-पार्क मशीनों के आर्केड गेम। इसके अलावा, कार्यान्वयन में SRAM क्षमता और कंप्यूटिंग शक्ति बाधित है। | ||

=== हार्डवेयर आर्किटेक्चर === | === हार्डवेयर आर्किटेक्चर === | ||

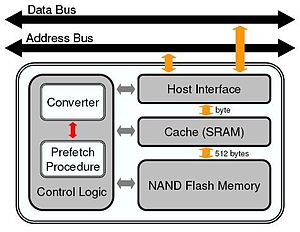

[[File:NR2.JPG|thumb|right|300px|NAND फ्लैश मेमोरी के प्रदर्शन में सुधार के लिए | [[File:NR2.JPG|thumb|right|300px|NAND फ्लैश मेमोरी के प्रदर्शन में सुधार के लिए आर्किटेक्चर]]हार्डवेयर डिज़ाइन में चार आवश्यक घटक शामिल हैं: होस्ट इंटरफ़ेस, SRAM (कैश), NAND फ़्लैश मेमोरी और नियंत्रण तर्क। NAND और NOR के बीच प्रदर्शन अंतर को भरने के लिए, SRAM NAND पर डेटा एक्सेस के लिए कैश परत के रूप में कार्य करता है। होस्ट इंटरफ़ेस पते और डेटा [[कंप्यूटर बस]] के माध्यम से होस्ट सिस्टम के साथ संचार के लिए जिम्मेदार है। सबसे महत्वपूर्ण बात यह है कि नियंत्रण तर्क कैशिंग गतिविधि का प्रबंधन करता है और NAND फ़्लैश और SRAM के साथ NOR फ़्लैश का सेवा अनुकरण प्रदान करता है; सिस्टम के प्रदर्शन को बेहतर बनाने के लिए इसमें बुद्धिमान भविष्यवाणी तंत्र लागू होना चाहिए। नियंत्रण तर्क में दो प्रमुख घटक हैं: कनवर्टर SRAM कैश के साथ NAND फ्लैश पर NOR फ्लैश एक्सेस का अनुकरण करता है, जहां एड्रेस ट्रांसलेशन बाइट एड्रेसिंग (NOR के लिए) से [[ तार्किक ब्लॉक पता |तार्किक ब्लॉक पता]] (LBA) एड्रेसिंग (NAND के लिए) में किया जाना चाहिए। ध्यान दें कि प्रत्येक 512B/2KB NAND पृष्ठ क्रमशः और चार LBA से मेल खाता है। प्रीफ़ेच प्रक्रिया NAND से SRAM में डेटा प्रीफ़ेच करने का प्रयास करती है ताकि NOR एक्सेस की हिट दर SRAM से अधिक हो। प्रक्रिया को एकत्र किए गए निशानों के सेट के माध्यम से लक्ष्य एप्लिकेशन के व्यवहार को पार्स करना और निकालना चाहिए। एकत्रित निशानों से निकाले गए एक्सेस पैटर्न के अनुसार, प्रक्रिया भविष्यवाणी जानकारी उत्पन्न करती है, जिसे भविष्यवाणी ग्राफ के रूप में जाना जाता है। | ||

=== भविष्यवाणी ग्राफ === | === भविष्यवाणी ग्राफ === | ||

NOR (या NAND) पर एप्लिकेशन निष्पादन के एक्सेस पैटर्न में LBA का | NOR (या NAND) पर एप्लिकेशन निष्पादन के एक्सेस पैटर्न में LBA का क्रम होता है। जैसे ही कोई एप्लिकेशन कई बार चलता है, एप्लिकेशन निष्पादन के संभावित एक्सेस पैटर्न की "वस्तुतः" पूरी तस्वीर दिखाई दे सकती है। चूंकि अधिकांश एप्लिकेशन निष्पादन इनपुट-निर्भर या डेटा-संचालित होते हैं, इसलिए किसी दिए गए एलबीए के बाद से अधिक एलबीए हो सकते हैं, जहां प्रत्येक एलबीए ग्राफ़ में नोड से मेल खाता है। से अधिक अनुवर्ती एलबीए वाले नोड्स को शाखा नोड कहा जाता है, और अन्य को नियमित नोड कहा जाता है। वह ग्राफ़ जो एक्सेस पैटर्न से मेल खाता है उसे विशिष्ट एप्लिकेशन का पूर्वानुमान ग्राफ़ कहा जाता है। यदि NAND फ़्लैश में पेजों को समय-समय पर प्रीफ़ेच किया जा सकता है, और कैशिंग के लिए पर्याप्त SRAM स्थान है, तो सभी डेटा एक्सेस SRAM पर किया जा सकता है। | ||

ओवरहेड्स (एसआरएएम क्षमता) को कम करके फ्लैश मेमोरी पर पूर्वानुमान ग्राफ़ को सहेजने के लिए, प्रत्येक नियमित नोड की बाद की एलबीए जानकारी संबंधित पृष्ठ के अतिरिक्त क्षेत्र में सहेजी जाती है। ऐसा इसलिए है क्योंकि वर्तमान कार्यान्वयन में किसी पृष्ठ के अतिरिक्त क्षेत्र में अप्रयुक्त स्थान होता है, और किसी पृष्ठ की रीडिंग आमतौर पर उसके डेटा और अतिरिक्त क्षेत्रों की रीडिंग के साथ-साथ आती है। ऐसे में, नियमित नोड की अगली एलबीए जानकारी तक पहुंच बिना किसी अतिरिक्त लागत के होती है। चूँकि | ओवरहेड्स (एसआरएएम क्षमता) को कम करके फ्लैश मेमोरी पर पूर्वानुमान ग्राफ़ को सहेजने के लिए, प्रत्येक नियमित नोड की बाद की एलबीए जानकारी संबंधित पृष्ठ के अतिरिक्त क्षेत्र में सहेजी जाती है। ऐसा इसलिए है क्योंकि वर्तमान कार्यान्वयन में किसी पृष्ठ के अतिरिक्त क्षेत्र में अप्रयुक्त स्थान होता है, और किसी पृष्ठ की रीडिंग आमतौर पर उसके डेटा और अतिरिक्त क्षेत्रों की रीडिंग के साथ-साथ आती है। ऐसे में, नियमित नोड की अगली एलबीए जानकारी तक पहुंच बिना किसी अतिरिक्त लागत के होती है। चूँकि शाखा नोड में से अधिक अनुवर्ती एलबीए होते हैं, इसलिए संबंधित पृष्ठ के अतिरिक्त क्षेत्र में जानकारी संग्रहीत करने के लिए पर्याप्त खाली स्थान नहीं हो सकता है। इस प्रकार, सभी शाखा नोड्स की बाद की एलबीए जानकारी को सहेजने के लिए शाखा तालिका बनाए रखी जाती है। शाखा नोड से संबंधित शाखा तालिका का प्रारंभिक प्रविष्टि पता संबंधित पृष्ठ के अतिरिक्त क्षेत्र में सहेजा जा सकता है। प्रारंभिक प्रविष्टि शाखा नोड के बाद के एलबीए की संख्या को रिकॉर्ड करती है, और बाद के एलबीए को प्रारंभिक प्रविष्टि के बाद की प्रविष्टियों में संग्रहीत किया जाता है। शाखा तालिका को फ़्लैश मेमोरी पर सहेजा जा सकता है। [[रन टाइम (प्रोग्राम जीवनचक्र चरण)]] के दौरान, बेहतर प्रदर्शन के लिए पूरी तालिका को SRAM में लोड किया जा सकता है। यदि पर्याप्त SRAM स्थान नहीं है, तो तालिका के कुछ हिस्सों को विक्ट:ऑन डिमांड|ऑन-डिमांड तरीके से लोड किया जा सकता है। | ||

=== प्रीफ़ेच प्रक्रिया === | === प्रीफ़ेच प्रक्रिया === | ||

प्रीफ़ेच प्रक्रिया का उद्देश्य किसी दिए गए पूर्वानुमान ग्राफ़ के आधार पर NAND से डेटा को प्रीफ़ेच करना है, ताकि अधिकांश डेटा एक्सेस SRAM पर हो। मूल विचार ग्राफ़ में एलबीए ऑर्डर का पालन करके डेटा को प्रीफ़ेच करना है। कैश में किसी चयनित पृष्ठ को कुशलतापूर्वक देखने के लिए, कैश प्रबंधन में | प्रीफ़ेच प्रक्रिया का उद्देश्य किसी दिए गए पूर्वानुमान ग्राफ़ के आधार पर NAND से डेटा को प्रीफ़ेच करना है, ताकि अधिकांश डेटा एक्सेस SRAM पर हो। मूल विचार ग्राफ़ में एलबीए ऑर्डर का पालन करके डेटा को प्रीफ़ेच करना है। कैश में किसी चयनित पृष्ठ को कुशलतापूर्वक देखने के लिए, कैश प्रबंधन में [[ वृत्ताकार बफ़र |वृत्ताकार बफ़र]] अपनाया जाता है। NAND फ़्लैश से प्रीफ़ेच किए गए डेटा को कतारबद्ध किया जाता है, जबकि दूसरी ओर, होस्ट में स्थानांतरित किए गए डेटा को कतारबद्ध किया जाता है। प्रीफ़ेच प्रक्रिया लालची एल्गोरिथम तरीके से की जाती है: मान लें कि P1 अंतिम प्रीफ़ेच किया गया पृष्ठ है। यदि P1 नियमित नोड से मेल खाता है, तो वह पृष्ठ जो बाद के LBA से मेल खाता है, प्रीफ़ेच किया गया है। यदि P1 शाखा नोड से मेल खाता है, तो प्रक्रिया को समान आधार और [[राउंड-रॉबिन शेड्यूलिंग]]|राउंड-रॉबिन तरीके से सभी संभावित अगले एलबीए लिंक का पालन करके पृष्ठों को प्रीफ़ेच करना चाहिए। | ||

==2डी नंद का 3डी नंद द्वारा प्रतिस्थापन== | ==2डी नंद का 3डी नंद द्वारा प्रतिस्थापन== | ||

2021 तक, 3D NAND द्वारा 2D NAND प्रतिस्थापन शुरू हो गया है।<ref>https://media.digikey.com/pdf/PCNs/Delkin/EOL_412-0068-00_Rev-A.pdf {{Bare URL PDF|date=March 2022}}</ref> 3डी नंद में प्रति बिट कम लागत और बेहतर विश्वसनीयता के लिए नवीनतम नियंत्रक तकनीक के फायदे हैं।<ref>{{Cite web|url=https://www.embeddedcomputing.com/technology/storage/different-priorities|title = Different Priorities}}</ref> नतीजतन, निम्न जीबी स्तर पर भी, 3डी नंद कोड भंडारण के लिए पसंदीदा विकल्प है।<ref>https://www.flashmemorysummit.com/English/Collaterals/Proceedings/2013/20130814_204C_Thomson.pdf {{Bare URL PDF|date=March 2022}}</ref><ref>[https://www.greenliant.com/products/?inode=51973 2GB storage from Greenliant]</ref> | 2021 तक, 3D NAND द्वारा 2D NAND प्रतिस्थापन शुरू हो गया है।<ref>https://media.digikey.com/pdf/PCNs/Delkin/EOL_412-0068-00_Rev-A.pdf {{Bare URL PDF|date=March 2022}}</ref> 3डी नंद में प्रति बिट कम लागत और बेहतर विश्वसनीयता के लिए नवीनतम नियंत्रक तकनीक के फायदे हैं।<ref>{{Cite web|url=https://www.embeddedcomputing.com/technology/storage/different-priorities|title = Different Priorities}}</ref> नतीजतन, निम्न जीबी स्तर पर भी, 3डी नंद कोड भंडारण के लिए पसंदीदा विकल्प है।<ref>https://www.flashmemorysummit.com/English/Collaterals/Proceedings/2013/20130814_204C_Thomson.pdf {{Bare URL PDF|date=March 2022}}</ref><ref>[https://www.greenliant.com/products/?inode=51973 2GB storage from Greenliant]</ref> | ||

==संदर्भ== | ==संदर्भ== | ||

{{Reflist}} | {{Reflist}} | ||

| Line 29: | Line 25: | ||

* [http://www.edn.com/article/CA6262540.html NAND versus NOR] | * [http://www.edn.com/article/CA6262540.html NAND versus NOR] | ||

* [http://www.samsung.com/global/business/semiconductor/products/fusionmemory/Products_OneNAND.html Samsung OneNAND Flash] | * [http://www.samsung.com/global/business/semiconductor/products/fusionmemory/Products_OneNAND.html Samsung OneNAND Flash] | ||

==बाहरी संबंध== | ==बाहरी संबंध== | ||

* [http://newslab.csie.ntu.edu.tw/~flash/index.php?SelectedItem=AcademicResearches&SelectedGroup=AcademicResearches Flash-Memory Research Group] | * [http://newslab.csie.ntu.edu.tw/~flash/index.php?SelectedItem=AcademicResearches&SelectedGroup=AcademicResearches Flash-Memory Research Group] | ||

Revision as of 17:42, 4 August 2023

जबकि फ्लैश मेमोरी अपनी गैर-अस्थिरता, शॉक-प्रतिरोध, छोटे आकार और कम ऊर्जा खपत के कारण अंतः स्थापित प्रणालियाँ में सबसे लोकप्रिय स्टोरेज में से बनी हुई है, इसका अनुप्रयोग इसके मूल डिजाइन से कहीं अधिक बढ़ गया है। अपने मूल डिजाइन के आधार पर, NOR फ्लैश मेमोरी को प्रोग्राम के बाइनरी कोड को स्टोर करने के लिए डिज़ाइन किया गया है क्योंकि यह XIP (eXecute-In-Place) और रीड ऑपरेशंस में उच्च प्रदर्शन का समर्थन करता है, जबकि NAND फ्लैश मेमोरी का उपयोग इसकी कम कीमत के कारण डेटा स्टोरेज के रूप में किया जाता है। और NOR फ़्लैश की तुलना में लिखने/मिटाने के कार्यों में उच्च प्रदर्शन। हाल के वर्षों में, NAND फ़्लैश की कीमत NOR फ़्लैश की तुलना में बहुत तेज़ी से कम हुई है। इस प्रकार, अंततः हार्डवेयर लागत को कम करने के लिए, NOR फ्लैश को बदलने के लिए NAND फ्लैश का उपयोग करना (मजबूत बाजार मांग से प्रेरित) एम्बेडेड-सिस्टम डिजाइन में नया चलन बन गया है, खासकर मोबाइल फोन और आर्केड खेल पर।

सिंहावलोकन

प्रतिस्थापन फ़्लैश मेमोरी के अच्छी तरह से डिज़ाइन किए गए प्रबंधन पर निर्भर करता है, जो या तो होस्ट सिस्टम पर सॉफ़्टवेयर (एक कच्चे माध्यम के रूप में) या उसके उपकरणों के अंदर हार्डवेयर सर्किट/फर्मवेयर द्वारा किया जाता है। यहां, सीमित मेमोरी-स्पेस आवश्यकताओं और कुशल कार्यान्वयन के साथ कुशल भविष्यवाणी तंत्र प्रस्तावित है। भविष्यवाणी तंत्र कार्यशील सेट अवधारणा को अपनाकर भविष्यवाणी ग्राफ बनाने के लिए कार्यक्रम निष्पादन के पहुंच पैटर्न एकत्र करता है। पूर्वानुमान ग्राफ़ के अनुसार, पूर्वानुमान तंत्र डेटा (/कोड) को स्थैतिक रैंडम-एक्सेस मेमोरी कैश में प्रीफ़ेच करता है, ताकि कैश मिस रेट को कम किया जा सके। इसलिए, प्रोग्राम निष्पादन के प्रदर्शन में सुधार होता है और NAND और NOR के बीच पढ़ने के प्रदर्शन का अंतर प्रभावी ढंग से भर जाता है। बूट कोड के लिए NAND फ़्लैश का उपयोग करने के लिए कोड को छाया देने के लिए DRAM के उपयोग की आवश्यकता होती है।[1]

एक प्रभावी प्रीफ़ेचिंग रणनीति

मेमोरी पदानुक्रम में लोकप्रिय कैश (कंप्यूटिंग) विचारों से अलग, इस दृष्टिकोण का लक्ष्य एप्लिकेशन-उन्मुख कैशिंग तंत्र है, जो अनुप्रयोगों के दिए गए निष्पादन निशान के आधार पर भविष्यवाणी-सहायता प्रीफ़ेचिंग को अपनाता है। एम्बेडेड सिस्टम के डिज़ाइन को अनुप्रयोगों के सीमित सेट के साथ माना जाता है, जैसे मोबाइल फोन में चयनित सिस्टम प्रोग्राम का सेट या मनोरंजन-पार्क मशीनों के आर्केड गेम। इसके अलावा, कार्यान्वयन में SRAM क्षमता और कंप्यूटिंग शक्ति बाधित है।

हार्डवेयर आर्किटेक्चर

हार्डवेयर डिज़ाइन में चार आवश्यक घटक शामिल हैं: होस्ट इंटरफ़ेस, SRAM (कैश), NAND फ़्लैश मेमोरी और नियंत्रण तर्क। NAND और NOR के बीच प्रदर्शन अंतर को भरने के लिए, SRAM NAND पर डेटा एक्सेस के लिए कैश परत के रूप में कार्य करता है। होस्ट इंटरफ़ेस पते और डेटा कंप्यूटर बस के माध्यम से होस्ट सिस्टम के साथ संचार के लिए जिम्मेदार है। सबसे महत्वपूर्ण बात यह है कि नियंत्रण तर्क कैशिंग गतिविधि का प्रबंधन करता है और NAND फ़्लैश और SRAM के साथ NOR फ़्लैश का सेवा अनुकरण प्रदान करता है; सिस्टम के प्रदर्शन को बेहतर बनाने के लिए इसमें बुद्धिमान भविष्यवाणी तंत्र लागू होना चाहिए। नियंत्रण तर्क में दो प्रमुख घटक हैं: कनवर्टर SRAM कैश के साथ NAND फ्लैश पर NOR फ्लैश एक्सेस का अनुकरण करता है, जहां एड्रेस ट्रांसलेशन बाइट एड्रेसिंग (NOR के लिए) से तार्किक ब्लॉक पता (LBA) एड्रेसिंग (NAND के लिए) में किया जाना चाहिए। ध्यान दें कि प्रत्येक 512B/2KB NAND पृष्ठ क्रमशः और चार LBA से मेल खाता है। प्रीफ़ेच प्रक्रिया NAND से SRAM में डेटा प्रीफ़ेच करने का प्रयास करती है ताकि NOR एक्सेस की हिट दर SRAM से अधिक हो। प्रक्रिया को एकत्र किए गए निशानों के सेट के माध्यम से लक्ष्य एप्लिकेशन के व्यवहार को पार्स करना और निकालना चाहिए। एकत्रित निशानों से निकाले गए एक्सेस पैटर्न के अनुसार, प्रक्रिया भविष्यवाणी जानकारी उत्पन्न करती है, जिसे भविष्यवाणी ग्राफ के रूप में जाना जाता है।

भविष्यवाणी ग्राफ

NOR (या NAND) पर एप्लिकेशन निष्पादन के एक्सेस पैटर्न में LBA का क्रम होता है। जैसे ही कोई एप्लिकेशन कई बार चलता है, एप्लिकेशन निष्पादन के संभावित एक्सेस पैटर्न की "वस्तुतः" पूरी तस्वीर दिखाई दे सकती है। चूंकि अधिकांश एप्लिकेशन निष्पादन इनपुट-निर्भर या डेटा-संचालित होते हैं, इसलिए किसी दिए गए एलबीए के बाद से अधिक एलबीए हो सकते हैं, जहां प्रत्येक एलबीए ग्राफ़ में नोड से मेल खाता है। से अधिक अनुवर्ती एलबीए वाले नोड्स को शाखा नोड कहा जाता है, और अन्य को नियमित नोड कहा जाता है। वह ग्राफ़ जो एक्सेस पैटर्न से मेल खाता है उसे विशिष्ट एप्लिकेशन का पूर्वानुमान ग्राफ़ कहा जाता है। यदि NAND फ़्लैश में पेजों को समय-समय पर प्रीफ़ेच किया जा सकता है, और कैशिंग के लिए पर्याप्त SRAM स्थान है, तो सभी डेटा एक्सेस SRAM पर किया जा सकता है।

ओवरहेड्स (एसआरएएम क्षमता) को कम करके फ्लैश मेमोरी पर पूर्वानुमान ग्राफ़ को सहेजने के लिए, प्रत्येक नियमित नोड की बाद की एलबीए जानकारी संबंधित पृष्ठ के अतिरिक्त क्षेत्र में सहेजी जाती है। ऐसा इसलिए है क्योंकि वर्तमान कार्यान्वयन में किसी पृष्ठ के अतिरिक्त क्षेत्र में अप्रयुक्त स्थान होता है, और किसी पृष्ठ की रीडिंग आमतौर पर उसके डेटा और अतिरिक्त क्षेत्रों की रीडिंग के साथ-साथ आती है। ऐसे में, नियमित नोड की अगली एलबीए जानकारी तक पहुंच बिना किसी अतिरिक्त लागत के होती है। चूँकि शाखा नोड में से अधिक अनुवर्ती एलबीए होते हैं, इसलिए संबंधित पृष्ठ के अतिरिक्त क्षेत्र में जानकारी संग्रहीत करने के लिए पर्याप्त खाली स्थान नहीं हो सकता है। इस प्रकार, सभी शाखा नोड्स की बाद की एलबीए जानकारी को सहेजने के लिए शाखा तालिका बनाए रखी जाती है। शाखा नोड से संबंधित शाखा तालिका का प्रारंभिक प्रविष्टि पता संबंधित पृष्ठ के अतिरिक्त क्षेत्र में सहेजा जा सकता है। प्रारंभिक प्रविष्टि शाखा नोड के बाद के एलबीए की संख्या को रिकॉर्ड करती है, और बाद के एलबीए को प्रारंभिक प्रविष्टि के बाद की प्रविष्टियों में संग्रहीत किया जाता है। शाखा तालिका को फ़्लैश मेमोरी पर सहेजा जा सकता है। रन टाइम (प्रोग्राम जीवनचक्र चरण) के दौरान, बेहतर प्रदर्शन के लिए पूरी तालिका को SRAM में लोड किया जा सकता है। यदि पर्याप्त SRAM स्थान नहीं है, तो तालिका के कुछ हिस्सों को विक्ट:ऑन डिमांड|ऑन-डिमांड तरीके से लोड किया जा सकता है।

प्रीफ़ेच प्रक्रिया

प्रीफ़ेच प्रक्रिया का उद्देश्य किसी दिए गए पूर्वानुमान ग्राफ़ के आधार पर NAND से डेटा को प्रीफ़ेच करना है, ताकि अधिकांश डेटा एक्सेस SRAM पर हो। मूल विचार ग्राफ़ में एलबीए ऑर्डर का पालन करके डेटा को प्रीफ़ेच करना है। कैश में किसी चयनित पृष्ठ को कुशलतापूर्वक देखने के लिए, कैश प्रबंधन में वृत्ताकार बफ़र अपनाया जाता है। NAND फ़्लैश से प्रीफ़ेच किए गए डेटा को कतारबद्ध किया जाता है, जबकि दूसरी ओर, होस्ट में स्थानांतरित किए गए डेटा को कतारबद्ध किया जाता है। प्रीफ़ेच प्रक्रिया लालची एल्गोरिथम तरीके से की जाती है: मान लें कि P1 अंतिम प्रीफ़ेच किया गया पृष्ठ है। यदि P1 नियमित नोड से मेल खाता है, तो वह पृष्ठ जो बाद के LBA से मेल खाता है, प्रीफ़ेच किया गया है। यदि P1 शाखा नोड से मेल खाता है, तो प्रक्रिया को समान आधार और राउंड-रॉबिन शेड्यूलिंग|राउंड-रॉबिन तरीके से सभी संभावित अगले एलबीए लिंक का पालन करके पृष्ठों को प्रीफ़ेच करना चाहिए।

2डी नंद का 3डी नंद द्वारा प्रतिस्थापन

2021 तक, 3D NAND द्वारा 2D NAND प्रतिस्थापन शुरू हो गया है।[2] 3डी नंद में प्रति बिट कम लागत और बेहतर विश्वसनीयता के लिए नवीनतम नियंत्रक तकनीक के फायदे हैं।[3] नतीजतन, निम्न जीबी स्तर पर भी, 3डी नंद कोड भंडारण के लिए पसंदीदा विकल्प है।[4][5]