प्राथमिकता एनकोडर: Difference between revisions

(Created page with "प्राथमिकता एनकोडर एक विद्युत सर्किट या कलन विधि है जो कई बाइन...") |

No edit summary |

||

| Line 1: | Line 1: | ||

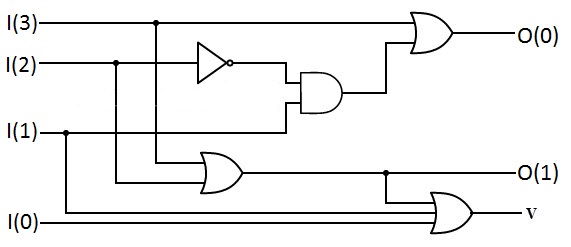

प्राथमिकता एनकोडर एक [[ विद्युत सर्किट ]] या [[कलन विधि]] है जो कई [[बाइनरी कोड]] इनपुट को कम संख्या में आउटपुट में | प्राथमिकता एनकोडर एक [[ विद्युत सर्किट | विद्युत परिपथ]] या [[कलन विधि|एल्गोरिदम]] है, जो कई [[बाइनरी कोड]] इनपुट को कम संख्या में आउटपुट में कम्प्रेस करता है। प्राथमिकता एनकोडर का आउटपुट शून्य से प्रारंभ होने वाली सबसे महत्वपूर्ण सक्रिय लाइन के सूचकांक का द्विआधारी प्रतिनिधित्व है। इनका उपयोग अधिकांशतः सर्वोच्च प्राथमिकता वाले इंटरप्ट इनपुट पर कार्य करके इंटरप्ट अनुरोधों को नियंत्रित करने के लिए किया जाता है।[[File:A 4-2 Priority Encoder .jpg|alt=A 4:2 प्राथमिकता एनकोडर|अंगूठा|486x486पीएक्स|ए 4:2 प्राथमिकता एनकोडर|केंद्र]] | ||

[[File:A 4-2 Priority Encoder .jpg|alt=A 4:2 प्राथमिकता एनकोडर|अंगूठा|486x486पीएक्स|ए 4:2 प्राथमिकता एनकोडर|केंद्र]]यदि एक ही समय में दो या दो से अधिक इनपुट दिए जाते हैं, तो सर्वोच्च प्राथमिकता | |||

यदि एक ही समय में दो या दो से अधिक इनपुट दिए जाते हैं, तो सर्वोच्च प्राथमिकता वाले इनपुट को प्राथमिकता दी जाएगी।<ref>M. Morris Mano, Michael D. Ciletti, "Digital Design", 4th Edition, Prentice Hall, 2006, {{ISBN|978-0-13-198924-5}}.</ref> एकल बिट 4 से 2 एनकोडर का एक उदाहरण दिखाया गया है, जहां उच्चतम-प्राथमिकता वाले इनपुट बाईं ओर हैं और x एक अप्रासंगिक मान को इंगित करता है - अर्थात् वहां कोई भी इनपुट मान समान आउटपुट देता है, क्योंकि इसे उच्च-प्राथमिकता वाले इनपुट द्वारा प्रतिस्थापित किया जाता है। (सामान्यतः सम्मिलित है{{efn|For instance, the [[List of 7400-series integrated circuits|74x147]] 10-to-4 [[BCD (character encoding)|BCD]] priority encoder does not have a dedicated output valid signal. However, invalid is indicated by all outputs simultaneously high. https://www.ti.com/lit/ds/symlink/sn74ls148.pdf}}) "v" आउटपुट इंगित करता है कि इनपुट वैध है या नहीं है। | |||

{| class="wikitable" | {| class="wikitable" | ||

| Line 22: | Line 23: | ||

| 1 || x || x || x ||style="border-left:2px solid #000;"| 1 || 1 || 1 | | 1 || x || x || x ||style="border-left:2px solid #000;"| 1 || 1 || 1 | ||

|} | |} | ||

बड़े एनकोडर बनाने के लिए प्राथमिकता एनकोडर को | बड़े एनकोडर बनाने के लिए प्राथमिकता एनकोडर को सरलता से एरे में जोड़ा जा सकता है, जैसे छह 4-से-2 प्राथमिकता एनकोडर से बना एक 16-से-4 एनकोडर - चार 4-से-2 एनकोडर जिनके सिग्नल स्रोत उनके इनपुट से जुड़े होते हैं, और शेष दो एनकोडर पहले चार के आउटपुट को इनपुट के रूप में लेते हैं। सभी संभावित इनपुट [[कंप्यूटर विन्यास|कॉन्फ़िगरेशन]] को संभालने की स्थिति में, प्राथमिकता एनकोडर एक सरल एनकोडर परिपथ में संशोधन है। | ||

== प्राथमिकता एनकोडर का पुनरावर्ती निर्माण<ref>{{Cite thesis|title=Architecture of block-RAM-based massively parallel memory structures : multi-ported memories and content-addressable memories|url=https://open.library.ubc.ca/cIRcle/collections/ubctheses/24/items/1.0314219|publisher=University of British Columbia|date=2016|first=Ameer M. S.|last=Abdelhadi}}</ref><ref>{{Cite book|last1=Abdelhadi|first1=Ameer M.S.|last2=Lemieux|first2=Guy G.F.|title=2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines |chapter=Modular SRAM-Based Binary Content-Addressable Memories |date=May 2015|pages=207–214|doi=10.1109/FCCM.2015.69|isbn=978-1-4799-9969-9|s2cid=16985129 }}</ref><ref>{{Cite book|last1=Abdelhadi|first1=Ameer M. S.|last2=Lemieux|first2=Guy G. F.|title=2014 International Conference on Field-Programmable Technology (FPT) |chapter=Deep and narrow binary content-addressable memories using FPGA-based BRAMs |date=December 2014|pages=318–321|doi=10.1109/FPT.2014.7082808|isbn=978-1-4799-6245-7|s2cid=2074456 }}</ref> == | == प्राथमिकता एनकोडर का पुनरावर्ती निर्माण<ref>{{Cite thesis|title=Architecture of block-RAM-based massively parallel memory structures : multi-ported memories and content-addressable memories|url=https://open.library.ubc.ca/cIRcle/collections/ubctheses/24/items/1.0314219|publisher=University of British Columbia|date=2016|first=Ameer M. S.|last=Abdelhadi}}</ref><ref>{{Cite book|last1=Abdelhadi|first1=Ameer M.S.|last2=Lemieux|first2=Guy G.F.|title=2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines |chapter=Modular SRAM-Based Binary Content-Addressable Memories |date=May 2015|pages=207–214|doi=10.1109/FCCM.2015.69|isbn=978-1-4799-9969-9|s2cid=16985129 }}</ref><ref>{{Cite book|last1=Abdelhadi|first1=Ameer M. S.|last2=Lemieux|first2=Guy G. F.|title=2014 International Conference on Field-Programmable Technology (FPT) |chapter=Deep and narrow binary content-addressable memories using FPGA-based BRAMs |date=December 2014|pages=318–321|doi=10.1109/FPT.2014.7082808|isbn=978-1-4799-6245-7|s2cid=2074456 }}</ref> == | ||

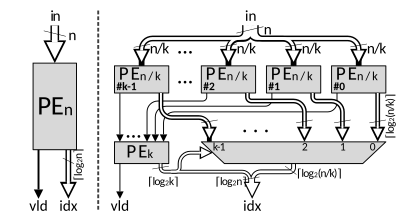

एक प्राथमिकता-एनकोडर, जिसे | एक प्राथमिकता-एनकोडर, जिसे लीडिंग शून्य डिटेक्टर (एलजेडडी) या लीडिंग शून्य काउंटर (एलजेडसी) भी कहा जाता है, एक <math>n</math>-बिट इनपुट वेक्टर प्राप्त करता है और इनपुट वेक्टर में पहले बाइनरी '1' के सूचकांक का पता लगाता है। एक वैध संकेत इंगित करता है कि क्या इनपुट वेक्टर में कोई बाइनरी '1' पाया गया था, इसलिए सूचकांक वैध है। | ||

'''प्राथमिकता-एनकोडर को रिकर्सन द्वारा कुशलतापूर्वक निर्मित किया जा सकता है। प्रत्येक टुकड़े के लिए 𝑛/𝑘 की कम चौड़ाई वाला एक प्राथमिकता एनकोडर प्रयुक्त किया जाता है। प्रत्येक का वैध बिट पता लगाने के लिए एक k बिट में जाता है। पहला वैध टुकड़ा. इस टुकड़े का स्थान टी का ऊपरी भाग है''' | |||

प्राथमिकता-एनकोडर को रिकर्सन द्वारा कुशलतापूर्वक निर्मित किया जा सकता है। इनपुट वेक्टर को <math>n/k</math> बिट्स के साथ <math>k</math> समान टुकड़ों में विभाजित किया गया है। एक प्राथमिकता एनकोडर <math>\textrm{PE}_{n/k}</math> के साथ प्रत्येक टुकड़े के लिए 𝑛/𝑘 की एक संकीर्ण चौड़ाई प्रयुक्त की जाती है। पहले वैध टुकड़े का पता लगाने के लिए, प्रत्येक <math>k</math> <math>\textrm{PE}_{n/k}</math> का वैध बिट, <math>k</math> बिट <math>\textrm{PE}_{n/k}</math> पर जाता है। इस टुकड़े का स्थान समग्र सूचकांक का उच्च भाग है, और समग्र सूचकांक के निचले हिस्से का उत्पादन करने के लिए टुकड़े के अन्दर ही स्पष्ट स्थान निर्धारित करता है। | |||

'''प्रत्येक का वैध बिटएक को जाता है अंश पहले वैध टुकड़े का पता लगाने के लिए।''' | |||

प्रस्तावित संरचना की गहराई <math>\lceil\log_kn\rceil</math> है, जबकि हार्डवेयर क्षेत्र की जटिलता <math>\mathcal{O}(n)</math> है। यदि अल्टेरा के स्ट्रैटिक्स V या समकक्ष उपकरण का उपयोग किया जाता है, तो उच्च प्रदर्शन और क्षेत्र संपीड़न प्राप्त करने के लिए <math>k=4</math> की अनुशंसा की जाती है, चूँकि मक्स को 6-एलयूटी का उपयोग करके कार्यान्वित किया जा सकता है, इसलिए यह एक संपूर्ण एएलएम है। | |||

'''उच्च प्रदर्शन और क्षेत्र संपीड़न प्राप्त करने के लिए इसकी की जाती है, क्योंकि को 6-, इसलिए एक संपूर्ण का उपयोग करके कार्यान्वित किया जा सकता है।''' | |||

पुनरावर्ती प्राथमिकता-एनकोडर के लिए एक ओपन-सोर्स वेरिलॉग जनरेटर ऑनलाइन उपलब्ध है।<ref name=II2DCAM>{{Cite web|url=https://github.com/AmeerAbdelhadi/Indirectly-Indexed-2D-Binary-Content-Addressable-Memory-BCAM/blob/master/pe |first1=A.M.S. |last1=Abdelhadi |first2=G.G.F. |last2=Lemieux |title=Modular SRAM-based Indirectly-indexed 2D Binary Content Addressable Memory II2DCAM |publisher=The University of British Columbia |date=2014 }}<br/> | पुनरावर्ती प्राथमिकता-एनकोडर के लिए एक ओपन-सोर्स वेरिलॉग जनरेटर ऑनलाइन उपलब्ध है।<ref name="II2DCAM">{{Cite web|url=https://github.com/AmeerAbdelhadi/Indirectly-Indexed-2D-Binary-Content-Addressable-Memory-BCAM/blob/master/pe |first1=A.M.S. |last1=Abdelhadi |first2=G.G.F. |last2=Lemieux |title=Modular SRAM-based Indirectly-indexed 2D Binary Content Addressable Memory II2DCAM |publisher=The University of British Columbia |date=2014 }}<br /> | ||

{{cite book |first1=A.M.S. |last1=Abdelhadi |first2=G.G.F. |last2=Lemieux |chapter=Modular SRAM-Based Binary Content-Addressable Memories |chapter-url=http://www.ece.ubc.ca/~lemieux/publications/abdelhadi-fccm2015.pdf |title=2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines |publisher=IEEE |location= |date=2015 |isbn=978-1-4799-9969-9 |pages=207–214 |doi=10.1109/FCCM.2015.69|s2cid=16985129 }}</ref> | {{cite book |first1=A.M.S. |last1=Abdelhadi |first2=G.G.F. |last2=Lemieux |chapter=Modular SRAM-Based Binary Content-Addressable Memories |chapter-url=http://www.ece.ubc.ca/~lemieux/publications/abdelhadi-fccm2015.pdf |title=2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines |publisher=IEEE |location= |date=2015 |isbn=978-1-4799-9969-9 |pages=207–214 |doi=10.1109/FCCM.2015.69|s2cid=16985129 }}</ref> | ||

[[File:PE-recursion.svg|alt=Priority-एनकोडर (बाएं) प्रतीक (दाएं) पुनरावर्ती परिभाषा।|केंद्र|अंगूठा|416x416px|प्राथमिकता-एनकोडर (बाएं) प्रतीक (दाएं) पुनरावर्ती परिभाषा।]]वेरिलॉग में प्राथमिकता एनकोडर का व्यवहारिक विवरण इस प्रकार है।<ref name=II2DCAM/><सिंटैक्सहाइलाइट लैंग= वेरिलॉग लाइन= 1 > | |||

[[File:PE-recursion.svg|alt=Priority-एनकोडर (बाएं) प्रतीक (दाएं) पुनरावर्ती परिभाषा।|केंद्र|अंगूठा|416x416px|प्राथमिकता-एनकोडर (बाएं) प्रतीक (दाएं) पुनरावर्ती परिभाषा।]] | |||

वेरिलॉग में प्राथमिकता एनकोडर का व्यवहारिक विवरण इस प्रकार है।<ref name="II2DCAM" /><syntaxhighlight lang="abl"> | |||

// behavioural description of priority enconder; | |||

// https://github.com/AmeerAbdelhadi/Indirectly-Indexed-2D-Binary-Content-Addressable-Memory-BCAM | |||

module pe_bhv | |||

#( parameter OHW = 512 ) // encoder one-hot input width | |||

( input clk , // clock for pipelined priority encoder | |||

input rst , // registers reset for pipelined priority encoder | |||

input [ OHW -1:0] oht , // one-hot input / [ OHW -1:0] | |||

output reg [`log2(OHW)-1:0] bin , // first '1' index/ [`log2(OHW)-1:0] | |||

output reg vld ); // binary is valid if one was found | |||

// use while loop for non fixed loop length | |||

// synthesizable well with Intel's QuartusII | |||

always @(*) begin | |||

bin = {`log2(OHW){1'b0}}; | |||

vld = oht[bin] ; | |||

while ((!vld) && (bin!=(OHW-1))) begin | |||

bin = bin + 1 ; | |||

vld = oht[bin]; | |||

end | |||

end | |||

endmodule | |||

</syntaxhighlight><सिंटैक्सहाइलाइट लैंग= वेरिलॉग लाइन= 1 > | |||

// प्राथमिकता एनकॉन्डर का व्यवहारिक विवरण; | // प्राथमिकता एनकॉन्डर का व्यवहारिक विवरण; | ||

// | // | ||

मॉड्यूल pe_bhv | मॉड्यूल pe_bhv | ||

| Line 62: | Line 96: | ||

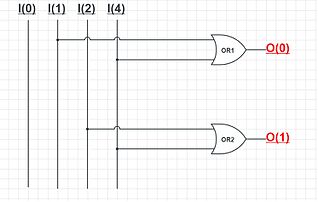

[[File:A Simple 4-2 encoder using or gate.jpg|alt=A simple 4:2 OR गेट का उपयोग करने वाला एनकोडर.|thumb|318x318px|OR गेट का उपयोग करने वाला एक सरल 4:2 एनकोडर।]] | [[File:A Simple 4-2 encoder using or gate.jpg|alt=A simple 4:2 OR गेट का उपयोग करने वाला एनकोडर.|thumb|318x318px|OR गेट का उपयोग करने वाला एक सरल 4:2 एनकोडर।]] | ||

{{Main| | {{Main|एनकोडर (डिजिटल)}} | ||

एक [[एनकोडर (डिजिटल)]] | एक [[एनकोडर (डिजिटल)]] परिपथ वन-हॉट से बाइनरी कनवर्टर है। अर्थात यदि 2<sup>''n''</sup> इनपुट लाइनें हैं, और अधिकतम उनमें से केवल एक ही कभी ऊंची होगी, तो इस 'हॉट' लाइन का बाइनरी कोड ''n''-बिट आउटपुट लाइनों पर निर्मित होता है। | ||

==टिप्पणियाँ== | ==टिप्पणियाँ== | ||

Revision as of 08:53, 10 August 2023

प्राथमिकता एनकोडर एक विद्युत परिपथ या एल्गोरिदम है, जो कई बाइनरी कोड इनपुट को कम संख्या में आउटपुट में कम्प्रेस करता है। प्राथमिकता एनकोडर का आउटपुट शून्य से प्रारंभ होने वाली सबसे महत्वपूर्ण सक्रिय लाइन के सूचकांक का द्विआधारी प्रतिनिधित्व है। इनका उपयोग अधिकांशतः सर्वोच्च प्राथमिकता वाले इंटरप्ट इनपुट पर कार्य करके इंटरप्ट अनुरोधों को नियंत्रित करने के लिए किया जाता है।

यदि एक ही समय में दो या दो से अधिक इनपुट दिए जाते हैं, तो सर्वोच्च प्राथमिकता वाले इनपुट को प्राथमिकता दी जाएगी।[1] एकल बिट 4 से 2 एनकोडर का एक उदाहरण दिखाया गया है, जहां उच्चतम-प्राथमिकता वाले इनपुट बाईं ओर हैं और x एक अप्रासंगिक मान को इंगित करता है - अर्थात् वहां कोई भी इनपुट मान समान आउटपुट देता है, क्योंकि इसे उच्च-प्राथमिकता वाले इनपुट द्वारा प्रतिस्थापित किया जाता है। (सामान्यतः सम्मिलित है[lower-alpha 1]) "v" आउटपुट इंगित करता है कि इनपुट वैध है या नहीं है।

| I3 | I2 | I1 | I0 | O1 | O0 | v |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | x | x | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | x | 0 | 1 | 1 |

| 0 | 1 | x | x | 1 | 0 | 1 |

| 1 | x | x | x | 1 | 1 | 1 |

बड़े एनकोडर बनाने के लिए प्राथमिकता एनकोडर को सरलता से एरे में जोड़ा जा सकता है, जैसे छह 4-से-2 प्राथमिकता एनकोडर से बना एक 16-से-4 एनकोडर - चार 4-से-2 एनकोडर जिनके सिग्नल स्रोत उनके इनपुट से जुड़े होते हैं, और शेष दो एनकोडर पहले चार के आउटपुट को इनपुट के रूप में लेते हैं। सभी संभावित इनपुट कॉन्फ़िगरेशन को संभालने की स्थिति में, प्राथमिकता एनकोडर एक सरल एनकोडर परिपथ में संशोधन है।

प्राथमिकता एनकोडर का पुनरावर्ती निर्माण[2][3][4]

एक प्राथमिकता-एनकोडर, जिसे लीडिंग शून्य डिटेक्टर (एलजेडडी) या लीडिंग शून्य काउंटर (एलजेडसी) भी कहा जाता है, एक -बिट इनपुट वेक्टर प्राप्त करता है और इनपुट वेक्टर में पहले बाइनरी '1' के सूचकांक का पता लगाता है। एक वैध संकेत इंगित करता है कि क्या इनपुट वेक्टर में कोई बाइनरी '1' पाया गया था, इसलिए सूचकांक वैध है।

प्राथमिकता-एनकोडर को रिकर्सन द्वारा कुशलतापूर्वक निर्मित किया जा सकता है। प्रत्येक टुकड़े के लिए 𝑛/𝑘 की कम चौड़ाई वाला एक प्राथमिकता एनकोडर प्रयुक्त किया जाता है। प्रत्येक का वैध बिट पता लगाने के लिए एक k बिट में जाता है। पहला वैध टुकड़ा. इस टुकड़े का स्थान टी का ऊपरी भाग है

प्राथमिकता-एनकोडर को रिकर्सन द्वारा कुशलतापूर्वक निर्मित किया जा सकता है। इनपुट वेक्टर को बिट्स के साथ समान टुकड़ों में विभाजित किया गया है। एक प्राथमिकता एनकोडर के साथ प्रत्येक टुकड़े के लिए 𝑛/𝑘 की एक संकीर्ण चौड़ाई प्रयुक्त की जाती है। पहले वैध टुकड़े का पता लगाने के लिए, प्रत्येक का वैध बिट, बिट पर जाता है। इस टुकड़े का स्थान समग्र सूचकांक का उच्च भाग है, और समग्र सूचकांक के निचले हिस्से का उत्पादन करने के लिए टुकड़े के अन्दर ही स्पष्ट स्थान निर्धारित करता है।

प्रत्येक का वैध बिटएक को जाता है अंश पहले वैध टुकड़े का पता लगाने के लिए।

प्रस्तावित संरचना की गहराई है, जबकि हार्डवेयर क्षेत्र की जटिलता है। यदि अल्टेरा के स्ट्रैटिक्स V या समकक्ष उपकरण का उपयोग किया जाता है, तो उच्च प्रदर्शन और क्षेत्र संपीड़न प्राप्त करने के लिए की अनुशंसा की जाती है, चूँकि मक्स को 6-एलयूटी का उपयोग करके कार्यान्वित किया जा सकता है, इसलिए यह एक संपूर्ण एएलएम है।

उच्च प्रदर्शन और क्षेत्र संपीड़न प्राप्त करने के लिए इसकी की जाती है, क्योंकि को 6-, इसलिए एक संपूर्ण का उपयोग करके कार्यान्वित किया जा सकता है।

पुनरावर्ती प्राथमिकता-एनकोडर के लिए एक ओपन-सोर्स वेरिलॉग जनरेटर ऑनलाइन उपलब्ध है।[5]

वेरिलॉग में प्राथमिकता एनकोडर का व्यवहारिक विवरण इस प्रकार है।[5]

// behavioural description of priority enconder;

// https://github.com/AmeerAbdelhadi/Indirectly-Indexed-2D-Binary-Content-Addressable-Memory-BCAM

module pe_bhv

#( parameter OHW = 512 ) // encoder one-hot input width

( input clk , // clock for pipelined priority encoder

input rst , // registers reset for pipelined priority encoder

input [ OHW -1:0] oht , // one-hot input / [ OHW -1:0]

output reg [`log2(OHW)-1:0] bin , // first '1' index/ [`log2(OHW)-1:0]

output reg vld ); // binary is valid if one was found

// use while loop for non fixed loop length

// synthesizable well with Intel's QuartusII

always @(*) begin

bin = {`log2(OHW){1'b0}};

vld = oht[bin] ;

while ((!vld) && (bin!=(OHW-1))) begin

bin = bin + 1 ;

vld = oht[bin];

end

end

endmodule

<सिंटैक्सहाइलाइट लैंग= वेरिलॉग लाइन= 1 >

// प्राथमिकता एनकॉन्डर का व्यवहारिक विवरण; //

मॉड्यूल pe_bhv

#(पैरामीटर OHW = 512) // एनकोडर एक-हॉट इनपुट चौड़ाई

(इनपुट सीएलके, // पाइपलाइन प्राथमिकता एनकोडर के लिए घड़ी

इनपुट आरएसटी, // पाइपलाइन प्राथमिकता एनकोडर के लिए रजिस्टर रीसेट

इनपुट [ओएचडब्ल्यू -1:0] ओएचटी, // एक-हॉट इनपुट / [ओएचडब्ल्यू -1:0]

आउटपुट reg [`log2(OHW)-1:0] बिन, // पहला '1' इंडेक्स/ [`log2(OHW)-1:0]

आउटपुट रेग वीएलडी); // यदि कोई पाया गया तो बाइनरी मान्य है

// गैर निश्चित लूप लंबाई के लिए while लूप का उपयोग करें

// इंटेल के क्वार्टस II के साथ अच्छी तरह से संश्लेषित

हमेशा @(*) प्रारंभ करें

बिन = {`log2(OHW){1'b0}};

वीएलडी = ओएचटी[बिन] ;

जबकि ((!vld) && (bin!=(OHW-1))) शुरू होता है

बिन = बिन + 1 ;

वीएलडी = ओएचटी[बिन];

अंत

अंत

एंडमॉड्यूल </सिंटैक्सहाइलाइट>

सरल एनकोडर

एक एनकोडर (डिजिटल) परिपथ वन-हॉट से बाइनरी कनवर्टर है। अर्थात यदि 2n इनपुट लाइनें हैं, और अधिकतम उनमें से केवल एक ही कभी ऊंची होगी, तो इस 'हॉट' लाइन का बाइनरी कोड n-बिट आउटपुट लाइनों पर निर्मित होता है।

टिप्पणियाँ

- ↑ For instance, the 74x147 10-to-4 BCD priority encoder does not have a dedicated output valid signal. However, invalid is indicated by all outputs simultaneously high. https://www.ti.com/lit/ds/symlink/sn74ls148.pdf

संदर्भ

- ↑ M. Morris Mano, Michael D. Ciletti, "Digital Design", 4th Edition, Prentice Hall, 2006, ISBN 978-0-13-198924-5.

- ↑ Abdelhadi, Ameer M. S. (2016). Architecture of block-RAM-based massively parallel memory structures : multi-ported memories and content-addressable memories (Thesis). University of British Columbia.

- ↑ Abdelhadi, Ameer M.S.; Lemieux, Guy G.F. (May 2015). "Modular SRAM-Based Binary Content-Addressable Memories". 2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines. pp. 207–214. doi:10.1109/FCCM.2015.69. ISBN 978-1-4799-9969-9. S2CID 16985129.

- ↑ Abdelhadi, Ameer M. S.; Lemieux, Guy G. F. (December 2014). "Deep and narrow binary content-addressable memories using FPGA-based BRAMs". 2014 International Conference on Field-Programmable Technology (FPT). pp. 318–321. doi:10.1109/FPT.2014.7082808. ISBN 978-1-4799-6245-7. S2CID 2074456.

- ↑ 5.0 5.1 Abdelhadi, A.M.S.; Lemieux, G.G.F. (2014). "Modular SRAM-based Indirectly-indexed 2D Binary Content Addressable Memory II2DCAM". The University of British Columbia.

Abdelhadi, A.M.S.; Lemieux, G.G.F. (2015). "Modular SRAM-Based Binary Content-Addressable Memories" (PDF). 2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines. IEEE. pp. 207–214. doi:10.1109/FCCM.2015.69. ISBN 978-1-4799-9969-9. S2CID 16985129.