मेमोरी ज्यामिति: Difference between revisions

No edit summary |

No edit summary |

||

| Line 1: | Line 1: | ||

{{Short description|Internal structure of random-access memory}} | {{Short description|Internal structure of random-access memory}} | ||

'''मेमोरी ज्योमेट्री''' आधुनिक कंप्यूटरों के डिज़ाइनों में [[ रैंडम एक्सेस मेमोरी |रैंडम एक्सेस मेमोरी]] की आंतरिक संरचना का वर्णन करती है। मेमोरी ज्योमेट्री अपने कंप्यूटर को अपग्रेड करने वाले उपभोक्ताओं के लिए चिंता का विषय है क्योंकि ये पुराने मेमोरी कंट्रोलर बाद के कंप्यूटरों के साथ संगत नहीं हो सकते हैं। ओवरलैपिंग संख्या के कारण मेमोरी ज्योमेट्री टर्मिनोलॉजी भ्रमित करने वाली हो सकती है। | '''मेमोरी ज्योमेट्री''' आधुनिक कंप्यूटरों के डिज़ाइनों में [[ रैंडम एक्सेस मेमोरी |रैंडम एक्सेस मेमोरी]] की आंतरिक संरचना का वर्णन करती है। मेमोरी ज्योमेट्री अपने कंप्यूटर को अपग्रेड करने वाले उपभोक्ताओं के लिए चिंता का विषय है क्योंकि ये पुराने मेमोरी कंट्रोलर बाद के कंप्यूटरों के साथ संगत नहीं हो सकते हैं। ओवरलैपिंग संख्या के कारण मेमोरी ज्योमेट्री टर्मिनोलॉजी भ्रमित करने वाली हो सकती है। | ||

| Line 77: | Line 73: | ||

* {{Citation | url = http://www.valueram.com/datasheets/KHX6400D2_1G.pdf | title = KHX6400D2 1G | publisher = Value RAM | type = data sheet | access-date = 2010-08-05 | archive-url = https://web.archive.org/web/20120310062857/http://www.valueram.com/datasheets/KHX6400D2_1G.pdf | archive-date = 2012-03-10 | url-status = dead }}. | * {{Citation | url = http://www.valueram.com/datasheets/KHX6400D2_1G.pdf | title = KHX6400D2 1G | publisher = Value RAM | type = data sheet | access-date = 2010-08-05 | archive-url = https://web.archive.org/web/20120310062857/http://www.valueram.com/datasheets/KHX6400D2_1G.pdf | archive-date = 2012-03-10 | url-status = dead }}. | ||

* {{Citation | url = http://www.intel.com/Assets/PDF/datasheet/307502.pdf | title = 307502 | publisher = Intel | type = data sheet}}. | * {{Citation | url = http://www.intel.com/Assets/PDF/datasheet/307502.pdf | title = 307502 | publisher = Intel | type = data sheet}}. | ||

[[Category: Machine Translated Page]] | [[Category: Machine Translated Page]] | ||

[[Category:Created On 15/08/2023]] | [[Category:Created On 15/08/2023]] | ||

Revision as of 13:11, 11 October 2023

मेमोरी ज्योमेट्री आधुनिक कंप्यूटरों के डिज़ाइनों में रैंडम एक्सेस मेमोरी की आंतरिक संरचना का वर्णन करती है। मेमोरी ज्योमेट्री अपने कंप्यूटर को अपग्रेड करने वाले उपभोक्ताओं के लिए चिंता का विषय है क्योंकि ये पुराने मेमोरी कंट्रोलर बाद के कंप्यूटरों के साथ संगत नहीं हो सकते हैं। ओवरलैपिंग संख्या के कारण मेमोरी ज्योमेट्री टर्मिनोलॉजी भ्रमित करने वाली हो सकती है।

मेमोरी सिस्टम की ज्योमेट्री को एक मल्टी-डायमेंशनल ऐरे के रूप में समझा जा सकता है। प्रत्येक डायमेंशन की अपनी विशेषताएं और भौतिक स्थितियाँ होती है। उदाहरण के लिए मेमोरी मॉड्यूल पर डेटा पिन की संख्या एक डायमेंशन होती है।

भौतिक विशेषताएं

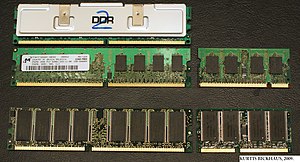

मेमोरी ज्योमेट्री रैंडम एक्सेस मेमोरी मॉड्यूल के लॉजिकल कॉन्फ़िगरेशन का वर्णन करती है लेकिन उपभोक्ताओं के लिए भौतिक कॉन्फ़िगरेशन को समझना सदैव साधारण होता है। मेमोरी ज्योमेट्री को लेकर अधिकांश भ्रम तब होता है जब भौतिक कॉन्फ़िगरेशन लॉजिकल कॉन्फ़िगरेशन को अस्पष्ट कर देता है। रैम की पहली परिभाषित विशेषता फॉर्म फैक्टर है। रैम मॉड्यूल लैपटॉप, प्रिंटर, एम्बेडेड कंप्यूटर और छोटे फॉर्म फैक्टर कंप्यूटर जैसे स्थान सीमित एप्लीकेशनों के लिए कॉम्पैक्ट एसओ-डीआईएमएम मॉड्यूल या डीआईएमएम मॉड्यूल के रूप में हो सकते हैं, जिसका उपयोग प्रायः डेस्कटॉप कंप्यूटरों में किया जाता है।[citation needed]

भौतिक परीक्षण द्वारा निर्धारित अन्य भौतिक विशेषताएँ मेमोरी चिप की संख्याएँ हैं और मेमोरी स्टिक के दोनों किनारे भरे हुए होते हैं जो दो मेमोरी स्टिक की क्षमता के बराबर रैम चिप की संख्या वाले मॉड्यूल मेमोरी त्रुटि का पता लगाने या सुधार का समर्थन नहीं करते हैं। यदि अतिरिक्त रैम चिप (दो की क्षमता के बीच) हैं, तो इसका उपयोग ईसीसी के लिए किया जाता है। रैम मॉड्यूल को किनारों पर और मॉड्यूल के नीचे इंडेंटेशन द्वारा 'कीड' किया जाता है। यह मॉड्यूल की तकनीक और वर्गीकरण को निर्दिष्ट करता है, उदाहरण के लिए यह डीडीआर-2 या डीडीआर-3 है और यह सामान्यतः डेस्कटॉप या सर्वर के लिए उपयुक्त होता है। कीड को सिस्टम में गलत मॉड्यूल को जटिल प्रकार से इंस्टॉल करने के लिए डिज़ाइन किया गया था लेकिन कुंजी में स्थित आवश्यकताओं की तुलना में अधिक आवश्यकताएं हैं। इसमे यह सुनिश्चित करना महत्वपूर्ण है कि मॉड्यूल की कुंजी उस स्लॉट की कुंजी के अनुरूप है या उसके अनुरूप नही है जिसे पर वह अधिकृत करना चाहता है। मॉड्यूल पर अतिरिक्त मेमोरी चिप संकेत हो सकता है जिसे सर्वरों मे हाई पावर मेमोरी सिस्टम के लिए डिजाइन किया गया है[by whom?] और मॉड्यूल बड़े पैमाने पर विणपन सिस्टम के साथ असंगत हो सकता है।[citation needed]

चूंकि इस आलेख का अगला भाग लॉजिकल आर्किटेक्चर को सूचित करता है जो सिस्टम में प्रत्येक संख्या वाले स्लॉट में लॉजिकल स्ट्रक्चर का वर्णन करता है। स्लॉट की भौतिक विशेषताएं स्वयं महत्वपूर्ण हो जाती हैं जब मदरबोर्ड के दस्तावेज़ीकरण या बोर्ड पर लेबल स्लॉट की मूल लॉजिकल संरचना निर्धारित की जाती है।[citation needed] जब एक से अधिक स्लॉट होते हैं तो उन्हें क्रमांकित किया जाता है और जब एक से अधिक चैनल होते हैं तो अलग-अलग स्लॉट को भी उसी प्रकार से कोडित किया जाता है।[citation needed]

लॉजिकल विशेषताएं

1990 के दशक में विशेष कंप्यूटर[which?] प्रारम्भ किए गए थे जहां दो कंप्यूटर जिनमें प्रत्येक का अपना मेमोरी कंट्रोलर होता था जिन्हें लो-लेवल नेटवर्क पर सक्रिय किया जा सकता था। सॉफ़्टवेयर चलाने के लिए किसी भी कंप्यूटर की मेमोरी या सीपीयू का उपयोग किया जा सकता था। वे सामान्यतः एक यूनिट के थे।[clarification needed] इन कंप्यूटरों के लिए नॉन-यूनिफॉर्म मेमोरी आर्किटेक्चर जैसी योजनाओं का उपयोग किया जाता था।[citation needed][citation needed]

चैनल लोकल मेमोरी कंट्रोलर लेवल पर हाई-लेवल स्ट्रक्चर हैं। आधुनिक कंप्यूटर में दो, तीन या इससे भी अधिक चैनल हो सकते हैं। सामान्यतः यह महत्वपूर्ण है कि एक चैनल में प्रत्येक मॉड्यूल के लिए अन्य संख्या वाले चैनलों में से प्रत्येक पर एक ही स्थान पर एक लॉजिकल रूप से समान मॉड्यूल हो सकता है।[citation needed]

मॉड्यूल क्षमता एक मॉड्यूल में कुल स्थान है जिसे बाइट में मापा जाता है या अधिक सामान्यतः मॉड्यूल क्षमता रैंकों की संख्या और रैंक डेनसिटी के उत्पाद के बराबर है जहां रैंक डेनसिटी रैंक डेप्थ और रैंक विड्थ का उत्पाद है।[1] इस विनिर्देश को व्यक्त करने के लिए मानक प्रारूप (रैंक डेप्थ) एमबीटी × (रैंक विड्थ) × (रैंक की संख्या) है।[citation needed]

मेमोरी रैंक एक मेमोरी मॉड्यूल की यूनिट हैं जो समान एड्रेस और डेटा बसों को साझा करती हैं और लो-लेवल एड्रेस में चिप चयन (सीएस) द्वारा चुनी जाती हैं। उदाहरण के लिए प्रत्येक फेज़ पर 8 चिप वाला एक मेमोरी मॉड्यूल प्रत्येक चिप में 8-बिट विड्थ डेटा बस होता है और कुल 2 रैंक के लिए प्रत्येक फेज के लिए एक रैंक होता है यदि हम एक रैंक को 64 बिट विड्थ से परिभाषित करते हैं तब 128 Mib × 16 के साथ माइक्रोन टेक्नोलॉजी MT47H128M16 चिप से बना एक मॉड्यूल जिसका अर्थ 128 Mi मेमोरी डेप्थ और प्रति चिप 16-बिट-वाइड डेटा बस से है। यदि मॉड्यूल में बोर्ड के प्रत्येक ओर इनमें से 8 चिप हैं तो कुल 16 चिप × 16-बिट वाइड डेटा = 256 कुल बिट विड्थ का डेटा होगा। 64-बिट-वाइड मेमोरी डेटा इंटरफ़ेस के लिए यह 4 रैंक के बराबर होता है। जहां प्रत्येक रैंक को 2-बिट चिप चयन सिग्नल द्वारा चुना जा सकता है। इंटेल 945 चिपसेट जैसे मेमोरी कंट्रोलर उन कॉन्फ़िगरेशन को सूचीबद्ध करते हैं जिनका वे समर्थन करते हैं। उदाहरण के लिए ×8 और ×16 उपकरणों के लिए 256-एमआईबी, 512-एमआईबी और 1-गीब डीडीआर-2 टेक्नोलॉजी 512-एमआईबिट तक के सभी डीडीआर-2 उपकरणों के लिए चार रैंक डेनसिटी, 1-गीबिट डीडीआर-2 उपकरणों के लिए 8 रैंक और चार किंग्स्टन टेक्नोलॉजी KHX6400D2/1G मेमोरी मॉड्यूल के साथ एक i945 मेमोरी कंट्रोलर लें, जहां प्रत्येक मॉड्यूल की क्षमता 1 गिबिबाइट है।[2] किंग्स्टन प्रत्येक मॉड्यूल को 16 "64M×8-बिट" चिप से बना प्रदर्शित करता है। प्रत्येक चिप में 8-बिट वाइड डेटा बस होती है जो 16 × 8, 128 के बराबर है। इसलिए प्रत्येक मॉड्यूल में 64 बिट की दो रैंक होती हैं। नॉर्थब्रिज (कंप्यूटिंग) के दृष्टिकोण से चार 1 जीबी मॉड्यूल हैं जिन्हें हाई-लॉजिकल लेवल पर एमसीएच दो चैनल पर प्रदर्शित किया जाता है जिनमें से प्रत्येक में चार रैंक होती हैं। इसके विपरीत बैंक, रैंक के लॉजिकल दृष्टिकोण से समान होते हुए भी भौतिक हार्डवेयर में अपेक्षाकृत अलग प्रकार से कार्यान्वित किए जाते हैं। बैंक एक एकल मेमोरी चिप के अंदर कई यूनिट होती हैं जबकि रैंक एक मॉड्यूल पर चिप के भाग से बनी यूनिट है। चिप चयन के समान बैंकों का चयन बैंक चयन बिट द्वारा किया जाता है, जो मेमोरी इंटरफ़ेस का एक भाग है।[citation needed]

संगठन का वर्गीकरण

मेमोरी चिप

मेमोरी ज्योमेट्री द्वारा चयन किए गए संगठन को निम्नतम रूप से कभी-कभी "मेमोरी डिवाइस" भी कहा जाता है। ये आईसी कॉम्पोनेन्ट हैं जो रैम के प्रत्येक मॉड्यूल को बनाते हैं। किसी चिप का सबसे महत्वपूर्ण माप उसका डेनसिटी है, जिसे बिट्स में मापा जाता है। क्योंकि मेमोरी बस की विड्थ सामान्यतः चिप की संख्या से बड़ी होती है प्रायः चिप को विड्थ के लिए डिज़ाइन किया जाता है, जिसका अर्थ है कि वे आंतरिक रूप से समान भागों में विभाजित होते हैं और जब एक एड्रेस "डेप्थ" को कॉल किया जाता है, तो केवल एक मान वापस करने के अतिरिक्त वह एक से अधिक मान वापस करता है। डेप्थ के अतिरिक्त चिप बैंकों पर एक दूसरा एड्रेस डायमेंशनल जोड़ा गया है जिसमे बैंक एक बैंक को उपलब्ध होने की स्वीकृति देती है जबकि दूसरा बैंक उपस्थित नही होता है क्योंकि यह रिफ्रेश होता है।[citation needed]

मेमोरी मॉड्यूल

मेमोरी मॉड्यूल की कुछ माप आकार, विड्थ, गति और लेटेंसी होती है। मेमोरी मॉड्यूल में वांछित मॉड्यूल विड्थ के बराबर कई मेमोरी चिप होते हैं। ये 32-बिट एसआईएमएम मॉड्यूल 8-बिट वाइड (×8) चिप से बना हो सकता है। जैसा कि मेमोरी चैनल भाग में बताया गया है कि भौतिक मॉड्यूल एक या अधिक लॉजिकल रैंक से बना हो सकता है। यदि वह 32-बिट एसआईएमएम 8-बिट चिप से बना होता है तो एसआईएमएम की दो रैंक होती हैं।[citation needed]

मेमोरी चैनल

एक मेमोरी चैनल कई रैंकों से बना होता है। भौतिक रूप से केवल मेमोरी मॉड्यूल वाला मेमोरी चैनल स्वयं को एक या अधिक लॉजिकल रैंक के रूप में प्रस्तुत कर सकता है।[citation needed]

संगठन कंट्रोलर

सामान्य कंप्यूटर में केवल एक मेमोरी कंट्रोलर होता है जिसमें केवल एक या दो चैनल होते हैं। लॉजिकल विशेषता अनुभाग में एनयूएमए कॉन्फ़िगरेशन का वर्णन किया गया है जो मेमोरी कंट्रोलरों के नेटवर्क का रूप ले सकता है। उदाहरण के लिए दो-सॉकेट एएमडी K-8 के प्रत्येक सॉकेट में दो-चैनल मेमोरी कंट्रोलर हो सकता है, जिससे सिस्टम को कुल चार मेमोरी चैनल प्राप्त होते हैं।

मेमोरी ज्योमेट्री नोटेशन

मेमोरी ज्योमेट्री को निर्दिष्ट करने के विभिन्न प्रकारों का सामना किया जा सकता है, जो विभिन्न प्रकार की जानकारी देते हैं।

मॉड्यूल

(memory depth) × (memory width)

मेमोरी विड्थ बिट्स में मेमोरी मॉड्यूल इंटरफ़ेस की डेटा विड्थ निर्दिष्ट करती है। उदाहरण के लिए यह 64-बिट डेटा विड्थ को इंगित करेगा, जैसा कि रैम के एसडीआर और डीडीआर 1-4 समूह में सामान्य नॉन-ईसीसी डीआईएमएम पर पाया जाता है। 72 बिट की विड्थ वाली मेमोरी एक ईसीसी मॉड्यूल को इंगित करता है जिसमें त्रुटि-सुधार कोड सिंड्रोम के लिए डेटा विड्थ में 8 अतिरिक्त बिट्स होते हैं जो ईसीसी सिंड्रोम एकल-बिट त्रुटियों को ठीक करने की स्वीकृति देते है। मेमोरी डेप्थ मेमोरी विड्थ से विभाजित बिट्स में कुल मेमोरी क्षमता है। कभी-कभी मेमोरी की डेप्थ मेग (220) की यूनिट में इंगित की जाती है, जैसे 32×64 या 64×64 जो क्रमशः 32 एमआई डेप्थ और 64 एमआई डेप्थ का संकेत देती है।

चिप

मेमोरी डेनसिटी - यह चिप की कुल मेमोरी क्षमता है।

128 Mib (memory depth) × (memory width)

मेमोरी डेप्थ और मेमोरी डेनसिटी को मेमोरी विड्थ से विभाजित किया जाता है। उदाहरण के लिए 128 एमआईबी और 8-बिट डेटा वाली मेमोरी चिप के लिए इसे 1(6 मेगा × 8) के रूप में निर्दिष्ट किया जा सकता है। कभी-कभी "एमआई" को 16 × 8 के रूप में निर्दिष्ट किया जाता है।

(memory depth per bank) × (memory width) × (number of banks)

उदाहरण: उपरोक्त के समान क्षमता और मेमोरी विड्थ वाली 4 बैंकों के साथ निर्मित एक चिप को 4 Mi × 8 × 4 के रूप में निर्दिष्ट किया जा सकता है।

यह भी देखें

- डीआईएमएम

- डिवाइस बैंडविड्थ की सूची

- डायनामिक रैंडम एक्सेस मेमोरी

- रैंडम एक्सेस मेमोरी

- मेमोरी संस्था

- मेमोरी एड्रेस

- मेमोरी बैंक

- बैंक स्विचिंग

- डबल साइडेड रैम

- ड्यूल चैनल आर्किटेक्चर

- पेज एड्रेस रजिस्टर

संदर्भ

- ↑ Ultimate Memory Guide (PDF), Kingston, 2007, archived from the original (PDF) on 2011-07-13.

- ↑ "KHX6400D2/1G" (PDF). Kingston Technology.

बाहरी

- "RAM", Mainboard (FAQ), IXT labs, 2006.

- FAQ, RAMpedia, archived from the original on 2010-05-16.

- "Part 1", RAM guide, Ars technica.

- "Banks", RAM, PC guide.

- KHX6400D2 1G (PDF) (data sheet), Value RAM, archived from the original (PDF) on 2012-03-10, retrieved 2010-08-05.

- 307502 (PDF) (data sheet), Intel.