सिस्टम-इन-पैकेज: Difference between revisions

m (Sugatha moved page एक पैकेज में सिस्टम to सिस्टम-इन-पैकेज) |

(→संदर्भ) |

||

| (6 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

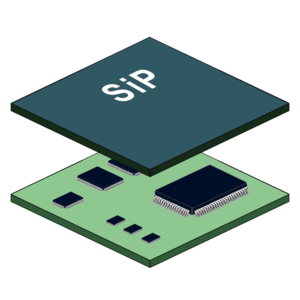

[[File:System in package.png|thumb|एक एसआईपी मल्टी-चिप का सीएडी ड्राइंग जिसमें एक ही सब्सट्रेट पर प्रोसेसर, मेमोरी औरसंचयन होता है।]]पैकेज में एक प्रणाली (एसआईपी) या प्रणाली-इन-पैकेज एक या एक से अधिक [[चिप वाहक]] पैकेजों में संलग्न कई एकीकृत परिपथ हैं जिन्हें [[पैकेज पर पैकेज]] का उपयोग करके संलग्न किया जा सकता है।<ref>{{Cite web|url=http://www.nepes.co.kr/web/nepes_eng/semi_SiP|title=System in Package (SiP) Solutions – nepes|website=www.nepes.co.kr}}</ref> एसआईपी एक [[इलेक्ट्रॉनिक प्रणाली]] के सभी या अधिकांश कार्य करता है, और सामान्यतः [[ चल दूरभाष |चल दूरभाष]] , [[पोर्टेबल मीडिया प्लेयर]] आदि के अंदर उपयोग किया जाता है।<ref> By Pushkar Apte, W. R. Bottoms, William Chen and George Scalise, IEEE Spectrum. “[https://spectrum.ieee.org/semiconductors/design/advanced-chip-packaging-satisfies-smartphone-needs Advanced Chip Packaging Satisfies Smartphone Needs].” February 8, 2011. Retrieved July 31, 2015.</ref> डाई (एकीकृत परिपथ) जिसमें एकीकृत परिपथ होते हैं, [[वेफर (इलेक्ट्रॉनिक्स)]] पर लंबवत रूप से रखे जा सकते हैं। वे आंतरिक रूप से ठीक [[तार]] से जुड़े होते हैं जो पैकेज से बंधे होते हैं। वैकल्पिक रूप से, [[ पलटें काटना |फ्लिप चिप]] विधि के साथ, सोल्डर बम्प्स का उपयोग स्टैक्ड चिप्स को साथ जोड़ने के लिए किया जाता है। एसआईपी एक चिप (एसओसी) पर एक प्रणाली की तरह है, किन्तु कम स्थायित्व से एकीकृत है और डाई (एकीकृत परिपथ) पर नहीं है।<ref>[https://anysilicon.com/system-in-package-sip-a-success-story/ System-in-Package (SiP), a success story] // AnySilicon, February 21, 2020</ref> | |||

कम सघन [[मल्टी-चिप मॉड्यूल]] के विपरीत, जो वाहक पर क्षैतिज रूप से मर जाता है, के विपरीत, एसआईपीडाई को खड़ी या क्षैतिज रूप से टाइल किया जा सकता है, चिपलेट्स या [[रजाई पैकेजिंग]] जैसी विधियोों के साथ। एसआईपीडाई को मानक ऑफ-चिप [[ तार का जोड़ |तार का जोड़]] या सोल्डर बम्प्स से जोड़ता है, थोड़ा सघन [[त्रि-आयामी एकीकृत सर्किट|त्रि-आयामी एकीकृत परिपथ]] के विपरीत जो डाई के माध्यम से चलने वाले संवाहक के साथ स्टैक्ड सिलिकॉन डाई को जोड़ता है। | |||

[[File:System in package.png|thumb|एक एसआईपी मल्टी-चिप का सीएडी ड्राइंग जिसमें एक ही सब्सट्रेट पर | |||

कम सघन [[मल्टी-चिप मॉड्यूल]] के विपरीत, जो | |||

कई अलग-अलग 3डी पैकेजिंग | कई अलग-अलग 3डी पैकेजिंग विधियोों को कॉम्पैक्ट क्षेत्र में कई मानक चिप मरने के ढेर के लिए विकसित किया गया है।<ref>By R. Wayne Johnson, Mark Strickland and David Gerke, NASA Electronic Parts and Packaging Program. “[http://nepp.nasa.gov/docuploads/EA7E7EA1-BD30-4DA4-BD615FEA1A7F5AE9/3D%20Packaging%20Report%20071805.pdf 3-D Packaging: A Technology Review].” June 23, 2005. Retrieved July 31, 2015.</ref> | ||

एक उदाहरण एसआईपीमें कई चिप्स हो सकते हैं - जैसे कि विशेष [[सेंट्रल प्रोसेसिंग यूनिट]], [[DRAM|डीरैम]], [[फ्लैश मेमोरी]] - [[निष्क्रिय घटक]] के साथ संयुक्त - प्रतिरोध और [[ संधारित्र |संधारित्र]] - सभी ही [[ सब्सट्रेट (इलेक्ट्रॉनिक्स) |सब्सट्रेट (इलेक्ट्रॉनिक्स)]] पर लगे होते हैं। इसका मतलब है कि मल्टी-चिप पैकेज में पूर्ण कार्यात्मक इकाई का निर्माण किया जा सकता है,जिससे इसे काम करने के लिए कुछ बाहरी घटकों को जोड़ने की आवश्यकता हो। यह [[ एमपी 3 प्लेयर |एमपी 3 प्लेयर]] और मोबाइल फोन जैसे सीमित स्थान वाले वातावरण में विशेष रूप से मूल्यवान है क्योंकि यह [[मुद्रित सर्किट बोर्ड|मुद्रित परिपथ बोर्ड]] और समग्र डिजाइन की जटिलता को कम करता है। इसके लाभों के बावजूद, यह विधि निर्माण की उपज को कम करती है क्योंकि पैकेज में किसी भी दोषपूर्ण चिप के परिणामस्वरूप गैर-कार्यात्मक पैकेज्ड एकीकृत परिपथ होगा, भले ही उसी पैकेज में अन्य सभी मॉड्यूल कार्यात्मक हों। | |||

एसआईपीएस एक चिप (एसओसी) एकीकृत परिपथ आर्किटेक्चर पर सामान्य प्रणाली के विपरीत हैं जो फ़ंक्शन के आधार पर घटकों को डाई (एकीकृत परिपथ) में एकीकृत करता है। एसओसी सामान्यतः सीपीयू, ग्राफिक्स और मेमोरी इंटरफेस, हार्ड-डिस्क और यूएसबी कनेक्टिविटी, [[ रैंडम एक्सेस मेमोरी |रैंडम एक्सेस मेमोरी]] | रैंडम-एक्सेस और [[ केवल पढ़ने के लिये मेमोरी |केवल पढ़ने के लिये मेमोरी]] | रीड-ओनली [[स्मृति]] और सेकेंडरीसंचयन और / या उनके कंट्रोलर को सिंगल पर एकीकृत करेगा। और डाई पर जाते हैं, जबकि एसआईपीइन मॉड्यूल को एक या एक से अधिक चिप वाहक पैकेजों में [[असतत घटक]] के रूप में जोड़ेगा। एसआईपीसामान्य पारंपरिक [[मदरबोर्ड]]-आधारित [[निजी कंप्यूटर]] [[कंप्यूटर आर्किटेक्चर]] जैसा दिखता है, जो फ़ंक्शन के आधार पर घटकों को अलग करता है और उन्हें केंद्रीय इंटरफेसिंग परिपथ बोर्ड के माध्यम से जोड़ता है। एसओसी की तुलना में एक एसआईपीमें एकीकरण का निम्न स्तर होता है। हाइब्रिड एकीकृत परिपथ कुछ हद तक एसआईपीएस के समान हैं, चूंकि वे पुरानी या कम उन्नत विधि का उपयोग करते हैं (सिंगल लेयर परिपथ बोर्ड या सबस्ट्रेट्स का उपयोग करते हैं, डाई स्टैकिंग का उपयोग नहीं करते हैं, डाइस/डिवाइस या स्मॉल आउटलाइन एकीकृत परिपथ पैकेज को जोड़ने के लिए वायर बॉन्डिंग का उपयोग करते हैं। फ्लिप चिप या बीजीए की, दोहरी इन-लाइन पैकेज का उपयोग करें, या बीजीए, आदि के बजाय हाइब्रिड आईसी के बाहर इंटरफेसिंग के लिए सिंगल इन-लाइन पैकेज) | |||

एसआईपी विधि मुख्य रूप से [[पहनने योग्य कंप्यूटर]], मोबाइल उपकरणों और [[चीजों की इंटरनेट]] में प्रारंभिक बाजार के रुझानों से संचालित होती है, जो स्थापित उपभोक्ता और व्यवसाय एसओसी बाजार में उच्च संख्या में उत्पादित इकाइयों की मांग नहीं करते हैं। जैसे-जैसे इंटरनेट ऑफ थिंग्स एक वास्तविकता अधिक और दृष्टि कम होती जाती है, चिप और एसआईपीस्तर पर प्रणाली में नवाचार हो रहा हैजिससे [[माइक्रोइलेक्ट्रॉनिक सिस्टम|माइक्रोइलेक्ट्रॉनिक प्रणाली]] (एमईएमएस) सेंसर को एक अलग डाई पर एकीकृत किया जा सके और कनेक्टिविटी को नियंत्रित किया जा सके।<ref>By Ed Sperling, Semiconductor Engineering. “[http://semiengineering.com/why-packaging-matters/ Why Packaging Matters].” November 19, 2015. Retrieved March 16, 2016.</ref> एसआईपीसमाधानों के लिए कई पैकेजिंग विधियोों की आवश्यकता हो सकती है, जैसे फ्लिप चिप, वायर बॉन्डिंग, [[वेफर-स्तरीय पैकेजिंग]] आदि।<ref>By Tech Search International and Chip Scale Review Staff, Chip Scale Review. “[http://fbs.advantageinc.com/chipscale/may-jun_2016/files/assets/basic-html/page-1.html Major OSATs positioned for growth opportunities in SiP].” May/June Issue. Retrieved June 22, 2016.</ref> | |||

| Line 19: | Line 19: | ||

* एएमपीके टेक्नोलॉजी इंक। | * एएमपीके टेक्नोलॉजी इंक। | ||

* नैनियम, एस.ए. | * नैनियम, एस.ए. | ||

* [[एएसई | * [[एएसई ग्रुप]] | ||

* सेरामाइक्रो | * सेरामाइक्रो | ||

* चिपसिप टेक्नोलॉजी | * चिपसिप टेक्नोलॉजी | ||

* [[सरू सेमीकंडक्टर]] | * [[सरू सेमीकंडक्टर]] | ||

* | * स्टैट्स चिपपैक लिमिटेड | ||

* [[तोशीबा]] | * [[तोशीबा]] | ||

* [[रेनेसास]] | * [[रेनेसास]] | ||

* [[ | * [[सैनडिस्क]] | ||

* [[ | * [[ सैमसंग ]] | ||

* [[सिलिकॉन लैब्स]] | * [[सिलिकॉन लैब्स]] | ||

* ऑक्टावो सिस्टम्स | * ऑक्टावो सिस्टम्स | ||

* [[नॉर्डिक | * [[नॉर्डिक अर्धचालक]] | ||

* जेसीईटी | * जेसीईटी | ||

{{div col end}} | {{div col end}} | ||

== यह भी देखें == | == यह भी देखें == | ||

* चिप पर | * चिप पर प्रणाली (एसओसी) | ||

* [[हाइब्रिड इंटीग्रेटेड सर्किट]] ( | * [[हाइब्रिड इंटीग्रेटेड सर्किट|हाइब्रिड एकीकृत परिपथ]] (एचआईसी) | ||

== संदर्भ == | == संदर्भ == | ||

{{reflist}} | {{reflist}} | ||

[[Category: | [[Category:Collapse templates]] | ||

[[Category:Created On 16/03/2023]] | [[Category:Created On 16/03/2023]] | ||

[[Category:Lua-based templates]] | |||

[[Category:Machine Translated Page]] | |||

[[Category:Multi-column templates]] | |||

[[Category:Navigational boxes| ]] | |||

[[Category:Navigational boxes without horizontal lists]] | |||

[[Category:Pages using div col with small parameter]] | |||

[[Category:Pages with script errors]] | |||

[[Category:Sidebars with styles needing conversion]] | |||

[[Category:Template documentation pages|Documentation/doc]] | |||

[[Category:Templates Vigyan Ready]] | |||

[[Category:Templates generating microformats]] | |||

[[Category:Templates that add a tracking category]] | |||

[[Category:Templates that are not mobile friendly]] | |||

[[Category:Templates using TemplateData]] | |||

[[Category:Templates using under-protected Lua modules]] | |||

[[Category:Wikipedia fully protected templates|Div col]] | |||

[[Category:Wikipedia metatemplates]] | |||

[[Category:इलेक्ट्रॉनिक डिजाइन]] | |||

[[Category:एकीकृत सर्किट]] | |||

[[Category:पैकेजिंग (माइक्रोफैब्रिकेशन)]] | |||

[[Category:माइक्रोटेक्नोलोजी]] | |||

[[Category:संगणक प्रणाली]] | |||

Latest revision as of 15:42, 13 September 2023

पैकेज में एक प्रणाली (एसआईपी) या प्रणाली-इन-पैकेज एक या एक से अधिक चिप वाहक पैकेजों में संलग्न कई एकीकृत परिपथ हैं जिन्हें पैकेज पर पैकेज का उपयोग करके संलग्न किया जा सकता है।[1] एसआईपी एक इलेक्ट्रॉनिक प्रणाली के सभी या अधिकांश कार्य करता है, और सामान्यतः चल दूरभाष , पोर्टेबल मीडिया प्लेयर आदि के अंदर उपयोग किया जाता है।[2] डाई (एकीकृत परिपथ) जिसमें एकीकृत परिपथ होते हैं, वेफर (इलेक्ट्रॉनिक्स) पर लंबवत रूप से रखे जा सकते हैं। वे आंतरिक रूप से ठीक तार से जुड़े होते हैं जो पैकेज से बंधे होते हैं। वैकल्पिक रूप से, फ्लिप चिप विधि के साथ, सोल्डर बम्प्स का उपयोग स्टैक्ड चिप्स को साथ जोड़ने के लिए किया जाता है। एसआईपी एक चिप (एसओसी) पर एक प्रणाली की तरह है, किन्तु कम स्थायित्व से एकीकृत है और डाई (एकीकृत परिपथ) पर नहीं है।[3]

कम सघन मल्टी-चिप मॉड्यूल के विपरीत, जो वाहक पर क्षैतिज रूप से मर जाता है, के विपरीत, एसआईपीडाई को खड़ी या क्षैतिज रूप से टाइल किया जा सकता है, चिपलेट्स या रजाई पैकेजिंग जैसी विधियोों के साथ। एसआईपीडाई को मानक ऑफ-चिप तार का जोड़ या सोल्डर बम्प्स से जोड़ता है, थोड़ा सघन त्रि-आयामी एकीकृत परिपथ के विपरीत जो डाई के माध्यम से चलने वाले संवाहक के साथ स्टैक्ड सिलिकॉन डाई को जोड़ता है।

कई अलग-अलग 3डी पैकेजिंग विधियोों को कॉम्पैक्ट क्षेत्र में कई मानक चिप मरने के ढेर के लिए विकसित किया गया है।[4]

एक उदाहरण एसआईपीमें कई चिप्स हो सकते हैं - जैसे कि विशेष सेंट्रल प्रोसेसिंग यूनिट, डीरैम, फ्लैश मेमोरी - निष्क्रिय घटक के साथ संयुक्त - प्रतिरोध और संधारित्र - सभी ही सब्सट्रेट (इलेक्ट्रॉनिक्स) पर लगे होते हैं। इसका मतलब है कि मल्टी-चिप पैकेज में पूर्ण कार्यात्मक इकाई का निर्माण किया जा सकता है,जिससे इसे काम करने के लिए कुछ बाहरी घटकों को जोड़ने की आवश्यकता हो। यह एमपी 3 प्लेयर और मोबाइल फोन जैसे सीमित स्थान वाले वातावरण में विशेष रूप से मूल्यवान है क्योंकि यह मुद्रित परिपथ बोर्ड और समग्र डिजाइन की जटिलता को कम करता है। इसके लाभों के बावजूद, यह विधि निर्माण की उपज को कम करती है क्योंकि पैकेज में किसी भी दोषपूर्ण चिप के परिणामस्वरूप गैर-कार्यात्मक पैकेज्ड एकीकृत परिपथ होगा, भले ही उसी पैकेज में अन्य सभी मॉड्यूल कार्यात्मक हों।

एसआईपीएस एक चिप (एसओसी) एकीकृत परिपथ आर्किटेक्चर पर सामान्य प्रणाली के विपरीत हैं जो फ़ंक्शन के आधार पर घटकों को डाई (एकीकृत परिपथ) में एकीकृत करता है। एसओसी सामान्यतः सीपीयू, ग्राफिक्स और मेमोरी इंटरफेस, हार्ड-डिस्क और यूएसबी कनेक्टिविटी, रैंडम एक्सेस मेमोरी | रैंडम-एक्सेस और केवल पढ़ने के लिये मेमोरी | रीड-ओनली स्मृति और सेकेंडरीसंचयन और / या उनके कंट्रोलर को सिंगल पर एकीकृत करेगा। और डाई पर जाते हैं, जबकि एसआईपीइन मॉड्यूल को एक या एक से अधिक चिप वाहक पैकेजों में असतत घटक के रूप में जोड़ेगा। एसआईपीसामान्य पारंपरिक मदरबोर्ड-आधारित निजी कंप्यूटर कंप्यूटर आर्किटेक्चर जैसा दिखता है, जो फ़ंक्शन के आधार पर घटकों को अलग करता है और उन्हें केंद्रीय इंटरफेसिंग परिपथ बोर्ड के माध्यम से जोड़ता है। एसओसी की तुलना में एक एसआईपीमें एकीकरण का निम्न स्तर होता है। हाइब्रिड एकीकृत परिपथ कुछ हद तक एसआईपीएस के समान हैं, चूंकि वे पुरानी या कम उन्नत विधि का उपयोग करते हैं (सिंगल लेयर परिपथ बोर्ड या सबस्ट्रेट्स का उपयोग करते हैं, डाई स्टैकिंग का उपयोग नहीं करते हैं, डाइस/डिवाइस या स्मॉल आउटलाइन एकीकृत परिपथ पैकेज को जोड़ने के लिए वायर बॉन्डिंग का उपयोग करते हैं। फ्लिप चिप या बीजीए की, दोहरी इन-लाइन पैकेज का उपयोग करें, या बीजीए, आदि के बजाय हाइब्रिड आईसी के बाहर इंटरफेसिंग के लिए सिंगल इन-लाइन पैकेज)

एसआईपी विधि मुख्य रूप से पहनने योग्य कंप्यूटर, मोबाइल उपकरणों और चीजों की इंटरनेट में प्रारंभिक बाजार के रुझानों से संचालित होती है, जो स्थापित उपभोक्ता और व्यवसाय एसओसी बाजार में उच्च संख्या में उत्पादित इकाइयों की मांग नहीं करते हैं। जैसे-जैसे इंटरनेट ऑफ थिंग्स एक वास्तविकता अधिक और दृष्टि कम होती जाती है, चिप और एसआईपीस्तर पर प्रणाली में नवाचार हो रहा हैजिससे माइक्रोइलेक्ट्रॉनिक प्रणाली (एमईएमएस) सेंसर को एक अलग डाई पर एकीकृत किया जा सके और कनेक्टिविटी को नियंत्रित किया जा सके।[5] एसआईपीसमाधानों के लिए कई पैकेजिंग विधियोों की आवश्यकता हो सकती है, जैसे फ्लिप चिप, वायर बॉन्डिंग, वेफर-स्तरीय पैकेजिंग आदि।[6]

आपूर्तिकर्ता

- उन्नत लघु उपकरण

- अमकोर प्रौद्योगिकी

- एटमेल

- एएमपीके टेक्नोलॉजी इंक।

- नैनियम, एस.ए.

- एएसई ग्रुप

- सेरामाइक्रो

- चिपसिप टेक्नोलॉजी

- सरू सेमीकंडक्टर

- स्टैट्स चिपपैक लिमिटेड

- तोशीबा

- रेनेसास

- सैनडिस्क

- सैमसंग

- सिलिकॉन लैब्स

- ऑक्टावो सिस्टम्स

- नॉर्डिक अर्धचालक

- जेसीईटी

यह भी देखें

- चिप पर प्रणाली (एसओसी)

- हाइब्रिड एकीकृत परिपथ (एचआईसी)

संदर्भ

- ↑ "System in Package (SiP) Solutions – nepes". www.nepes.co.kr.

- ↑ By Pushkar Apte, W. R. Bottoms, William Chen and George Scalise, IEEE Spectrum. “Advanced Chip Packaging Satisfies Smartphone Needs.” February 8, 2011. Retrieved July 31, 2015.

- ↑ System-in-Package (SiP), a success story // AnySilicon, February 21, 2020

- ↑ By R. Wayne Johnson, Mark Strickland and David Gerke, NASA Electronic Parts and Packaging Program. “3-D Packaging: A Technology Review.” June 23, 2005. Retrieved July 31, 2015.

- ↑ By Ed Sperling, Semiconductor Engineering. “Why Packaging Matters.” November 19, 2015. Retrieved March 16, 2016.

- ↑ By Tech Search International and Chip Scale Review Staff, Chip Scale Review. “Major OSATs positioned for growth opportunities in SiP.” May/June Issue. Retrieved June 22, 2016.