अनुक्रमिक स्थिरता: Difference between revisions

(Created page with "{{Short description|Consistency model in concurrent computing}} अनुक्रमिक संगति एक संगति मॉडल है जिसका उप...") |

No edit summary |

||

| (5 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

{{Short description|Consistency model in concurrent computing}} | {{Short description|Consistency model in concurrent computing}} | ||

अनुक्रमिक | '''अनुक्रमिक सुसंगित''' एक सुसंगित मॉडल है जिसका उपयोग [[समवर्ती कंप्यूटिंग]] के क्षेत्र में किया जाता है (उदाहरण के लिए वितरित साझा मेमोरी, [[वितरित लेनदेन]], आदि में)। | ||

यह | यह वह गुण है" ... किसी भी निष्पादन का नतीजा समान होता है जैसे कि सभी प्रोसेसर के संचालन को किसी अनुक्रमिक क्रम में निष्पादित किया जाता है, और प्रत्येक व्यक्तिगत प्रोसेसर के संचालन इस क्रम में उसके प्रोग्राम द्वारा निर्दिष्ट क्रम में दिखाई देते हैं।<ref>[[Leslie Lamport]], "How to Make a Multiprocessor Computer That Correctly Executes Multiprocess Programs", IEEE Trans. Comput. C-28,9 (Sept. 1979), 690-691.</ref> | ||

अर्थात्, एक ही प्रोसेसर (या थ्रेड) में प्रोग्राम का निष्पादन क्रम प्रोग्राम ऑर्डर के समान होता है, जबकि विभिन्न प्रोसेसर (या थ्रेड्स) पर प्रोग्राम का निष्पादन क्रम अपरिभाषित होता है। इस तरह उदाहरण में: | |||

संकल्पनात्मक रूप से, एकल वैश्विक मेमोरी और | [[File:Sequential consistency.svg|600px]]A1, B1 और C1 के बीच निष्पादन क्रम संरक्षित है, अर्थात A1, B1 से पहले रन करता है, और B1, C1 से पहले रन करता है। A2 और B2 के लिए समान है। लेकिन, जैसा कि प्रोसेसर के बीच निष्पादन क्रम अपरिभाषित है, B2 C1 से पहले या बाद में रन कर सकता है (B2 प्राकृतिक रूप से C1 से पहले रन कर सकता है, लेकिन B2 का प्रभाव C1 के बाद देखा जा सकता है, जो "C1 के बाद B2 रन" के समान है) | ||

संकल्पनात्मक रूप से, एकल वैश्विक मेमोरी और "स्विच" है जो किसी भी काल चरण पर यादृच्छिक ढंग से प्रोसेसर को मेमोरी से जोड़ता है। प्रत्येक प्रोसेसर '''प्रोग्राम ऑर्डर''' में मेमोरी ऑपरेशंस (स्मृति संचालन) जारी करता है और स्विच सभी मेमोरी ऑपरेशंस के बीच वैश्विक क्रमांकन प्रदान करता है<ref>[[Sarita V. Adve]], [[Kourosh Gharachorloo]], "Shared Memory Consistency Models: A Tutorial"</ref> | |||

<gallery> | <gallery> | ||

Rsz_selection_055.png| | Rsz_selection_055.png| | ||

</gallery> | </gallery> | ||

अनुक्रमिक | अनुक्रमिक सुसंगित सख्त सुसंगित की तुलना में दुर्बल है, जिसके लिए उस स्थान पर अंतिम लेखन के मान को वापस करने के लिए किसी स्थान से पढ़ने की आवश्यकता होती है; सख्त सुसंगित की मांग है कि संचालन को उस क्रम में देखा जाए जिसमें वे वास्तव में जारी किए गए थे। | ||

== यह भी देखें == | == यह भी देखें == | ||

| Line 22: | Line 23: | ||

==संदर्भ== | ==संदर्भ== | ||

{{Reflist}} | {{Reflist}} | ||

[[Category:Created On 26/05/2023]] | [[Category:Created On 26/05/2023]] | ||

[[Category:Lua-based templates]] | |||

[[Category:Machine Translated Page]] | |||

[[Category:Pages with script errors]] | |||

[[Category:Templates Vigyan Ready]] | |||

[[Category:Templates that add a tracking category]] | |||

[[Category:Templates that generate short descriptions]] | |||

[[Category:Templates using TemplateData]] | |||

[[Category:संगति मॉडल]] | |||

Latest revision as of 16:56, 12 June 2023

अनुक्रमिक सुसंगित एक सुसंगित मॉडल है जिसका उपयोग समवर्ती कंप्यूटिंग के क्षेत्र में किया जाता है (उदाहरण के लिए वितरित साझा मेमोरी, वितरित लेनदेन, आदि में)।

यह वह गुण है" ... किसी भी निष्पादन का नतीजा समान होता है जैसे कि सभी प्रोसेसर के संचालन को किसी अनुक्रमिक क्रम में निष्पादित किया जाता है, और प्रत्येक व्यक्तिगत प्रोसेसर के संचालन इस क्रम में उसके प्रोग्राम द्वारा निर्दिष्ट क्रम में दिखाई देते हैं।[1]

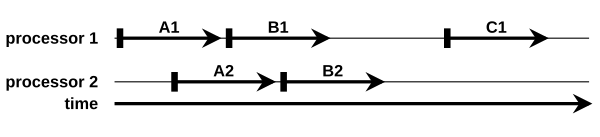

अर्थात्, एक ही प्रोसेसर (या थ्रेड) में प्रोग्राम का निष्पादन क्रम प्रोग्राम ऑर्डर के समान होता है, जबकि विभिन्न प्रोसेसर (या थ्रेड्स) पर प्रोग्राम का निष्पादन क्रम अपरिभाषित होता है। इस तरह उदाहरण में:

A1, B1 और C1 के बीच निष्पादन क्रम संरक्षित है, अर्थात A1, B1 से पहले रन करता है, और B1, C1 से पहले रन करता है। A2 और B2 के लिए समान है। लेकिन, जैसा कि प्रोसेसर के बीच निष्पादन क्रम अपरिभाषित है, B2 C1 से पहले या बाद में रन कर सकता है (B2 प्राकृतिक रूप से C1 से पहले रन कर सकता है, लेकिन B2 का प्रभाव C1 के बाद देखा जा सकता है, जो "C1 के बाद B2 रन" के समान है)

A1, B1 और C1 के बीच निष्पादन क्रम संरक्षित है, अर्थात A1, B1 से पहले रन करता है, और B1, C1 से पहले रन करता है। A2 और B2 के लिए समान है। लेकिन, जैसा कि प्रोसेसर के बीच निष्पादन क्रम अपरिभाषित है, B2 C1 से पहले या बाद में रन कर सकता है (B2 प्राकृतिक रूप से C1 से पहले रन कर सकता है, लेकिन B2 का प्रभाव C1 के बाद देखा जा सकता है, जो "C1 के बाद B2 रन" के समान है)

संकल्पनात्मक रूप से, एकल वैश्विक मेमोरी और "स्विच" है जो किसी भी काल चरण पर यादृच्छिक ढंग से प्रोसेसर को मेमोरी से जोड़ता है। प्रत्येक प्रोसेसर प्रोग्राम ऑर्डर में मेमोरी ऑपरेशंस (स्मृति संचालन) जारी करता है और स्विच सभी मेमोरी ऑपरेशंस के बीच वैश्विक क्रमांकन प्रदान करता है[2]

अनुक्रमिक सुसंगित सख्त सुसंगित की तुलना में दुर्बल है, जिसके लिए उस स्थान पर अंतिम लेखन के मान को वापस करने के लिए किसी स्थान से पढ़ने की आवश्यकता होती है; सख्त सुसंगित की मांग है कि संचालन को उस क्रम में देखा जाए जिसमें वे वास्तव में जारी किए गए थे।

यह भी देखें

संदर्भ

- ↑ Leslie Lamport, "How to Make a Multiprocessor Computer That Correctly Executes Multiprocess Programs", IEEE Trans. Comput. C-28,9 (Sept. 1979), 690-691.

- ↑ Sarita V. Adve, Kourosh Gharachorloo, "Shared Memory Consistency Models: A Tutorial"