क्वाड्रुपल प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट: Difference between revisions

No edit summary |

m (Abhishekkshukla moved page चौगुनी-परिशुद्धता फ़्लोटिंग-पॉइंट प्रारूप to क्वाड्रुपल प्रिसिजन फ़्लोटिंग-पॉइंट फॉर्मेट without leaving a redirect) |

||

| (9 intermediate revisions by 4 users not shown) | |||

| Line 2: | Line 2: | ||

{{Floating-point}} | {{Floating-point}} | ||

{{Computer architecture bit widths}} | {{Computer architecture bit widths}} | ||

कंप्यूटिंग में, क्वाड्रुपल प्रिसिजन (या क्वाड परिशुद्धता) एक बाइनरी फ्लोटिंग पॉइंट-आधारित कंप्यूटर नंबर फॉर्मेट है जो 53-बिट डबल प्रिसिजन से कम से कम दोगुनी प्रिसिजन के साथ 16 बाइट्स (128 बिट्स) पर अधिकृत कर लेता है। | |||

== आईईईई 754 | यह 128-बिट क्वाड्रुपल प्रिसिजन न केवल उन अनुप्रयोगों के लिए डिज़ाइन की गई है, जिनके परिणामों की दोगुनी से अधिक प्रिसिजन की आवश्यकता होती है,<ref>{{cite web|url=https://www.davidhbailey.com/dhbpapers/dhb-jmb-acat08.pdf|title=उच्च परिशुद्धता संगणना और गणितीय भौतिकी|author1=David H. Bailey |author2=Jonathan M. Borwein |date=July 6, 2009}}</ref> किंतु एक प्राथमिक कार्य के रूप में, मध्यवर्ती गणनाओं और स्क्रैच वेरिएबल्स में अतिप्रवाह और राउंड-ऑफ त्रुटियों को कम करके दोहरे प्रिसिजन परिणामों की गणना को अधिक विश्वसनीय और स्पष्ट रूप से अनुमति देना है। मूल आईईईई-754 फ़्लोटिंग पॉइंट मानक के प्राथमिक वास्तुकार [[विलियम कहाँ|विलियम]] ने कहा, अभी के लिए विस्तारित परिशुद्धता या x86 आर्किटेक्चर विस्तारित प्रिसिजन फॉर्मेट या 10-बाइट विस्तारित फॉर्मेट अतिरिक्त-स्पष्ट अंकगणित के मूल्य और इसे तेजी से चलाने के लिए प्रयुक्त करने की मूल्य के बीच एक सहनीय समझौता है; बहुत जल्द प्रिसिजन के दो और बाइट्स सहनीय हो जाएंगे, और अंततः 16-बाइट फॉर्मेट ... व्यापक प्रिसिजन की ओर उस तरह का क्रमिक विकास पहले से ही देखने में था जब [[IEEE 754|आईईईई 754]] या फ़्लोटिंग-पॉइंट अंकगणित के लिए आईईईई मानक 754 तैयार किया गया था।<ref>{{cite book|first=Nicholas | last=Higham |title="Designing stable algorithms" in Accuracy and Stability of Numerical Algorithms (2 ed)| publisher=SIAM|year=2002 | pages=43 }}</ref> | ||

[[IEEE 754-2008|आईईईई 754-2008]] में 128-बिट बेस-2 फॉर्मेट को आधिकारिक रूप से बाइनरी128 कहा जाता है। | |||

== आईईईई 754 क्वाड्रुपल -प्रिसिजन बाइनरी फ़्लोटिंग-पॉइंट फॉर्मेट: बाइनरी128 == | |||

आईईईई 754 मानक एक बाइनरी128 को इस प्रकार निर्दिष्ट करता है: | |||

* [[साइन बिट]]: 1 बिट | * [[साइन बिट]]: 1 बिट | ||

* घातांक चौड़ाई: 15 बिट्स | * घातांक चौड़ाई: 15 बिट्स | ||

* [[महत्व]]पूर्ण [[परिशुद्धता (अंकगणित)]]: 113 बिट्स (112 स्पष्ट रूप से संग्रहीत) | * [[महत्व]]पूर्ण [[परिशुद्धता (अंकगणित)|प्रिसिजन (अंकगणित)]]: 113 बिट्स (112 स्पष्ट रूप से संग्रहीत) | ||

यह 33 से 36 महत्वपूर्ण दशमलव अंकों तक स्पष्टता देता है। यदि अधिकतम 33 महत्वपूर्ण अंकों वाली एक दशमलव स्ट्रिंग को सामान्य संख्या देते हुए आईईईई 754 चतुर्गुण-स्पष्ट फॉर्मेट में परिवर्तित किया जाता है, और फिर समान अंकों की संख्या के साथ दशमलव स्ट्रिंग में परिवर्तित किया जाता है, तो अंतिम परिणाम मूल स्ट्रिंग से मेल खाना चाहिए। यदि आईईईई 754 क्वाड्रुपल -स्पष्ट संख्या को कम से कम 36 महत्वपूर्ण अंकों के साथ दशमलव स्ट्रिंग में परिवर्तित किया जाता है और फिर वापस क्वाड्रुपल -स्पष्ट प्रतिनिधित्व में परिवर्तित किया जाता है, तो अंतिम परिणाम मूल संख्या से मेल खाना चाहिए।<ref name="whyieee">{{cite web|url=http://www.cs.berkeley.edu/~wkahan/ieee754status/IEEE754.PDF|title=Lecture Notes on the Status of IEEE Standard 754 for Binary Floating-Point Arithmetic| author=William Kahan |date=1 October 1987}}</ref> | |||

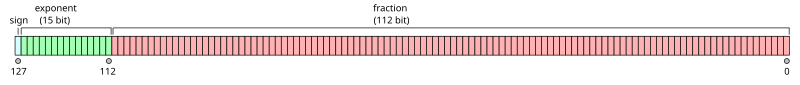

जब तक घातांक को सभी शून्यों के साथ संग्रहीत नहीं किया जाता है तब तक प्रारूप को मान 1 के साथ एक अंतर्निहित लीड बिट के साथ लिखा जाता है। इस प्रकार मेमोरी फॉर्मेट में महत्व के केवल 112 बिट्स दिखाई देते हैं, किंतु कुल परिशुद्धता 113 बिट्स (लगभग 34 दशमलव अंक: {{nowrap|log<sub>10</sub>(2<sup>113</sup>) ≈ 34.016}} है। बिट्स को इस प्रकार रखा गया है: | |||

जब तक घातांक को सभी शून्यों के साथ संग्रहीत नहीं किया जाता है तब तक प्रारूप को मान 1 के साथ एक अंतर्निहित लीड बिट के साथ लिखा जाता है। इस प्रकार मेमोरी फॉर्मेट में महत्व के केवल 112 बिट्स दिखाई देते हैं, | |||

[[File:IEEE 754 Quadruple Floating Point Format.svg|800px|एक संकेत बिट, एक 15-बिट प्रतिपादक, और एक 112-बिट महत्व]] | [[File:IEEE 754 Quadruple Floating Point Format.svg|800px|एक संकेत बिट, एक 15-बिट प्रतिपादक, और एक 112-बिट महत्व]] | ||

=== घातांक एन्कोडिंग === | === घातांक एन्कोडिंग === | ||

क्वाड्रुपल -स्पष्ट बाइनरी फ़्लोटिंग-पॉइंट एक्सपोनेंट को [[ऑफसेट बाइनरी]] प्रतिनिधित्व का उपयोग करके एन्कोड किया गया है, जिसमें शून्य ऑफसेट 16383 है; इसे आईईईई 754 मानक में प्रतिपादक पूर्वाग्रह के रूप में भी जाना जाता है। | |||

* | ** E<sub>min</sub> = 0001<sub>16</sub> − 3FFF<sub>16</sub> = −16382 | ||

* | ** E<sub>max</sub> = 7FFE<sub>16</sub> − 3FFF<sub>16</sub> = 16383 | ||

* घातांक पूर्वाग्रह = | ** घातांक पूर्वाग्रह = 3FFF<sub>16</sub> = 16383 | ||

इस प्रकार, जैसा कि ऑफसेट बाइनरी प्रतिनिधित्व द्वारा परिभाषित किया गया है, वास्तविक घातांक प्राप्त करने के लिए, 16383 के ऑफसेट को संग्रहीत घातांक से घटाना होगा। | इस प्रकार, जैसा कि ऑफसेट बाइनरी प्रतिनिधित्व द्वारा परिभाषित किया गया है, वास्तविक घातांक प्राप्त करने के लिए, 16383 के ऑफसेट को संग्रहीत घातांक से घटाना होगा। | ||

संग्रहीत घातांक 0000<sub>16</sub> और 7FFF<sub>16</sub> की विशेष रूप से व्याख्या की गई है। | |||

{|class="wikitable" style="text-align:center" | {|class="wikitable" style="text-align:center" | ||

! | !प्रतिपादक | ||

!सार्थकता शून्य | |||

!सार्थकतथा गैर-शून्य | |||

!समीकरण | |||

|- | |- | ||

| 0000<sub>16</sub> || [[0 (number)|0]], [[−0]] || | | 0000<sub>16</sub> || [[0 (number)|0]], [[−0]] ||असामान्य संख्याएँ | ||

| (−1)<sup>signbit</sup> × 2<sup>−16382</sup> × 0.महत्वपूर्णबिट्स<sub>2</sub> | |||

|- | |- | ||

| 0001<sub>16</sub>, ..., 7FFE<sub>16</sub> ||colspan=2| | | 0001<sub>16</sub>, ..., 7FFE<sub>16</sub> ||colspan=2|सामान्यीकृत मूल्य | ||

| (−1)<sup>signbit</sup> × 2<sup>exponentbits<sub>2</sub> − 16383</sup> × 1.महत्वपूर्णबिट्स<sub>2</sub> | |||

|- | |- | ||

| 7FFF<sub>16</sub> || ±[[infinity|∞]] || | | 7FFF<sub>16</sub> || ±[[infinity|∞]] ||NaN (शांत, सिग्नलिंग) | ||

|} | |} | ||

न्यूनतम सख्ती से धनात्मक (असामान्य) मान 2<sup>−16494</sup> ≈ 10<sup>−4965</sup> है और इसकी स्पष्टता केवल एक बिट है। न्यूनतम धनात्मक सामान्य मान 2<sup>−16382</sup> ≈ 3.3621 × 10<sup>−4932</sup> है और इसकी स्पष्टता 113 बिट्स अर्थात ±2<sup>−16494</sup> भी है। अधिकतम प्रतिनिधित्व योग्य मान 2<sup>16384</sup> − 2<sup>16271</sup> ≈ 1.1897 × 10<sup>4932</sup>. है। | |||

डिफ़ॉल्ट रूप से, महत्व में बिट्स की विषम संख्या के कारण, 1/3 राउंड दोहरी परिशुद्धता की तरह नीचे आते हैं। | === क्वाड्रुपल प्रिसिजन उदाहरण === | ||

तो | ये उदाहरण [[हेक्साडेसिमल]] में बिट प्रतिनिधित्व में दिए गए हैं, फ़्लोटिंग-पॉइंट मान का। इसमें संकेत, (पक्षपातपूर्ण) प्रतिपादक और महत्व सम्मिलित हैं।<syntaxhighlight lang="abl"> | ||

0000 0000 0000 0000 0000 0000 0000 000116 = 2−16382 × 2−112 = 2−16494 | |||

≈ 6.4751751194380251109244389582276465525 × 10−4966 | |||

(smallest positive subnormal number) | |||

</syntaxhighlight><syntaxhighlight lang="abl"> | |||

0000 ffff ffff ffff ffff ffff ffff ffff16 = 2−16382 × (1 − 2−112) | |||

≈ 3.3621031431120935062626778173217519551 × 10−4932 | |||

(largest subnormal number) | |||

</syntaxhighlight><syntaxhighlight lang="abl"> | |||

0001 0000 0000 0000 0000 0000 0000 000016 = 2−16382 | |||

≈ 3.3621031431120935062626778173217526026 × 10−4932 | |||

(smallest positive normal number) | |||

</syntaxhighlight><syntaxhighlight lang="abl"> | |||

7ffe ffff ffff ffff ffff ffff ffff ffff16 = 216383 × (2 − 2−112) | |||

≈ 1.1897314953572317650857593266280070162 × 104932 | |||

(largest normal number) | |||

</syntaxhighlight><syntaxhighlight lang="abl"> | |||

3ffe ffff ffff ffff ffff ffff ffff ffff16 = 1 − 2−113 | |||

≈ 0.9999999999999999999999999999999999037 | |||

(largest number less than one) | |||

</syntaxhighlight><syntaxhighlight> | |||

3fff 0000 0000 0000 0000 0000 0000 000016 = 1 (one) | |||

</syntaxhighlight><syntaxhighlight lang="abl"> | |||

3fff 0000 0000 0000 0000 0000 0000 000116 = 1 + 2−112 | |||

≈ 1.0000000000000000000000000000000001926 | |||

(smallest number larger than one) | |||

</syntaxhighlight><syntaxhighlight> | |||

c000 0000 0000 0000 0000 0000 0000 000016 = −2 | |||

</syntaxhighlight><syntaxhighlight> | |||

0000 0000 0000 0000 0000 0000 0000 000016 = 0 | |||

8000 0000 0000 0000 0000 0000 0000 000016 = −0 | |||

</syntaxhighlight><syntaxhighlight> | |||

7fff 0000 0000 0000 0000 0000 0000 000016 = infinity | |||

ffff 0000 0000 0000 0000 0000 0000 000016 = −infinity | |||

</syntaxhighlight><syntaxhighlight> | |||

4000 921f b544 42d1 8469 898c c517 01b816 ≈ π | |||

</syntaxhighlight><syntaxhighlight> | |||

3ffd 5555 5555 5555 5555 5555 5555 555516 ≈ 1/3 | |||

</syntaxhighlight>डिफ़ॉल्ट रूप से, महत्व में बिट्स की विषम संख्या के कारण, 1/3 राउंड दोहरी परिशुद्धता की तरह नीचे आते हैं। तो गोलाकार बिंदु से परे बिट्स <code>0101...</code> हैं जो कि अंतिम स्थान पर एक इकाई के 1/2 से कम है। | |||

== डबल-डबल अंकगणित == | == डबल-डबल अंकगणित == | ||

दोहरे- | दोहरे-प्रिसिजन मानों के जोड़े का उपयोग करके लगभग क्वाड्रुपल प्रिसिजन को प्रयुक्त करने की एक सामान्य सॉफ़्टवेयर तकनीक को कभी-कभी 'डबल-डबल अंकगणित' कहा जाता है।<ref name=Hida>Yozo Hida, X. Li, and D. H. Bailey, [http://citeseerx.ist.psu.edu/viewdoc/summary?doi=10.1.1.4.5769 Quad-Double Arithmetic: Algorithms, Implementation, and Application], Lawrence Berkeley National Laboratory Technical Report LBNL-46996 (2000). Also Y. Hida et al., [http://web.mit.edu/tabbott/Public/quaddouble-debian/qd-2.3.4-old/docs/qd.pdf Library for double-double and quad-double arithmetic] (2007).</ref><ref name=Shewchuk>J. R. Shewchuk, [https://www.cs.cmu.edu/~quake/robust.html Adaptive Precision Floating-Point Arithmetic and Fast Robust Geometric Predicates], [[Discrete & Computational Geometry]] 18:305–363, 1997.</ref><ref name="Knuth-4.2.3-pr9">{{cite book |last=Knuth |first=D. E. |title=कंप्यूटर प्रोग्रामिंग की कला|edition=2nd |at=chapter 4.2.3. problem 9. }}</ref> 53-बिट महत्व के साथ आईईईई डबल-स्पष्ट मानों के जोड़े का उपयोग करते हुए, डबल-डबल अंकगणित कम से कम महत्व वाले संख्याओं पर संचालन प्रदान करता है <ref name=Hida/> {{nowrap|1=2 × 53 = 106 bits}} (वास्तव में 107 बिट्स <ref>Robert Munafo [http://mrob.com/pub/math/f161.html F107 and F161 High-Precision Floating-Point Data Types] (2011).</ref> कुछ सबसे बड़े मानों को छोड़कर, सीमित घातांक सीमा के कारण), आईईईई बाइनरी128 क्वाड्रुपल प्रिसिजन के 113-बिट महत्व से केवल थोड़ा कम स्पष्ट डबल-डबल की सीमा अनिवार्य रूप से डबल-स्पष्ट फॉर्मेट के समान ही रहती है क्योंकि घातांक में अभी भी 11 बिट हैं,<ref name=Hida /> आईईईई क्वाड्रुपल प्रिसिजन (की एक सीमा) के 15-बिट प्रतिपादक से अधिक कम है (डबल- के लिए {{nowrap|1.8 × 10<sup>308</sup>}} की रेंज) बाइनरी128 के लिए डबल बनाम {{nowrap|1.2 × 10<sup>4932</sup>}})। | ||

विशेष रूप से, डबल-डबल तकनीक में एक डबल-डबल/ | विशेष रूप से, डबल-डबल तकनीक में एक डबल-डबल/क्वाड्रुपल-स्पष्ट मान q को दो दोहरे-स्पष्ट मान x और y के योग q = x + y के रूप में दर्शाया जाता है, जिनमें से प्रत्येक q के महत्व का आधा भाग प्रदान करता है।<ref name=Shewchuk/> अर्थात्, जोड़ी (x, y) को q के स्थान पर संग्रहीत किया जाता है, और q मान (+, -, ×, ...) पर संचालन x और y मानों पर समतुल्य (किंतु अधिक सम्मिश्र ) संचालन में बदल दिया जाता है। इस प्रकार, इस तकनीक में अंकगणित दोहरे-परिशुद्धता संचालन के अनुक्रम में कम हो जाता है; चूंकि डबल-प्रिसिजन अंकगणित समान्यत: हार्डवेयर में प्रयुक्त किया जाता है, डबल-डबल अंकगणित समान्यत: अधिक सामान्य इच्छित -स्पष्ट अंकगणित तकनीकों की तुलना में अधिक तेज होता है।<ref name=Hida/><ref name=Shewchuk/> | ||

ध्यान दें कि डबल-डबल अंकगणित में निम्नलिखित विशेष विशेषताएं हैं:<ref>[http://pic.dhe.ibm.com/infocenter/aix/v7r1/index.jsp?topic=%2Fcom.ibm.aix.genprogc%2Fdoc%2Fgenprogc%2F128bit_long_double_floating-point_datatype.htm 128-Bit Long Double Floating-Point Data Type]</ref> | ध्यान दें कि डबल-डबल अंकगणित में निम्नलिखित विशेष विशेषताएं हैं:<ref>[http://pic.dhe.ibm.com/infocenter/aix/v7r1/index.jsp?topic=%2Fcom.ibm.aix.genprogc%2Fdoc%2Fgenprogc%2F128bit_long_double_floating-point_datatype.htm 128-Bit Long Double Floating-Point Data Type]</ref> | ||

* जैसे-जैसे मूल्य का परिमाण घटता है, अतिरिक्त परिशुद्धता की मात्रा भी घटती जाती है। इसलिए, सामान्यीकृत सीमा में सबसे छोटी संख्या दोगुनी परिशुद्धता से संकीर्ण है। पूर्ण | *जैसे-जैसे मूल्य का परिमाण घटता है, अतिरिक्त परिशुद्धता की मात्रा भी घटती जाती है। इसलिए, सामान्यीकृत सीमा में सबसे छोटी संख्या दोगुनी परिशुद्धता से संकीर्ण है। पूर्ण स्पष्टता के साथ सबसे छोटी संख्या {{nowrap|1000...0<sub>2</sub> (106 zeros) × 2<sup>−1074</sup>}} या {{nowrap|1.000...0<sub>2</sub> (106 zeros) × 2<sup>−968</sup>}} है। वे संख्याएँ जिनका परिमाण 2−1021 से छोटा है, उनमें दोहरी परिशुद्धता की तुलना में अतिरिक्त परिशुद्धता नहीं होगी। | ||

* | * प्रिसिजन के बिट्स की वास्तविक संख्या भिन्न हो सकती है। सामान्य रूप से संख्या के निम्न-क्रम वाले भाग का परिमाण उच्च-क्रम वाले भाग के आधे यूएलपी से अधिक नहीं होता है। यदि निम्न-क्रम वाला भाग उच्च-क्रम वाले भाग के आधे यूएलपी से कम है, तो उच्च-क्रम और निम्न-क्रम संख्याओं के महत्वपूर्ण के बीच महत्वपूर्ण बिट्स (या तो सभी 0 या सभी 1) निहित हैं। कुछ एल्गोरिदम जो महत्व में बिट्स की एक निश्चित संख्या पर भरोसा करते हैं, 128-बिट लंबी दोहरी संख्याओं का उपयोग करते समय विफल हो सकते हैं। | ||

* उपरोक्त कारण | *उपरोक्त कारण के कारण, {{nowrap|1 + 2<sup>−1074</sup>}} जैसे मानों का प्रतिनिधित्व करना संभव है, जो 1 से बड़ी सबसे छोटी प्रतिनिधित्व योग्य संख्या है। | ||

डबल-डबल अंकगणित के अतिरिक्त, यदि किसी उच्च प्रिसिजन फ़्लोटिंग-पॉइंट लाइब्रेरी के बिना उच्च प्रिसिजन की आवश्यकता होती है, तो ट्रिपल-डबल या क्वाड-डबल अंकगणित उत्पन्न करना भी संभव है। उन्हें क्रमशः तीन (या चार) दोहरे-स्पष्ट मानों के योग के रूप में दर्शाया जाता है। वे क्रमशः कम से कम 159/161 और 212/215 बिट्स के साथ संचालन का प्रतिनिधित्व कर सकते हैं। | |||

एक समान तकनीक का उपयोग डबल-क्वाड अंकगणित का उत्पादन करने के लिए किया जा सकता है, जिसे दो क्वाड्रुपल -स्पष्ट मानों के योग के रूप में दर्शाया जाता है। वे कम से कम 226 (या 227) बिट्स के साथ संचालन का प्रतिनिधित्व कर सकते हैं।<ref>sourceware.org [http://sourceware.org/ml/libc-alpha/2012-03/msg01024.html Re: The state of glibc libm]</ref> | |||

==कार्यान्वयन== | ==कार्यान्वयन== | ||

क्वाड्रुपल प्रिसिजन को अधिकांशतः सॉफ्टवेयर में विभिन्न तकनीकों द्वारा प्रयुक्त किया जाता है (जैसे कि उपरोक्त डबल-डबल तकनीक, चूँकि वह तकनीक आईईईई क्वाड्रुपल प्रिसिजन को प्रयुक्त नहीं करती है), क्योंकि 2016 तक क्वाड्रुपल प्रिसिजन के लिए प्रत्यक्ष हार्डवेयर समर्थन कम समान्य है (नीचे या हार्डवेयर समर्थन देखें)। क्वाड्रुपल (या उच्चतर) प्रिसिजन प्राप्त करने के लिए कोई सामान्य इच्छित -स्पष्ट अंकगणितीय लाइब्रेरी का उपयोग कर सकता है, किंतु विशेष क्वाड्रुपल -प्रिसिजन कार्यान्वयन उच्च प्रदर्शन प्राप्त कर सकता है। | |||

===कंप्यूटर- | ===कंप्यूटर-लैंग्वेज समर्थन=== | ||

एक अलग प्रश्न यह है कि किस हद तक | एक अलग प्रश्न यह है कि किस हद तक क्वाड्रुपल -स्पष्ट प्रकारों को सीधे कंप्यूटर [[प्रोग्रामिंग भाषा|प्रोग्रामिंग लैंग्वेज]] ओं में सम्मिलित किया जाता है। | ||

फोरट्रान में क्वाड्रुपल परिशुद्धता <code>real(real128)</code> द्वारा निर्दिष्ट की जाती है (फोरट्रान 2008 से मॉड्यूल <code>iso_fortran_env</code> का उपयोग किया जाना चाहिए, अधिकांश प्रोसेसर पर निरंतर <code>real128</code> 16 के बराबर है), या <code>real(selected_real_kind(33, 4931))</code>के रूप में, या एक गैर में -वास्तविक जैसा मानक <code>REAL*16</code> (उदाहरण के लिए, क्वाड्रुपल-प्रिसिजन <code>REAL*16</code>इंटेल फोरट्रान कंपाइलर <ref>{{cite web|title= GCC 4.6 Release Series - Changes, New Features, and Fixes |url=https://gcc.gnu.org/gcc-4.6/changes.html|access-date=2010-02-06}}</ref> और x86, x86-64 और इटेनियम आर्किटेक्चर पर जीएनयू फोरट्रान कंपाइलर <ref>{{cite web|title=इंटेल फोरट्रान कंपाइलर उत्पाद संक्षिप्त (web.archive.org पर संग्रहीत प्रति)|url=http://h21007.www2.hp.com/portal/download/files/unprot/intel/product_brief_Fortran_Linux.pdf |publisher=Su |access-date=2010-01-23 |url-status=unfit |archive-url=https://web.archive.org/web/20081025174427/http://h21007.www2.hp.com/portal/download/files/unprot/intel/product_brief_Fortran_Linux.pdf |archive-date=October 25, 2008 }}</ref> द्वारा समर्थित है।) | |||

सी प्रोग्रामिंग लैंग्वेज के लिए, आईएसओ/आईईसी टीएस 18661-3 (सी, इंटरचेंज और विस्तारित प्रकारों के लिए फ़्लोटिंग-पॉइंट एक्सटेंशन) <code>_Float128</code> को आईईईई 754 चतुर्भुज-स्पष्ट प्रारूप (बाइनरी128) को प्रयुक्त करने वाले प्रकार के रूप में निर्दिष्ट करता है।<ref>{{cite web|title=ISO/IEC TS 18661-3|url=https://www.open-std.org/jtc1/sc22/wg14/www/docs/n1945.pdf|date=2015-06-10|access-date=2019-09-22}}</ref> वैकल्पिक रूप से, कुछ प्रणालियों और कंपाइलरों के साथ [[C++|C]]/[[C++]] में, क्वाड्रुपल परिशुद्धता को <code>लंबे डबल</code> प्रकार द्वारा निर्दिष्ट किया जा सकता है, किंतु यह लैंग्वेज के लिए आवश्यक नहीं है (जिसे कम से कम <code>double</code> जितना स्पष्ट होने के लिए केवल <code>long double</code> की आवश्यकता होती है), न ही ऐसा है यह समान्य है. | |||

x86 और x86-64 पर, सबसे | x86 और x86-64 पर, सबसे समान्य C/C++ कंपाइलर 80-बिट विस्तारित परिशुद्धता के रूप में <code>long double</code> प्रयुक्त करते हैं (उदाहरण के लिए जीएनयू C कंपाइलर जीसीसी<ref>[https://web.archive.org/web/20080713131713/https://gcc.gnu.org/onlinedocs/gcc/i386-and-x86_002d64-Options.html i386 and x86-64 Options (archived copy on web.archive.org)], ''Using the GNU Compiler Collection''.</ref> और इंटेल C++ कंपाइलर<code>/Qlong‑double</code> स्विच <ref>[http://software.intel.com/en-us/articles/size-of-long-integer-type-on-different-architecture-and-os/ Intel Developer Site]</ref> के साथ) या बस क्वाड्रुपल परिशुद्धता के अतिरिक्त दोहरी परिशुद्धता (उदाहरण के लिए माइक्रोसॉफ्ट विजुअल C++<ref>[http://msdn.microsoft.com/en-us/library/9cx8xs15.aspx MSDN homepage, about Visual C++ compiler]</ref>) का पर्याय बन गया है। एआरएम 64-बिट आर्किटेक्चर (एआर्क64) के लिए प्रक्रिया कॉल मानक निर्दिष्ट करता है कि <code>long double</code> आईईईई 754 क्वाड्रुपल-प्रिसिजन प्रारूप से मेल खाता है। <ref>{{cite web|title=Procedure Call Standard for the ARM 64-bit Architecture (AArch64)|url=http://infocenter.arm.com/help/topic/com.arm.doc.ihi0055b/IHI0055B_aapcs64.pdf|date=2013-05-22|access-date=2019-09-22|archive-url=https://web.archive.org/web/20191016000704/http://infocenter.arm.com/help/topic/com.arm.doc.ihi0055b/IHI0055B_aapcs64.pdf|archive-date=2019-10-16|url-status=dead}}</ref> कुछ अन्य आर्किटेक्चर पर, कुछ C/C++ कंपाइलर लंबे समय तक डबल को क्वाड्रुपल परिशुद्धता के रूप में प्रयुक्त करते हैं, उदाहरण के लिए। पावरपीसी पर जीसीसी (डबल-डबल<ref>[https://gcc.gnu.org/onlinedocs/gcc/RS_002f6000-and-PowerPC-Options.html RS/6000 and PowerPC Options], ''Using the GNU Compiler Collection''.</ref><ref>[https://developer.apple.com/legacy/mac/library/documentation/Performance/Conceptual/Mac_OSX_Numerics/Mac_OSX_Numerics.pdf Inside Macintosh - PowerPC Numerics] {{webarchive |url=https://web.archive.org/web/20121009191824/http://developer.apple.com/legacy/mac/library/documentation/Performance/Conceptual/Mac_OSX_Numerics/Mac_OSX_Numerics.pdf |date=October 9, 2012 }}</ref><ref>[https://opensource.apple.com/source/gcc/gcc-5646/gcc/config/rs6000/darwin-ldouble.c 128-bit long double support routines for Darwin]</ref> के रूप में) और स्पार्क,<ref>[https://gcc.gnu.org/onlinedocs/gcc/SPARC-Options.html SPARC Options], ''Using the GNU Compiler Collection''.</ref> या स्पार्क पर सन स्टूडियो कंपाइलर<ref>[http://docs.oracle.com/cd/E19422-01/819-3693/ncg_lib.html The Math Libraries], Sun Studio 11 ''Numerical Computation Guide'' (2005).</ref> तथापि <code>long double</code> क्वाड्रुपल परिशुद्धता नहीं है, तथापि, कुछ C/C++ कंपाइलर एक विस्तार के रूप में एक गैरमानक क्वाड्रुपल-स्पष्ट प्रकार प्रदान करते हैं। उदाहरण के लिए, जीसीसी x86, x86-64 और इटेनियम सीपीयू के लिए __float128 नामक एक क्वाड्रुपल-परिशुद्धता प्रकार प्रदान करता है, <ref>[https://gcc.gnu.org/onlinedocs/gcc/Floating-Types.html Additional Floating Types], ''Using the GNU Compiler Collection''</ref> और पावरपीसी पर -mfloat128-हार्डवेयर या -mfloat128 विकल्पों का उपयोग करके आईईईई 128-बिट फ़्लोटिंग-पॉइंट के रूप में प्रदान करता है;<ref name="gcc6changes">{{cite web|title=GCC 6 Release Series - Changes, New Features, and Fixes|url=https://gcc.gnu.org/gcc-6/changes.html|access-date=2016-09-13}}</ref> और x86 और x86-64 के लिए Intel के C/C++ कंपाइलर के कुछ संस्करण _Quad नामक एक गैर-मानक चतुर्भुज-स्पष्ट प्रकार की आपूर्ति करते हैं। <ref>[http://software.intel.com/en-us/forums/showthread.php?t=56359 Intel C++ Forums] (2007).</ref> | ||

गूगल की कार्य-प्रगति वाली लैंग्वेज [[कार्बन (प्रोग्रामिंग भाषा)|कार्बन (प्रोग्रामिंग लैंग्वेज )]] 'f128' नामक प्रकार के साथ इसके लिए समर्थन प्रदान करती है।<ref>{{cite web |url=https://github.com/carbon-language/carbon-lang/blob/trunk/docs/design/README.md#floating-point-types |title=कार्बन भाषा का मुख्य भंडार - भाषा डिज़ाइन|date=2022-08-09 |website=GitHub |access-date=2022-09-22}}</ref> | |||

===लैब्ररी और टूलबॉक्स === | |||

*[[जीएनयू कंपाइलर संग्रह]] क्वाड-प्रिसिजन गणित लाइब्रेरी, [https://gcc.gnu.org/onlinedocs/libquadmath लिबक्वाडमैथ], <code>__float128</code> और <code>__complex128</code> संचालन प्रदान करता है। | |||

*बूस्ट मल्टीप्रिसिज़न लाइब्रेरी बूस्ट.मल्टीप्रिसिजन <code>__float128</code> और _Quad प्रकारों के लिए एकीकृत क्रॉस-प्लेटफ़ॉर्म C++ इंटरफ़ेस प्रदान करता है, और इसमें मानक गणित लाइब्रेरी का एक कस्टम कार्यान्वयन सम्मिलित है।<ref>{{cite web|url=http://www.boost.org/doc/libs/1_58_0/libs/multiprecision/doc/html/boost_multiprecision/tut/floats/float128.html|title=Boost.Multiprecision - float128|access-date=2015-06-22}}</ref> | |||

* [[MATLAB|मैटलैब]] के लिए मल्टीप्रिसिजन कंप्यूटिंग टूलबॉक्स मैटलैब में क्वाड्रुपल -प्रिसिजन गणना की अनुमति देता है। इसमें मूलभूत अंकगणितीय कार्यक्षमता के साथ-साथ संख्यात्मक विधियाँ, सघन और विरल रैखिक बीजगणित भी सम्मिलित हैं।<ref>{{cite web|url=http://www.advanpix.com/2013/01/20/fast-quadruple-precision-computations/|title=MATLAB में तेज़ चौगुनी परिशुद्धता संगणनाएँ|author=Pavel Holoborodko|date=2013-01-20|access-date=2015-06-22}}</ref> | |||

* डबलफ्लोट्स<ref>{{cite web|title=DoubleFloats.jl|website=[[GitHub]] |url=https://github.com/JuliaMath/DoubleFloats.jl}}</ref> पैकेज जूलिया प्रोग्रामिंग लैंग्वेज के लिए डबल-डबल संगणना के लिए समर्थन प्रदान करता है। | |||

* Doubledouble.py <ref>{{cite web|title=डॉबलेडोउब्ले.पी|website=[[GitHub]] |url=https://github.com/sukop/doubledouble}}</ref> लाइब्रेरी पायथन में डबल-डबल गणनाओं को सक्षम बनाती है। | |||

* मैथमेटिका आईईईई क्वाड-प्रिसिजन संख्याओं का समर्थन करता है: 128-बिट फ़्लोटिंग-पॉइंट मान (रियल128), और 256-बिट सम्मिश्र मान (कॉम्प्लेक्स256)। | |||

* | |||

=== हार्डवेयर समर्थन === | |||

आईईईई चतुर्भुज प्रिसिजन को 1998 में आईबीएम सिस्टम/390 G5 में जोड़ा गया था,<ref>{{cite journal |last1=Schwarz |first1=E. M. |last2=Krygowski |first2=C. A. |date=September 1999 |title=The S/390 G5 floating-point unit |journal=IBM Journal of Research and Development |volume=43 |issue=5/6 |pages=707–721 |doi=10.1147/rd.435.0707 |citeseerx=10.1.1.117.6711 }}</ref> और बाद के z/आर्किटेक्चर प्रोसेसर में हार्डवेयर में समर्थित है।<ref>{{cite news|title=The IBM eServer z990 floating-point unit. IBM J. Res. Dev. 48; pp. 311-322|author=Gerwig, G. and Wetter, H. and Schwarz, E. M. and Haess, J. and Krygowski, C. A. and Fleischer, B. M. and Kroener, M.|date=May 2004}}</ref><ref>{{cite web|url=http://arith22.gforge.inria.fr/slides/s1-schwarz.pdf|author=Eric Schwarz|title=The IBM z13 SIMD Accelerators for Integer, String, and Floating-Point|date=June 22, 2015|access-date=July 13, 2015}}</ref> आईबीएम [[POWER9|पॉवर9]] सीपीयू (पावर आईएसए या पावर आईएसए v.3.0|पावर आईएसए 3.0) में मूल 128-बिट हार्डवेयर समर्थन है।<ref name=gcc6changes/> | |||

आईईईई 128-बिट फ़्लोट का मूल समर्थन [[PA-RISC|पीए-रिस्क]] 1.0 में परिभाषित किया गया है,<ref>{{cite web |url=http://grouper.ieee.org/groups//754/email/msg04128.html |title=बाइनरी इंटरचेंज प्रारूपों के लिए कार्यान्वयनकर्ता समर्थन|website=grouper.ieee.org |archive-url=https://web.archive.org/web/20171027202715/https://grouper.ieee.org/groups//754/email/msg04128.html |archive-date=2017-10-27 |access-date=2021-07-15}}</ref> और स्पार्क V8 में<ref>{{cite book | |||

|title = The SPARC Architecture Manual: Version 8 (archived copy on web.archive.org) | |title = The SPARC Architecture Manual: Version 8 (archived copy on web.archive.org) | ||

|year = 1992 | |year = 1992 | ||

| Line 138: | Line 139: | ||

|archive-url = https://web.archive.org/web/20050204100221/http://www.sparc.org/standards/V8.pdf | |archive-url = https://web.archive.org/web/20050204100221/http://www.sparc.org/standards/V8.pdf | ||

|archive-date = 2005-02-04 | |archive-date = 2005-02-04 | ||

}}</ref> और वी9<ref>{{cite book |title=The SPARC Architecture Manual: Version 9 (archived copy on web.archive.org) |year=1994 |editor1=David L. Weaver |editor2=Tom Germond |publisher=SPARC International, Inc |url=http://www.sparc.org/standards/SPARCV9.pdf |access-date=2011-09-24 |quote=Floating-point: The architecture provides an IEEE 754-compatible floating-point instruction set, operating on a separate register file that provides 32 single-precision (32-bit), 32 double-precision (64-bit), 16 quad-precision (128-bit) registers, or a mixture thereof. |url-status=dead |archive-url=https://web.archive.org/web/20120118213535/http://www.sparc.org/standards/SPARCV9.pdf |archive-date=2012-01-18 }}</ref> आर्किटेक्चर (उदाहरण के लिए 16 क्वाड-प्रिसिजन रजिस्टर %q0, %q4, ... हैं), | }}</ref> और वी9<ref>{{cite book |title=The SPARC Architecture Manual: Version 9 (archived copy on web.archive.org) |year=1994 |editor1=David L. Weaver |editor2=Tom Germond |publisher=SPARC International, Inc |url=http://www.sparc.org/standards/SPARCV9.pdf |access-date=2011-09-24 |quote=Floating-point: The architecture provides an IEEE 754-compatible floating-point instruction set, operating on a separate register file that provides 32 single-precision (32-bit), 32 double-precision (64-bit), 16 quad-precision (128-bit) registers, or a mixture thereof. |url-status=dead |archive-url=https://web.archive.org/web/20120118213535/http://www.sparc.org/standards/SPARCV9.pdf |archive-date=2012-01-18 }}</ref> आर्किटेक्चर (उदाहरण के लिए 16 क्वाड-प्रिसिजन रजिस्टर %q0, %q4, ... हैं), {{as of|2004|lc=on}} किंतु कोई भी स्पार्क सीपीयू हार्डवेयर में क्वाड-प्रिसिजन ऑपरेशन प्रयुक्त नहीं करता है .<ref>{{cite book | ||

| title = Numerical Computation Guide — Sun Studio 10 | | title = Numerical Computation Guide — Sun Studio 10 | ||

| chapter = SPARC Behavior and Implementation | | chapter = SPARC Behavior and Implementation | ||

| Line 147: | Line 148: | ||

| quote = There are four situations, however, when the hardware will not successfully complete a floating-point instruction: ... The instruction is not implemented by the hardware (such as ... quad-precision instructions on any SPARC FPU). | | quote = There are four situations, however, when the hardware will not successfully complete a floating-point instruction: ... The instruction is not implemented by the hardware (such as ... quad-precision instructions on any SPARC FPU). | ||

}}</ref> | }}</ref> | ||

आईबीएम हेक्साडेसिमल फ्लोटिंग-पॉइंट या एक्सटेंडेड-प्रिसिजन 128-बिट या नॉन-आईईईई एक्सटेंडेड-प्रिसिजन (128 बिट्स ऑफ स्टोरेज, 1 साइन बिट, 7 एक्सपोनेंट बिट्स, 112 फ्रैक्शन बिट्स, 8 बिट्स अप्रयुक्त) को आईबीएम सिस्टम/370 सीरीज (1970-1980 के दशक) में जोड़ा गया था और 196 में कुछ आईबीएम सिस्टम/360 या सिस्टम/360 मॉडल पर उपलब्ध था। 0एस (सिस्टम/360-85,<ref>{{cite journal | doi = 10.1147/sj.71.0022 | volume=7 | title=Structural aspects of the System/360 Model 85, III: Extensions to floating-point architecture | year=1968 | journal=IBM Systems Journal | pages=22–29 | author=Padegs A}}</ref> -195, और अन्य विशेष अनुरोध द्वारा या ओएस सॉफ़्टवेयर द्वारा सिम्युलेटेड)। | |||

[[ | [[सीमेंस]] 7.700 और 7.500 श्रृंखला मेनफ्रेम और उनके उत्तराधिकारी आईबीएम सिस्टम/360 और सिस्टम/370 के समान फ़्लोटिंग-पॉइंट फॉर्मेट और निर्देशों का समर्थन करते हैं। | ||

[[NEC SX-Aurora TSUBASA]] आर्किटेक्चर 128-बिट बाइनरी | [[VAX|वैक्स]] प्रोसेसर ने गैर-आईईईई क्वाड्रपल-प्रिसिजन फ़्लोटिंग पॉइंट को अपने H फ़्लोटिंग-पॉइंट फॉर्मेट के रूप में कार्यान्वित किया गया था। इसमें एक साइन बिट, एक 15-बिट एक्सपोनेंट और 112-फ़्रेक्शन बिट्स थे, चूँकि मेमोरी में लेआउट आईईईई क्वाड्रुपल प्रिसिजन से अधिक अलग था और एक्सपोनेंट पूर्वाग्रह भी भिन्न था। प्रारंभिक [[VAX|वैक्स]] प्रोसेसरों में से केवल कुछ ने हार्डवेयर में H फ़्लोटिंग-पॉइंट निर्देशों को प्रयुक्त किया था अन्य सभी ने सॉफ़्टवेयर में H फ़्लोटिंग-पॉइंट का अनुकरण किया था। | ||

[[ RISC-वी ]] | |||

क्वाड्रपल-प्रिसिजन (128-बिट) हार्डवेयर कार्यान्वयन को 128-बिट एफपीयू के साथ | [[NEC SX-Aurora TSUBASA|एनईसी एसएक्स-अरोड़ा त्सुबासा]] आर्किटेक्चर 128-बिट बाइनरी आईईईई754 क्वाड स्पष्ट संख्याओं को जोड़ने, घटाने, गुणा करने और तुलना करने का समर्थन करता है।<ref>[https://sxauroratsubasa.sakura.ne.jp/documents/sdk/pdfs/VectorEngine-as-manual-v1.4.pdf Vector Engine AssemblyLanguage Reference Manual], Chapter4 Assembler Syntax page 23.</ref> दो निकटतम 64-बिट रजिस्टर का उपयोग किया जाता है। क्वाडप्रिसिजन अंकगणित वेक्टर रजिस्टर में समर्थित नहीं है।<ref>[https://sxauroratsubasa.sakura.ne.jp/documents/guide/pdfs/Aurora_ISA_guide.pdf SX-Aurora TSUBASA Architecture Guide Revision 1.1] (p. 38, 60).</ref> | ||

[[ RISC-वी |आरआईएससी-वी]] आर्किटेक्चर 128-बिट बाइनरी आईईईई 754-2008 फ्लोटिंग पॉइंट अंकगणित के लिए Q (क्वाड-प्रिसिजन) एक्सटेंशन निर्दिष्ट करता है।<ref>[https://github.com/riscv/riscv-isa-manual/releases/download/Ratified-IMAFDQC/riscv-spec-20191213.pdf RISC-V ISA Specification v. 20191213], Chapter 13, “Q” Standard Extension for Quad-Precision Floating-Point, page 79.</ref> एल एक्सटेंशन (अभी तक प्रमाणित नहीं) 64-बिट और 128-बिट दशमलव फ़्लोटिंग पॉइंट निर्दिष्ट करेगा।<ref>[https://github.com/riscv/riscv-isa-manual/releases/download/Ratified-IMAFDQC/riscv-spec-20191213.pdf] Chapter 15 (p. 95).</ref> | |||

क्वाड्रपल-प्रिसिजन (128-बिट) हार्डवेयर कार्यान्वयन को 128-बिट एफपीयू के साथ अस्पष्ट नहीं किया जाना चाहिए जो एकल निर्देश, कई डेटा निर्देशों को प्रयुक्त करता है, जैसे कि [[स्ट्रीमिंग SIMD एक्सटेंशन|स्ट्रीमिंग एसआईएमडी एक्सटेंशन]] या [[AltiVec|अल्टीवेक]], जो चार 32-बिट सिंगल-प्रिसिजन या दो 64-बिट डबल-प्रिसिजन मानों के 128-बिट [[वेक्टर प्रोसेसर]] को संदर्भित करता है जो एक साथ संचालित होते हैं। | |||

== यह भी देखें == | == यह भी देखें == | ||

* आईईईई 754, फ्लोटिंग-पॉइंट अंकगणित के लिए आईईईई मानक | * आईईईई 754, फ्लोटिंग-पॉइंट अंकगणित के लिए आईईईई मानक | ||

* आईएसओ/आईईसी 10967, | * आईएसओ/आईईसी 10967, लैंग्वेज स्वतंत्र अंकगणित | ||

* [[आदिम डेटा प्रकार]] | * [[आदिम डेटा प्रकार|प्राचीन डेटा प्रकार]] | ||

* [[क्यू संकेतन (वैज्ञानिक संकेतन)]] | * [[क्यू संकेतन (वैज्ञानिक संकेतन)]] | ||

== संदर्भ == | == संदर्भ == | ||

{{Reflist|30em}} | {{Reflist|30em}} | ||

== बाहरी संबंध == | == बाहरी संबंध == | ||

* [https://www.davidhbailey.com/dhbsoftware/ High-Precision Software Directory] | * [https://www.davidhbailey.com/dhbsoftware/ High-Precision Software Directory] | ||

| Line 174: | Line 176: | ||

* [http://babbage.cs.qc.cuny.edu/IEEE-754 IEEE-754 Analysis], Interactive web page for examining Binary32, Binary64, and Binary128 floating-point values | * [http://babbage.cs.qc.cuny.edu/IEEE-754 IEEE-754 Analysis], Interactive web page for examining Binary32, Binary64, and Binary128 floating-point values | ||

[[Category:All articles containing potentially dated statements]] | |||

[[Category: | [[Category:Articles containing potentially dated statements from 2004]] | ||

[[Category:CS1 maint]] | |||

[[Category: | |||

[[Category:Created On 25/07/2023]] | [[Category:Created On 25/07/2023]] | ||

[[Category:Lua-based templates]] | |||

[[Category:Machine Translated Page]] | |||

[[Category:Pages with script errors]] | |||

[[Category:Pages with syntax highlighting errors]] | |||

[[Category:Short description with empty Wikidata description]] | |||

[[Category:Templates Vigyan Ready]] | |||

[[Category:Templates that add a tracking category]] | |||

[[Category:Templates that generate short descriptions]] | |||

[[Category:Templates using TemplateData]] | |||

[[Category:Webarchive template wayback links]] | |||

[[Category:फ़्लोटिंग पॉइंट प्रकार]] | |||

[[Category:बाइनरी अंकगणित]] | |||

Latest revision as of 12:44, 6 September 2023

| Floating-point formats |

|---|

| IEEE 754 |

|

| Other |

| Computer architecture bit widths |

|---|

| Bit |

| Application |

| Binary floating-point precision |

| Decimal floating-point precision |

कंप्यूटिंग में, क्वाड्रुपल प्रिसिजन (या क्वाड परिशुद्धता) एक बाइनरी फ्लोटिंग पॉइंट-आधारित कंप्यूटर नंबर फॉर्मेट है जो 53-बिट डबल प्रिसिजन से कम से कम दोगुनी प्रिसिजन के साथ 16 बाइट्स (128 बिट्स) पर अधिकृत कर लेता है।

यह 128-बिट क्वाड्रुपल प्रिसिजन न केवल उन अनुप्रयोगों के लिए डिज़ाइन की गई है, जिनके परिणामों की दोगुनी से अधिक प्रिसिजन की आवश्यकता होती है,[1] किंतु एक प्राथमिक कार्य के रूप में, मध्यवर्ती गणनाओं और स्क्रैच वेरिएबल्स में अतिप्रवाह और राउंड-ऑफ त्रुटियों को कम करके दोहरे प्रिसिजन परिणामों की गणना को अधिक विश्वसनीय और स्पष्ट रूप से अनुमति देना है। मूल आईईईई-754 फ़्लोटिंग पॉइंट मानक के प्राथमिक वास्तुकार विलियम ने कहा, अभी के लिए विस्तारित परिशुद्धता या x86 आर्किटेक्चर विस्तारित प्रिसिजन फॉर्मेट या 10-बाइट विस्तारित फॉर्मेट अतिरिक्त-स्पष्ट अंकगणित के मूल्य और इसे तेजी से चलाने के लिए प्रयुक्त करने की मूल्य के बीच एक सहनीय समझौता है; बहुत जल्द प्रिसिजन के दो और बाइट्स सहनीय हो जाएंगे, और अंततः 16-बाइट फॉर्मेट ... व्यापक प्रिसिजन की ओर उस तरह का क्रमिक विकास पहले से ही देखने में था जब आईईईई 754 या फ़्लोटिंग-पॉइंट अंकगणित के लिए आईईईई मानक 754 तैयार किया गया था।[2]

आईईईई 754-2008 में 128-बिट बेस-2 फॉर्मेट को आधिकारिक रूप से बाइनरी128 कहा जाता है।

आईईईई 754 क्वाड्रुपल -प्रिसिजन बाइनरी फ़्लोटिंग-पॉइंट फॉर्मेट: बाइनरी128

आईईईई 754 मानक एक बाइनरी128 को इस प्रकार निर्दिष्ट करता है:

- साइन बिट: 1 बिट

- घातांक चौड़ाई: 15 बिट्स

- महत्वपूर्ण प्रिसिजन (अंकगणित): 113 बिट्स (112 स्पष्ट रूप से संग्रहीत)

यह 33 से 36 महत्वपूर्ण दशमलव अंकों तक स्पष्टता देता है। यदि अधिकतम 33 महत्वपूर्ण अंकों वाली एक दशमलव स्ट्रिंग को सामान्य संख्या देते हुए आईईईई 754 चतुर्गुण-स्पष्ट फॉर्मेट में परिवर्तित किया जाता है, और फिर समान अंकों की संख्या के साथ दशमलव स्ट्रिंग में परिवर्तित किया जाता है, तो अंतिम परिणाम मूल स्ट्रिंग से मेल खाना चाहिए। यदि आईईईई 754 क्वाड्रुपल -स्पष्ट संख्या को कम से कम 36 महत्वपूर्ण अंकों के साथ दशमलव स्ट्रिंग में परिवर्तित किया जाता है और फिर वापस क्वाड्रुपल -स्पष्ट प्रतिनिधित्व में परिवर्तित किया जाता है, तो अंतिम परिणाम मूल संख्या से मेल खाना चाहिए।[3]

जब तक घातांक को सभी शून्यों के साथ संग्रहीत नहीं किया जाता है तब तक प्रारूप को मान 1 के साथ एक अंतर्निहित लीड बिट के साथ लिखा जाता है। इस प्रकार मेमोरी फॉर्मेट में महत्व के केवल 112 बिट्स दिखाई देते हैं, किंतु कुल परिशुद्धता 113 बिट्स (लगभग 34 दशमलव अंक: log10(2113) ≈ 34.016 है। बिट्स को इस प्रकार रखा गया है:

घातांक एन्कोडिंग

क्वाड्रुपल -स्पष्ट बाइनरी फ़्लोटिंग-पॉइंट एक्सपोनेंट को ऑफसेट बाइनरी प्रतिनिधित्व का उपयोग करके एन्कोड किया गया है, जिसमें शून्य ऑफसेट 16383 है; इसे आईईईई 754 मानक में प्रतिपादक पूर्वाग्रह के रूप में भी जाना जाता है।

- Emin = 000116 − 3FFF16 = −16382

- Emax = 7FFE16 − 3FFF16 = 16383

- घातांक पूर्वाग्रह = 3FFF16 = 16383

इस प्रकार, जैसा कि ऑफसेट बाइनरी प्रतिनिधित्व द्वारा परिभाषित किया गया है, वास्तविक घातांक प्राप्त करने के लिए, 16383 के ऑफसेट को संग्रहीत घातांक से घटाना होगा।

संग्रहीत घातांक 000016 और 7FFF16 की विशेष रूप से व्याख्या की गई है।

| प्रतिपादक | सार्थकता शून्य | सार्थकतथा गैर-शून्य | समीकरण |

|---|---|---|---|

| 000016 | 0, −0 | असामान्य संख्याएँ | (−1)signbit × 2−16382 × 0.महत्वपूर्णबिट्स2 |

| 000116, ..., 7FFE16 | सामान्यीकृत मूल्य | (−1)signbit × 2exponentbits2 − 16383 × 1.महत्वपूर्णबिट्स2 | |

| 7FFF16 | ±∞ | NaN (शांत, सिग्नलिंग) | |

न्यूनतम सख्ती से धनात्मक (असामान्य) मान 2−16494 ≈ 10−4965 है और इसकी स्पष्टता केवल एक बिट है। न्यूनतम धनात्मक सामान्य मान 2−16382 ≈ 3.3621 × 10−4932 है और इसकी स्पष्टता 113 बिट्स अर्थात ±2−16494 भी है। अधिकतम प्रतिनिधित्व योग्य मान 216384 − 216271 ≈ 1.1897 × 104932. है।

क्वाड्रुपल प्रिसिजन उदाहरण

ये उदाहरण हेक्साडेसिमल में बिट प्रतिनिधित्व में दिए गए हैं, फ़्लोटिंग-पॉइंट मान का। इसमें संकेत, (पक्षपातपूर्ण) प्रतिपादक और महत्व सम्मिलित हैं।

0000 0000 0000 0000 0000 0000 0000 000116 = 2−16382 × 2−112 = 2−16494

≈ 6.4751751194380251109244389582276465525 × 10−4966

(smallest positive subnormal number)

0000 ffff ffff ffff ffff ffff ffff ffff16 = 2−16382 × (1 − 2−112)

≈ 3.3621031431120935062626778173217519551 × 10−4932

(largest subnormal number)

0001 0000 0000 0000 0000 0000 0000 000016 = 2−16382

≈ 3.3621031431120935062626778173217526026 × 10−4932

(smallest positive normal number)

7ffe ffff ffff ffff ffff ffff ffff ffff16 = 216383 × (2 − 2−112)

≈ 1.1897314953572317650857593266280070162 × 104932

(largest normal number)

3ffe ffff ffff ffff ffff ffff ffff ffff16 = 1 − 2−113

≈ 0.9999999999999999999999999999999999037

(largest number less than one)

3fff 0000 0000 0000 0000 0000 0000 000016 = 1 (one)3fff 0000 0000 0000 0000 0000 0000 000116 = 1 + 2−112

≈ 1.0000000000000000000000000000000001926

(smallest number larger than one)

c000 0000 0000 0000 0000 0000 0000 000016 = −20000 0000 0000 0000 0000 0000 0000 000016 = 0

8000 0000 0000 0000 0000 0000 0000 000016 = −07fff 0000 0000 0000 0000 0000 0000 000016 = infinity

ffff 0000 0000 0000 0000 0000 0000 000016 = −infinity4000 921f b544 42d1 8469 898c c517 01b816 ≈ π3ffd 5555 5555 5555 5555 5555 5555 555516 ≈ 1/3डिफ़ॉल्ट रूप से, महत्व में बिट्स की विषम संख्या के कारण, 1/3 राउंड दोहरी परिशुद्धता की तरह नीचे आते हैं। तो गोलाकार बिंदु से परे बिट्स 0101... हैं जो कि अंतिम स्थान पर एक इकाई के 1/2 से कम है।

डबल-डबल अंकगणित

दोहरे-प्रिसिजन मानों के जोड़े का उपयोग करके लगभग क्वाड्रुपल प्रिसिजन को प्रयुक्त करने की एक सामान्य सॉफ़्टवेयर तकनीक को कभी-कभी 'डबल-डबल अंकगणित' कहा जाता है।[4][5][6] 53-बिट महत्व के साथ आईईईई डबल-स्पष्ट मानों के जोड़े का उपयोग करते हुए, डबल-डबल अंकगणित कम से कम महत्व वाले संख्याओं पर संचालन प्रदान करता है [4] 2 × 53 = 106 bits (वास्तव में 107 बिट्स [7] कुछ सबसे बड़े मानों को छोड़कर, सीमित घातांक सीमा के कारण), आईईईई बाइनरी128 क्वाड्रुपल प्रिसिजन के 113-बिट महत्व से केवल थोड़ा कम स्पष्ट डबल-डबल की सीमा अनिवार्य रूप से डबल-स्पष्ट फॉर्मेट के समान ही रहती है क्योंकि घातांक में अभी भी 11 बिट हैं,[4] आईईईई क्वाड्रुपल प्रिसिजन (की एक सीमा) के 15-बिट प्रतिपादक से अधिक कम है (डबल- के लिए 1.8 × 10308 की रेंज) बाइनरी128 के लिए डबल बनाम 1.2 × 104932)।

विशेष रूप से, डबल-डबल तकनीक में एक डबल-डबल/क्वाड्रुपल-स्पष्ट मान q को दो दोहरे-स्पष्ट मान x और y के योग q = x + y के रूप में दर्शाया जाता है, जिनमें से प्रत्येक q के महत्व का आधा भाग प्रदान करता है।[5] अर्थात्, जोड़ी (x, y) को q के स्थान पर संग्रहीत किया जाता है, और q मान (+, -, ×, ...) पर संचालन x और y मानों पर समतुल्य (किंतु अधिक सम्मिश्र ) संचालन में बदल दिया जाता है। इस प्रकार, इस तकनीक में अंकगणित दोहरे-परिशुद्धता संचालन के अनुक्रम में कम हो जाता है; चूंकि डबल-प्रिसिजन अंकगणित समान्यत: हार्डवेयर में प्रयुक्त किया जाता है, डबल-डबल अंकगणित समान्यत: अधिक सामान्य इच्छित -स्पष्ट अंकगणित तकनीकों की तुलना में अधिक तेज होता है।[4][5]

ध्यान दें कि डबल-डबल अंकगणित में निम्नलिखित विशेष विशेषताएं हैं:[8]

- जैसे-जैसे मूल्य का परिमाण घटता है, अतिरिक्त परिशुद्धता की मात्रा भी घटती जाती है। इसलिए, सामान्यीकृत सीमा में सबसे छोटी संख्या दोगुनी परिशुद्धता से संकीर्ण है। पूर्ण स्पष्टता के साथ सबसे छोटी संख्या 1000...02 (106 zeros) × 2−1074 या 1.000...02 (106 zeros) × 2−968 है। वे संख्याएँ जिनका परिमाण 2−1021 से छोटा है, उनमें दोहरी परिशुद्धता की तुलना में अतिरिक्त परिशुद्धता नहीं होगी।

- प्रिसिजन के बिट्स की वास्तविक संख्या भिन्न हो सकती है। सामान्य रूप से संख्या के निम्न-क्रम वाले भाग का परिमाण उच्च-क्रम वाले भाग के आधे यूएलपी से अधिक नहीं होता है। यदि निम्न-क्रम वाला भाग उच्च-क्रम वाले भाग के आधे यूएलपी से कम है, तो उच्च-क्रम और निम्न-क्रम संख्याओं के महत्वपूर्ण के बीच महत्वपूर्ण बिट्स (या तो सभी 0 या सभी 1) निहित हैं। कुछ एल्गोरिदम जो महत्व में बिट्स की एक निश्चित संख्या पर भरोसा करते हैं, 128-बिट लंबी दोहरी संख्याओं का उपयोग करते समय विफल हो सकते हैं।

- उपरोक्त कारण के कारण, 1 + 2−1074 जैसे मानों का प्रतिनिधित्व करना संभव है, जो 1 से बड़ी सबसे छोटी प्रतिनिधित्व योग्य संख्या है।

डबल-डबल अंकगणित के अतिरिक्त, यदि किसी उच्च प्रिसिजन फ़्लोटिंग-पॉइंट लाइब्रेरी के बिना उच्च प्रिसिजन की आवश्यकता होती है, तो ट्रिपल-डबल या क्वाड-डबल अंकगणित उत्पन्न करना भी संभव है। उन्हें क्रमशः तीन (या चार) दोहरे-स्पष्ट मानों के योग के रूप में दर्शाया जाता है। वे क्रमशः कम से कम 159/161 और 212/215 बिट्स के साथ संचालन का प्रतिनिधित्व कर सकते हैं।

एक समान तकनीक का उपयोग डबल-क्वाड अंकगणित का उत्पादन करने के लिए किया जा सकता है, जिसे दो क्वाड्रुपल -स्पष्ट मानों के योग के रूप में दर्शाया जाता है। वे कम से कम 226 (या 227) बिट्स के साथ संचालन का प्रतिनिधित्व कर सकते हैं।[9]

कार्यान्वयन

क्वाड्रुपल प्रिसिजन को अधिकांशतः सॉफ्टवेयर में विभिन्न तकनीकों द्वारा प्रयुक्त किया जाता है (जैसे कि उपरोक्त डबल-डबल तकनीक, चूँकि वह तकनीक आईईईई क्वाड्रुपल प्रिसिजन को प्रयुक्त नहीं करती है), क्योंकि 2016 तक क्वाड्रुपल प्रिसिजन के लिए प्रत्यक्ष हार्डवेयर समर्थन कम समान्य है (नीचे या हार्डवेयर समर्थन देखें)। क्वाड्रुपल (या उच्चतर) प्रिसिजन प्राप्त करने के लिए कोई सामान्य इच्छित -स्पष्ट अंकगणितीय लाइब्रेरी का उपयोग कर सकता है, किंतु विशेष क्वाड्रुपल -प्रिसिजन कार्यान्वयन उच्च प्रदर्शन प्राप्त कर सकता है।

कंप्यूटर-लैंग्वेज समर्थन

एक अलग प्रश्न यह है कि किस हद तक क्वाड्रुपल -स्पष्ट प्रकारों को सीधे कंप्यूटर प्रोग्रामिंग लैंग्वेज ओं में सम्मिलित किया जाता है।

फोरट्रान में क्वाड्रुपल परिशुद्धता real(real128) द्वारा निर्दिष्ट की जाती है (फोरट्रान 2008 से मॉड्यूल iso_fortran_env का उपयोग किया जाना चाहिए, अधिकांश प्रोसेसर पर निरंतर real128 16 के बराबर है), या real(selected_real_kind(33, 4931))के रूप में, या एक गैर में -वास्तविक जैसा मानक REAL*16 (उदाहरण के लिए, क्वाड्रुपल-प्रिसिजन REAL*16इंटेल फोरट्रान कंपाइलर [10] और x86, x86-64 और इटेनियम आर्किटेक्चर पर जीएनयू फोरट्रान कंपाइलर [11] द्वारा समर्थित है।)

सी प्रोग्रामिंग लैंग्वेज के लिए, आईएसओ/आईईसी टीएस 18661-3 (सी, इंटरचेंज और विस्तारित प्रकारों के लिए फ़्लोटिंग-पॉइंट एक्सटेंशन) _Float128 को आईईईई 754 चतुर्भुज-स्पष्ट प्रारूप (बाइनरी128) को प्रयुक्त करने वाले प्रकार के रूप में निर्दिष्ट करता है।[12] वैकल्पिक रूप से, कुछ प्रणालियों और कंपाइलरों के साथ C/C++ में, क्वाड्रुपल परिशुद्धता को लंबे डबल प्रकार द्वारा निर्दिष्ट किया जा सकता है, किंतु यह लैंग्वेज के लिए आवश्यक नहीं है (जिसे कम से कम double जितना स्पष्ट होने के लिए केवल long double की आवश्यकता होती है), न ही ऐसा है यह समान्य है.

x86 और x86-64 पर, सबसे समान्य C/C++ कंपाइलर 80-बिट विस्तारित परिशुद्धता के रूप में long double प्रयुक्त करते हैं (उदाहरण के लिए जीएनयू C कंपाइलर जीसीसी[13] और इंटेल C++ कंपाइलर/Qlong‑double स्विच [14] के साथ) या बस क्वाड्रुपल परिशुद्धता के अतिरिक्त दोहरी परिशुद्धता (उदाहरण के लिए माइक्रोसॉफ्ट विजुअल C++[15]) का पर्याय बन गया है। एआरएम 64-बिट आर्किटेक्चर (एआर्क64) के लिए प्रक्रिया कॉल मानक निर्दिष्ट करता है कि long double आईईईई 754 क्वाड्रुपल-प्रिसिजन प्रारूप से मेल खाता है। [16] कुछ अन्य आर्किटेक्चर पर, कुछ C/C++ कंपाइलर लंबे समय तक डबल को क्वाड्रुपल परिशुद्धता के रूप में प्रयुक्त करते हैं, उदाहरण के लिए। पावरपीसी पर जीसीसी (डबल-डबल[17][18][19] के रूप में) और स्पार्क,[20] या स्पार्क पर सन स्टूडियो कंपाइलर[21] तथापि long double क्वाड्रुपल परिशुद्धता नहीं है, तथापि, कुछ C/C++ कंपाइलर एक विस्तार के रूप में एक गैरमानक क्वाड्रुपल-स्पष्ट प्रकार प्रदान करते हैं। उदाहरण के लिए, जीसीसी x86, x86-64 और इटेनियम सीपीयू के लिए __float128 नामक एक क्वाड्रुपल-परिशुद्धता प्रकार प्रदान करता है, [22] और पावरपीसी पर -mfloat128-हार्डवेयर या -mfloat128 विकल्पों का उपयोग करके आईईईई 128-बिट फ़्लोटिंग-पॉइंट के रूप में प्रदान करता है;[23] और x86 और x86-64 के लिए Intel के C/C++ कंपाइलर के कुछ संस्करण _Quad नामक एक गैर-मानक चतुर्भुज-स्पष्ट प्रकार की आपूर्ति करते हैं। [24]

गूगल की कार्य-प्रगति वाली लैंग्वेज कार्बन (प्रोग्रामिंग लैंग्वेज ) 'f128' नामक प्रकार के साथ इसके लिए समर्थन प्रदान करती है।[25]

लैब्ररी और टूलबॉक्स

- जीएनयू कंपाइलर संग्रह क्वाड-प्रिसिजन गणित लाइब्रेरी, लिबक्वाडमैथ,

__float128और__complex128संचालन प्रदान करता है। - बूस्ट मल्टीप्रिसिज़न लाइब्रेरी बूस्ट.मल्टीप्रिसिजन

__float128और _Quad प्रकारों के लिए एकीकृत क्रॉस-प्लेटफ़ॉर्म C++ इंटरफ़ेस प्रदान करता है, और इसमें मानक गणित लाइब्रेरी का एक कस्टम कार्यान्वयन सम्मिलित है।[26] - मैटलैब के लिए मल्टीप्रिसिजन कंप्यूटिंग टूलबॉक्स मैटलैब में क्वाड्रुपल -प्रिसिजन गणना की अनुमति देता है। इसमें मूलभूत अंकगणितीय कार्यक्षमता के साथ-साथ संख्यात्मक विधियाँ, सघन और विरल रैखिक बीजगणित भी सम्मिलित हैं।[27]

- डबलफ्लोट्स[28] पैकेज जूलिया प्रोग्रामिंग लैंग्वेज के लिए डबल-डबल संगणना के लिए समर्थन प्रदान करता है।

- Doubledouble.py [29] लाइब्रेरी पायथन में डबल-डबल गणनाओं को सक्षम बनाती है।

- मैथमेटिका आईईईई क्वाड-प्रिसिजन संख्याओं का समर्थन करता है: 128-बिट फ़्लोटिंग-पॉइंट मान (रियल128), और 256-बिट सम्मिश्र मान (कॉम्प्लेक्स256)।

हार्डवेयर समर्थन

आईईईई चतुर्भुज प्रिसिजन को 1998 में आईबीएम सिस्टम/390 G5 में जोड़ा गया था,[30] और बाद के z/आर्किटेक्चर प्रोसेसर में हार्डवेयर में समर्थित है।[31][32] आईबीएम पॉवर9 सीपीयू (पावर आईएसए या पावर आईएसए v.3.0|पावर आईएसए 3.0) में मूल 128-बिट हार्डवेयर समर्थन है।[23]

आईईईई 128-बिट फ़्लोट का मूल समर्थन पीए-रिस्क 1.0 में परिभाषित किया गया है,[33] और स्पार्क V8 में[34] और वी9[35] आर्किटेक्चर (उदाहरण के लिए 16 क्वाड-प्रिसिजन रजिस्टर %q0, %q4, ... हैं), as of 2004[update] किंतु कोई भी स्पार्क सीपीयू हार्डवेयर में क्वाड-प्रिसिजन ऑपरेशन प्रयुक्त नहीं करता है .[36]

आईबीएम हेक्साडेसिमल फ्लोटिंग-पॉइंट या एक्सटेंडेड-प्रिसिजन 128-बिट या नॉन-आईईईई एक्सटेंडेड-प्रिसिजन (128 बिट्स ऑफ स्टोरेज, 1 साइन बिट, 7 एक्सपोनेंट बिट्स, 112 फ्रैक्शन बिट्स, 8 बिट्स अप्रयुक्त) को आईबीएम सिस्टम/370 सीरीज (1970-1980 के दशक) में जोड़ा गया था और 196 में कुछ आईबीएम सिस्टम/360 या सिस्टम/360 मॉडल पर उपलब्ध था। 0एस (सिस्टम/360-85,[37] -195, और अन्य विशेष अनुरोध द्वारा या ओएस सॉफ़्टवेयर द्वारा सिम्युलेटेड)।

सीमेंस 7.700 और 7.500 श्रृंखला मेनफ्रेम और उनके उत्तराधिकारी आईबीएम सिस्टम/360 और सिस्टम/370 के समान फ़्लोटिंग-पॉइंट फॉर्मेट और निर्देशों का समर्थन करते हैं।

वैक्स प्रोसेसर ने गैर-आईईईई क्वाड्रपल-प्रिसिजन फ़्लोटिंग पॉइंट को अपने H फ़्लोटिंग-पॉइंट फॉर्मेट के रूप में कार्यान्वित किया गया था। इसमें एक साइन बिट, एक 15-बिट एक्सपोनेंट और 112-फ़्रेक्शन बिट्स थे, चूँकि मेमोरी में लेआउट आईईईई क्वाड्रुपल प्रिसिजन से अधिक अलग था और एक्सपोनेंट पूर्वाग्रह भी भिन्न था। प्रारंभिक वैक्स प्रोसेसरों में से केवल कुछ ने हार्डवेयर में H फ़्लोटिंग-पॉइंट निर्देशों को प्रयुक्त किया था अन्य सभी ने सॉफ़्टवेयर में H फ़्लोटिंग-पॉइंट का अनुकरण किया था।

एनईसी एसएक्स-अरोड़ा त्सुबासा आर्किटेक्चर 128-बिट बाइनरी आईईईई754 क्वाड स्पष्ट संख्याओं को जोड़ने, घटाने, गुणा करने और तुलना करने का समर्थन करता है।[38] दो निकटतम 64-बिट रजिस्टर का उपयोग किया जाता है। क्वाडप्रिसिजन अंकगणित वेक्टर रजिस्टर में समर्थित नहीं है।[39]

आरआईएससी-वी आर्किटेक्चर 128-बिट बाइनरी आईईईई 754-2008 फ्लोटिंग पॉइंट अंकगणित के लिए Q (क्वाड-प्रिसिजन) एक्सटेंशन निर्दिष्ट करता है।[40] एल एक्सटेंशन (अभी तक प्रमाणित नहीं) 64-बिट और 128-बिट दशमलव फ़्लोटिंग पॉइंट निर्दिष्ट करेगा।[41]

क्वाड्रपल-प्रिसिजन (128-बिट) हार्डवेयर कार्यान्वयन को 128-बिट एफपीयू के साथ अस्पष्ट नहीं किया जाना चाहिए जो एकल निर्देश, कई डेटा निर्देशों को प्रयुक्त करता है, जैसे कि स्ट्रीमिंग एसआईएमडी एक्सटेंशन या अल्टीवेक, जो चार 32-बिट सिंगल-प्रिसिजन या दो 64-बिट डबल-प्रिसिजन मानों के 128-बिट वेक्टर प्रोसेसर को संदर्भित करता है जो एक साथ संचालित होते हैं।

यह भी देखें

- आईईईई 754, फ्लोटिंग-पॉइंट अंकगणित के लिए आईईईई मानक

- आईएसओ/आईईसी 10967, लैंग्वेज स्वतंत्र अंकगणित

- प्राचीन डेटा प्रकार

- क्यू संकेतन (वैज्ञानिक संकेतन)

संदर्भ

- ↑ David H. Bailey; Jonathan M. Borwein (July 6, 2009). "उच्च परिशुद्धता संगणना और गणितीय भौतिकी" (PDF).

- ↑ Higham, Nicholas (2002). "Designing stable algorithms" in Accuracy and Stability of Numerical Algorithms (2 ed). SIAM. p. 43.

- ↑ William Kahan (1 October 1987). "Lecture Notes on the Status of IEEE Standard 754 for Binary Floating-Point Arithmetic" (PDF).

- ↑ 4.0 4.1 4.2 4.3 Yozo Hida, X. Li, and D. H. Bailey, Quad-Double Arithmetic: Algorithms, Implementation, and Application, Lawrence Berkeley National Laboratory Technical Report LBNL-46996 (2000). Also Y. Hida et al., Library for double-double and quad-double arithmetic (2007).

- ↑ 5.0 5.1 5.2 J. R. Shewchuk, Adaptive Precision Floating-Point Arithmetic and Fast Robust Geometric Predicates, Discrete & Computational Geometry 18:305–363, 1997.

- ↑ Knuth, D. E. कंप्यूटर प्रोग्रामिंग की कला (2nd ed.). chapter 4.2.3. problem 9.

- ↑ Robert Munafo F107 and F161 High-Precision Floating-Point Data Types (2011).

- ↑ 128-Bit Long Double Floating-Point Data Type

- ↑ sourceware.org Re: The state of glibc libm

- ↑ "GCC 4.6 Release Series - Changes, New Features, and Fixes". Retrieved 2010-02-06.

- ↑ "इंटेल फोरट्रान कंपाइलर उत्पाद संक्षिप्त (web.archive.org पर संग्रहीत प्रति)" (PDF). Su. Archived from the original on October 25, 2008. Retrieved 2010-01-23.

{{cite web}}: CS1 maint: unfit URL (link) - ↑ "ISO/IEC TS 18661-3" (PDF). 2015-06-10. Retrieved 2019-09-22.

- ↑ i386 and x86-64 Options (archived copy on web.archive.org), Using the GNU Compiler Collection.

- ↑ Intel Developer Site

- ↑ MSDN homepage, about Visual C++ compiler

- ↑ "Procedure Call Standard for the ARM 64-bit Architecture (AArch64)" (PDF). 2013-05-22. Archived from the original (PDF) on 2019-10-16. Retrieved 2019-09-22.

- ↑ RS/6000 and PowerPC Options, Using the GNU Compiler Collection.

- ↑ Inside Macintosh - PowerPC Numerics Archived October 9, 2012, at the Wayback Machine

- ↑ 128-bit long double support routines for Darwin

- ↑ SPARC Options, Using the GNU Compiler Collection.

- ↑ The Math Libraries, Sun Studio 11 Numerical Computation Guide (2005).

- ↑ Additional Floating Types, Using the GNU Compiler Collection

- ↑ 23.0 23.1 "GCC 6 Release Series - Changes, New Features, and Fixes". Retrieved 2016-09-13.

- ↑ Intel C++ Forums (2007).

- ↑ "कार्बन भाषा का मुख्य भंडार - भाषा डिज़ाइन". GitHub. 2022-08-09. Retrieved 2022-09-22.

- ↑ "Boost.Multiprecision - float128". Retrieved 2015-06-22.

- ↑ Pavel Holoborodko (2013-01-20). "MATLAB में तेज़ चौगुनी परिशुद्धता संगणनाएँ". Retrieved 2015-06-22.

- ↑ "DoubleFloats.jl". GitHub.

- ↑ "डॉबलेडोउब्ले.पी". GitHub.

- ↑ Schwarz, E. M.; Krygowski, C. A. (September 1999). "The S/390 G5 floating-point unit". IBM Journal of Research and Development. 43 (5/6): 707–721. CiteSeerX 10.1.1.117.6711. doi:10.1147/rd.435.0707.

- ↑ Gerwig, G. and Wetter, H. and Schwarz, E. M. and Haess, J. and Krygowski, C. A. and Fleischer, B. M. and Kroener, M. (May 2004). "The IBM eServer z990 floating-point unit. IBM J. Res. Dev. 48; pp. 311-322".

{{cite news}}: CS1 maint: multiple names: authors list (link) - ↑ Eric Schwarz (June 22, 2015). "The IBM z13 SIMD Accelerators for Integer, String, and Floating-Point" (PDF). Retrieved July 13, 2015.

- ↑ "बाइनरी इंटरचेंज प्रारूपों के लिए कार्यान्वयनकर्ता समर्थन". grouper.ieee.org. Archived from the original on 2017-10-27. Retrieved 2021-07-15.

- ↑ The SPARC Architecture Manual: Version 8 (archived copy on web.archive.org) (PDF). SPARC International, Inc. 1992. Archived from the original (PDF) on 2005-02-04. Retrieved 2011-09-24.

SPARC is an instruction set architecture (ISA) with 32-bit integer and 32-, 64-, and 128-bit IEEE Standard 754 floating-point as its principal data types.

- ↑ David L. Weaver; Tom Germond, eds. (1994). The SPARC Architecture Manual: Version 9 (archived copy on web.archive.org) (PDF). SPARC International, Inc. Archived from the original (PDF) on 2012-01-18. Retrieved 2011-09-24.

Floating-point: The architecture provides an IEEE 754-compatible floating-point instruction set, operating on a separate register file that provides 32 single-precision (32-bit), 32 double-precision (64-bit), 16 quad-precision (128-bit) registers, or a mixture thereof.

- ↑ "SPARC Behavior and Implementation". Numerical Computation Guide — Sun Studio 10. Sun Microsystems, Inc. 2004. Retrieved 2011-09-24.

There are four situations, however, when the hardware will not successfully complete a floating-point instruction: ... The instruction is not implemented by the hardware (such as ... quad-precision instructions on any SPARC FPU).

- ↑ Padegs A (1968). "Structural aspects of the System/360 Model 85, III: Extensions to floating-point architecture". IBM Systems Journal. 7: 22–29. doi:10.1147/sj.71.0022.

- ↑ Vector Engine AssemblyLanguage Reference Manual, Chapter4 Assembler Syntax page 23.

- ↑ SX-Aurora TSUBASA Architecture Guide Revision 1.1 (p. 38, 60).

- ↑ RISC-V ISA Specification v. 20191213, Chapter 13, “Q” Standard Extension for Quad-Precision Floating-Point, page 79.

- ↑ [1] Chapter 15 (p. 95).

बाहरी संबंध

- High-Precision Software Directory

- QPFloat, a free software (GPL) software library for quadruple-precision arithmetic

- HPAlib, a free software (LGPL) software library for quad-precision arithmetic

- libquadmath, the GCC quad-precision math library

- IEEE-754 Analysis, Interactive web page for examining Binary32, Binary64, and Binary128 floating-point values