डिले-लॉक लूप: Difference between revisions

No edit summary |

No edit summary |

||

| (4 intermediate revisions by 2 users not shown) | |||

| Line 2: | Line 2: | ||

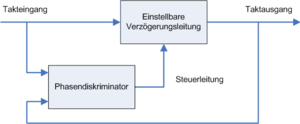

[[File:Delay locked loop.png|thumb]]इलेक्ट्रॉनिक्स में, '''डिले-लॉक लूप (डीएलएल)''' चरण-लॉक लूप (पीएलएल) के समान छद्म-[[डिजिटल इलेक्ट्रॉनिक्स]] परिपथ है, जिसमें मुख्य अंतर आंतरिक वोल्टेज-नियंत्रित ऑसिलेटर की अनुपस्थिति है, जिसे डिले लाइन द्वारा प्रतिस्थापित किया जाता है। | [[File:Delay locked loop.png|thumb]]इलेक्ट्रॉनिक्स में, '''डिले-लॉक लूप (डीएलएल)''' चरण-लॉक लूप (पीएलएल) के समान छद्म-[[डिजिटल इलेक्ट्रॉनिक्स]] परिपथ है, जिसमें मुख्य अंतर आंतरिक वोल्टेज-नियंत्रित ऑसिलेटर की अनुपस्थिति है, जिसे डिले लाइन द्वारा प्रतिस्थापित किया जाता है। | ||

एक डीएलएल का उपयोग क्लॉक सिग्नल के चरण को बदलने के लिए किया जा सकता है (आवधिक फ़ंक्शन [[तरंग]] के साथ सिग्नल), सामान्यतः एकीकृत परिपथ की 'क्लॉक राइज'-टू-''डेटा आउटपुट वैलिड' टाइमिंग विशेषताओं को बढ़ाने के लिए (जैसे [[गतिशील रैंडम-एक्सेस मेमोरी]] डिवाइस के रूप में) डीएलएल का उपयोग [[ घड़ी की वसूली |घड़ी पुनर्प्राप्ति]] (सीडीआर) के लिए भी किया जा सकता है। बाहर से, डीएलएल को डिजिटल परिपथ के क्लॉक पाथ में रखे गए | एक डीएलएल का उपयोग क्लॉक सिग्नल के चरण को बदलने के लिए किया जा सकता है (आवधिक फ़ंक्शन [[तरंग]] के साथ सिग्नल), सामान्यतः एकीकृत परिपथ की 'क्लॉक राइज'-टू-''डेटा आउटपुट वैलिड' टाइमिंग विशेषताओं को बढ़ाने के लिए (जैसे [[गतिशील रैंडम-एक्सेस मेमोरी]] डिवाइस के रूप में) डीएलएल का उपयोग [[ घड़ी की वसूली |घड़ी पुनर्प्राप्ति]] (सीडीआर) के लिए भी किया जा सकता है। बाहर से, डीएलएल को डिजिटल परिपथ के क्लॉक पाथ में रखे गए ऋणात्मक डिले गेट के रूप में देखा जा सकता है।'' | ||

डीएलएल का मुख्य घटक डिले श्रृंखला है जो आउटपुट-टू-इनपुट से जुड़े कई डिले गेट्स से बना है। श्रृंखला का इनपुट (और इस प्रकार डीएलएल का) उस घड़ी से जुड़ा है जिसे | डीएलएल का मुख्य घटक डिले श्रृंखला है जो आउटपुट-टू-इनपुट से जुड़े कई डिले गेट्स से बना है। श्रृंखला का इनपुट (और इस प्रकार डीएलएल का) उस घड़ी से जुड़ा है जिसे ऋणात्मक रूप से डिलेित किया जाना है। डिले श्रृंखला के प्रत्येक चरण से बहुसंकेतक जुड़ा हुआ है; ऋणात्मक डिले प्रभाव उत्पन्न करने के लिए नियंत्रण परिपथ स्वचालित रूप से इस मल्टीप्लेक्सर के चयनकर्ता को अपडेट करता है। डीएलएल का आउटपुट परिणामी, ऋणात्मक रूप से डिलेित क्लॉक सिग्नल है। | ||

[[File:Delay locked loop, 0th order type 0 and 1st order type 1.png|thumb|center|660px|{{center|विलंब लॉक लूप एक परिवर्तनीय विलंब रेखा है जिसका विलंब एक संदर्भ घड़ी की अवधि की अवधि के लिए लॉक किया गया है।<br /> | [[File:Delay locked loop, 0th order type 0 and 1st order type 1.png|thumb|center|660px|{{center|विलंब लॉक लूप एक परिवर्तनीय विलंब रेखा है जिसका विलंब एक संदर्भ घड़ी की अवधि की अवधि के लिए लॉक किया गया है।<br /> | ||

लूप में सिग्नल प्रोसेसिंग तत्व के आधार पर (एक फ्लैट एम्पलीफायर या एक इंटीग्रेटर),<br />डीएलएल लूप 0वें क्रम प्रकार 0 या प्रथम क्रम प्रकार 1 का हो सकता है.}}]]डीएलएल और पीएलएल के बीच अंतर देखने का दूसरी विधि यह है कि डीएलएल चर चरण ब्लॉक का उपयोग करता है, जबकि पीएलएल चर आवृत्ति ब्लॉक का उपयोग करता है। | लूप में सिग्नल प्रोसेसिंग तत्व के आधार पर (एक फ्लैट एम्पलीफायर या एक इंटीग्रेटर),<br />डीएलएल लूप 0वें क्रम प्रकार 0 या प्रथम क्रम प्रकार 1 का हो सकता है.}}]]डीएलएल और पीएलएल के बीच अंतर देखने का दूसरी विधि यह है कि डीएलएल चर चरण ब्लॉक का उपयोग करता है, जबकि पीएलएल चर आवृत्ति ब्लॉक का उपयोग करता है। | ||

| Line 14: | Line 14: | ||

नियंत्रण प्रणाली शब्दजाल में, डीएलएल क्रम में और पीएलएल के संबंध में टाइप में लूप है, क्योंकि इसमें नियंत्रित ब्लॉक में 1/एस कारक की कमी है: डिले लाइन में ट्रांसफर फ़ंक्शन चरण-आउट/चरण है इनमें केवल स्थिरांक है, इसके अतिरिक्त वीसीओ ट्रांसफर फ़ंक्शन G है पिछले वाक्यों में की गई तुलना में (जो उस आंकड़े के अनुरूप है जहां इंटीग्रेटर, न कि फ्लैट गेन का उपयोग किया जाता है), डीएलएल पहले क्रम का लूप है और टाइप 1 और दूसरे क्रम का पीएलएल और टाइप 2 है। बिना त्रुटि संकेत का एकीकरण, डीएलएल 0वां क्रम और प्रकार 0 होगा, और पीएलएल पहला क्रम और प्रकार 1 होता है। | नियंत्रण प्रणाली शब्दजाल में, डीएलएल क्रम में और पीएलएल के संबंध में टाइप में लूप है, क्योंकि इसमें नियंत्रित ब्लॉक में 1/एस कारक की कमी है: डिले लाइन में ट्रांसफर फ़ंक्शन चरण-आउट/चरण है इनमें केवल स्थिरांक है, इसके अतिरिक्त वीसीओ ट्रांसफर फ़ंक्शन G है पिछले वाक्यों में की गई तुलना में (जो उस आंकड़े के अनुरूप है जहां इंटीग्रेटर, न कि फ्लैट गेन का उपयोग किया जाता है), डीएलएल पहले क्रम का लूप है और टाइप 1 और दूसरे क्रम का पीएलएल और टाइप 2 है। बिना त्रुटि संकेत का एकीकरण, डीएलएल 0वां क्रम और प्रकार 0 होगा, और पीएलएल पहला क्रम और प्रकार 1 होता है। | ||

डिले श्रृंखला में तत्वों की संख्या सम होनी चाहिए, अन्यथा श्रृंखला के मध्यवर्ती नोड्स पर घड़ी का कर्तव्य चक्र अनियमित हो सकता है। | |||

यदि 2N +1 चरणों की विषम-संख्या थी, तो 50% कर्तव्य-चक्र कई बार N/(2N+1) बन जाएगा, कई बार (N+1)/(2N+1), घबराहट के बाद सही ताला के अनुरूप मूल्य के आसपास त्रुटि संकेत दता है। | यदि 2N +1 चरणों की विषम-संख्या थी, तो 50% कर्तव्य-चक्र कई बार N/(2N+1) बन जाएगा, कई बार (N+1)/(2N+1), घबराहट के बाद सही ताला के अनुरूप मूल्य के आसपास त्रुटि संकेत दता है। | ||

| Line 28: | Line 28: | ||

आगे यह टिप्पणी की जा सकती है कि, ऐसे स्थिति में जहां फ्लैट गेन के अतिरिक्त इंटीग्रेटर को चुना जाता है, जो पीएलएल प्राप्त किया जा सकता है वह अस्थिर है। | आगे यह टिप्पणी की जा सकती है कि, ऐसे स्थिति में जहां फ्लैट गेन के अतिरिक्त इंटीग्रेटर को चुना जाता है, जो पीएलएल प्राप्त किया जा सकता है वह अस्थिर है। | ||

चरण बदलाव को या तो निरपेक्ष रूप से ( | चरण बदलाव को या तो निरपेक्ष रूप से (डिले श्रृंखला गेट इकाइयों में), या घड़ी की अवधि के अनुपात के रूप में, या दोनों के रूप में निर्दिष्ट किया जा सकता है। | ||

== यह भी देखें == | == यह भी देखें == | ||

| Line 39: | Line 39: | ||

The Delay Lock Loop has been derived by J.J. Spilker, JR. and D.T. Magill, "The delay-lock discriminator--an optimum tracking device," Proc. IRE, vol.49, pp. 1403–1416, September 1961. | The Delay Lock Loop has been derived by J.J. Spilker, JR. and D.T. Magill, "The delay-lock discriminator--an optimum tracking device," Proc. IRE, vol.49, pp. 1403–1416, September 1961. | ||

[[Category:Created On 19/06/2023]] | [[Category:Created On 19/06/2023]] | ||

[[Category:Lua-based templates]] | |||

[[Category:Machine Translated Page]] | |||

[[Category:Pages with script errors]] | |||

[[Category:Short description with empty Wikidata description]] | |||

[[Category:Templates Vigyan Ready]] | |||

[[Category:Templates that add a tracking category]] | |||

[[Category:Templates that generate short descriptions]] | |||

[[Category:Templates using TemplateData]] | |||

[[Category:इलेक्ट्रॉनिक ऑसिलेटर्स]] | |||

[[Category:इलेक्ट्रॉनिक डिजाइन]] | |||

[[Category:एकीकृत सर्किट]] | |||

[[Category:गेट सरणियाँ]] | |||

[[Category:डिजिटल इलेक्ट्रॉनिक्स]] | |||

Latest revision as of 15:58, 29 August 2023

इलेक्ट्रॉनिक्स में, डिले-लॉक लूप (डीएलएल) चरण-लॉक लूप (पीएलएल) के समान छद्म-डिजिटल इलेक्ट्रॉनिक्स परिपथ है, जिसमें मुख्य अंतर आंतरिक वोल्टेज-नियंत्रित ऑसिलेटर की अनुपस्थिति है, जिसे डिले लाइन द्वारा प्रतिस्थापित किया जाता है।

एक डीएलएल का उपयोग क्लॉक सिग्नल के चरण को बदलने के लिए किया जा सकता है (आवधिक फ़ंक्शन तरंग के साथ सिग्नल), सामान्यतः एकीकृत परिपथ की 'क्लॉक राइज'-टू-डेटा आउटपुट वैलिड' टाइमिंग विशेषताओं को बढ़ाने के लिए (जैसे गतिशील रैंडम-एक्सेस मेमोरी डिवाइस के रूप में) डीएलएल का उपयोग घड़ी पुनर्प्राप्ति (सीडीआर) के लिए भी किया जा सकता है। बाहर से, डीएलएल को डिजिटल परिपथ के क्लॉक पाथ में रखे गए ऋणात्मक डिले गेट के रूप में देखा जा सकता है।

डीएलएल का मुख्य घटक डिले श्रृंखला है जो आउटपुट-टू-इनपुट से जुड़े कई डिले गेट्स से बना है। श्रृंखला का इनपुट (और इस प्रकार डीएलएल का) उस घड़ी से जुड़ा है जिसे ऋणात्मक रूप से डिलेित किया जाना है। डिले श्रृंखला के प्रत्येक चरण से बहुसंकेतक जुड़ा हुआ है; ऋणात्मक डिले प्रभाव उत्पन्न करने के लिए नियंत्रण परिपथ स्वचालित रूप से इस मल्टीप्लेक्सर के चयनकर्ता को अपडेट करता है। डीएलएल का आउटपुट परिणामी, ऋणात्मक रूप से डिलेित क्लॉक सिग्नल है।

डीएलएल और पीएलएल के बीच अंतर देखने का दूसरी विधि यह है कि डीएलएल चर चरण ब्लॉक का उपयोग करता है, जबकि पीएलएल चर आवृत्ति ब्लॉक का उपयोग करता है।

एक डीएलएल त्रुटि संकेत उत्पन्न करने के लिए इनपुट क्लॉक के साथ अपने अंतिम आउटपुट के चरण की तुलना करता है जो तब एकीकृत होता है और सभी डिले तत्वों को नियंत्रण के रूप में वापस खिलाया जाता है।नियंत्रण संकेत रखते हुए एकीकरण त्रुटि को शून्य पर जाने की अनुमति देता है, और इस प्रकार डिले, जहां उन्हें चरण लॉक के लिए होना चाहिए। चूंकि नियंत्रण संकेत सीधे चरण को प्रभावित करता है, यह सब आवश्यक है।

एक पीएलएल त्रुटि संकेत उत्पन्न करने के लिए आने वाले सिग्नल के साथ अपने ऑसीलेटर के चरण की तुलना करता है जिसे वोल्टेज-नियंत्रित ऑसीलेटर के लिए नियंत्रण सिग्नल बनाने के लिए एकीकृत किया जाता है। नियंत्रण संकेत दोलक की आवृत्ति को प्रभावित करता है, और चरण आवृत्ति का अभिन्न अंग है, इसलिए दूसरा एकीकरण अनिवार्य रूप से दोलक द्वारा ही किया जाता है।

नियंत्रण प्रणाली शब्दजाल में, डीएलएल क्रम में और पीएलएल के संबंध में टाइप में लूप है, क्योंकि इसमें नियंत्रित ब्लॉक में 1/एस कारक की कमी है: डिले लाइन में ट्रांसफर फ़ंक्शन चरण-आउट/चरण है इनमें केवल स्थिरांक है, इसके अतिरिक्त वीसीओ ट्रांसफर फ़ंक्शन G है पिछले वाक्यों में की गई तुलना में (जो उस आंकड़े के अनुरूप है जहां इंटीग्रेटर, न कि फ्लैट गेन का उपयोग किया जाता है), डीएलएल पहले क्रम का लूप है और टाइप 1 और दूसरे क्रम का पीएलएल और टाइप 2 है। बिना त्रुटि संकेत का एकीकरण, डीएलएल 0वां क्रम और प्रकार 0 होगा, और पीएलएल पहला क्रम और प्रकार 1 होता है।

डिले श्रृंखला में तत्वों की संख्या सम होनी चाहिए, अन्यथा श्रृंखला के मध्यवर्ती नोड्स पर घड़ी का कर्तव्य चक्र अनियमित हो सकता है।

यदि 2N +1 चरणों की विषम-संख्या थी, तो 50% कर्तव्य-चक्र कई बार N/(2N+1) बन जाएगा, कई बार (N+1)/(2N+1), घबराहट के बाद सही ताला के अनुरूप मूल्य के आसपास त्रुटि संकेत दता है।

2N को डीएलएल श्रृंखला के चरणों की संख्या कहते हुए, यह देखना सरल है कि ऊपर दिया गया आंकड़ा डीएलएल से पीएलएल में बदल जाता है, उसी चरण और आवृत्ति पर लॉक हो जाता है, यदि निम्नलिखित संशोधन किए गए थे:

- चरणों की संख्या को दो से विभाजित करना

- चरणों में से को उलटा बनाना

- संदर्भ घड़ी के अतिरिक्त चरणों की श्रृंखला के इनपुट को उसके आउटपुट से जोड़ना।

परिणामी श्रृंखला पिछली श्रृंखला की डिले के समान अवधि के साथ रिंग दोलक बन जाती है, और लूप उसी संदर्भ घड़ी को समान स्तर के त्रुटि संकेत के साथ लॉक करता है।

लूप क्रम और प्रकार दोनों एक-एक करके बढ़ाए जाते हैं।

आगे यह टिप्पणी की जा सकती है कि, ऐसे स्थिति में जहां फ्लैट गेन के अतिरिक्त इंटीग्रेटर को चुना जाता है, जो पीएलएल प्राप्त किया जा सकता है वह अस्थिर है।

चरण बदलाव को या तो निरपेक्ष रूप से (डिले श्रृंखला गेट इकाइयों में), या घड़ी की अवधि के अनुपात के रूप में, या दोनों के रूप में निर्दिष्ट किया जा सकता है।

यह भी देखें

- फेज-लॉक लूप (पीएलएल)

- डिजिटल घड़ी प्रबंधक (डीसीएम)

- घड़ी संकेत

संदर्भ

The Delay Lock Loop has been derived by J.J. Spilker, JR. and D.T. Magill, "The delay-lock discriminator--an optimum tracking device," Proc. IRE, vol.49, pp. 1403–1416, September 1961.