आईईईई 754-1985: Difference between revisions

m (added Category:Vigyan Ready using HotCat) |

m (22 revisions imported from alpha:आईईईई_754-1985) |

(No difference)

| |

Latest revision as of 22:15, 2 February 2024

आईईईई 754-1985[1] कंप्यूटर में फ्लोटिंग-पॉइंट नंबर्स का रिप्रजेंटेशन करने के लिए इंडस्ट्री स्टैण्डर्ड था, जिसे सामान्यतः 1985 में स्वीकार किया गया था और 2008 में आईईईई 754-2008 द्वारा प्रतिस्थापित किया गया था, और फिर 2019 में माइनर वर्ज़न आईईईई 754-2019 द्वारा प्रतिस्थापित किया गया था।[2] अपने 23 वर्षों के समय में, यह फ़्लोटिंग-पॉइंट कैलकुलेशन के लिए सबसे वाइड रूप से उपयोग किया जाने वाला फॉर्मेट था। इसे सॉफ़्टवेयर में, फ़्लोटिंग-पॉइंट लाइब्रेरीज़ के रूप में, और हार्डवेयर में, कई सीपीयू और एफपीयू के इंस्ट्रक्शन में इम्प्लीमेंट किया गया था। आईईईई 754-1985 बनने वाले ड्राफ्ट को इम्प्लीमेंट करने वाला प्रथम इंटीग्रेटेड सर्किट इंटेल 8087 था।

आईईईई 754-1985 बाइनरी में नंबर्स को रिप्रजेंटेशन करता है, जो एक्यूरेसी के चार लेवल्स की परिभाषा प्रदान करता है, जिनमें से दो सबसे अधिक उपयोग किए जाते हैं:

| लेवल | विड्थ | कम्पलीट एक्यूरेसी से रेंज करें | एक्यूरेसी[lower-alpha 1] |

|---|---|---|---|

| सिंगल एक्यूरेसी | 32 bits | ±1.18×10−38 to ±3.4×1038 | लगभग 7 दशमलव अंक |

| डबल एक्यूरेसी | 64 bits | ±2.23×10−308 to ±1.80×10308 | लगभग 16 दशमलव अंक |

स्टैण्डर्ड पॉजिटिव और नेगेटिव इनफाइनाइट के लिए रिप्रजेंटेशन को भी परिभाषित करता है, नेगेटिव शून्य, शून्य से विभाजन जैसे इनवैलिड परिणामों को सुरक्षित करने के लिए पांच एक्सेप्शन, उन एक्सेप्शन्स का रिप्रजेंटेशन करने के लिए विशेष वैल्यू जिन्हें NaN कहा जाता है, ऊपर दिखाए गए छोटी नंबर्स का रिप्रजेंटेशन करने के लिए डिनॉर्मल नंबर्स, और चार गोल मोड है।

नंबर्स का रिप्रजेंटेशन

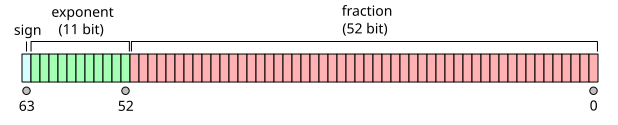

आईईईई 754 फॉर्मेट में फ़्लोटिंग-पॉइंट नंबर्स में तीन फील्ड्स होते हैं: साइन बिट, बायस्ड एक्सपोनेंट और फ्रैक्शन आदि। निम्नलिखित उदाहरण प्रत्येक का अर्थ बताता है।

दशमलव नंबर 0.1562510 बाइनरी में 0.001012 (अर्थात् 1/8 + 1/32) प्रदर्शित किया गया है। (सबस्क्रिप्ट नंबर बेस प्रदर्शित करते हैं।) साइंटिफिक नोटेशन के अनुरूप, जहां नंबर्स को दशमलव बिंदु के बाईं ओर अन्य-शून्य अंक के रूप में लिखा जाता है, हम इस नंबर को पुनः लिखते हैं जिससे कि इसमें बाइनरी बिंदु के बाईं ओर सिंगल 1 बिट होता है। हम तीन स्टेट्स द्वारा लेफ्ट किये गए बिट्स के ट्रांसफर की पूर्ति के लिए 2 की एप्रोप्रियेट पावर से मल्टीप्लाई करते हैं:

अब हम फ्रैक्शन और एक्सपोनेंट को रीड कर सकते हैं: फ्रैक्शन .012 है और एक्सपोनेंट −3 है।

जैसा कि चित्रों में प्रदर्शित किया गया है, आईईईई 754 में इस नंबर का रिप्रजेंटेशन करने वाले तीन फील्ड हैं:

- चिन्ह = 0, क्योंकि नंबर पॉजिटिव है (1 नेगेटिव प्रदर्शित करता है।)।

- बायस्ड एक्सपोनेंट = −3 + बायस है। 'सिंगल एक्यूरेसी' में, बायस '127' है, इसलिए इस उदाहरण में बायस्ड एक्सपोनेंट 124 है; 'डबल प्रिसिजन' में, बायस '1023' है, इसलिए इस उदाहरण में बायस्ड एक्सपोनेंट 1020 है।

- फ्रैक्शन = .01000…2.

आईईईई 754 एक्सपोनेंट में ऑफसेट बाइनरी जोड़ता है जिससे कि कई स्टेट्स में नंबर्स की अपेक्षा उसी हार्डवेयर द्वारा सरलता से की जा सके जो साइंड 2-कॉम्प्लीमेंट इंटिजर्स की अपेक्षा करता है। बायस्ड एक्सपोनेंट का उपयोग करते हुए, दो पॉजिटिव फ़्लोटिंग-पॉइंट नंबर्स में से छोटी नंबर चिह्न और परिमाण इंटिजर्स के समान क्रम के पश्चात बड़ी नंबर से कम निकलती है। यदि दो फ़्लोटिंग-पॉइंट नंबर्स के भिन्न-भिन्न चिह्न हैं, तो चिह्न-और-परिमाण अपेक्षा बायस्ड एक्सपोनेंट के साथ भी कार्य करती है। चूँकि, यदि दोनों बायस्ड-एक्सपोनेंट फ़्लोटिंग-पॉइंट नंबर्स नेगेटिव हैं, तो क्रम को विपरीत कर दिया जाना चाहिए। यदि एक्सपोनेंट को, वैल्यू लीजिए, 2-कम्पलीट नंबर के रूप में प्रदर्शित किया जाता है, तो यह देखने के लिए अपेक्षा करना कि दो नंबर्स में से कौन सी बड़ी है, सुविधाजनक नहीं होता है।

लीडिंग 1 बिट को ओमिटेड कर दिया गया है क्योंकि एक्सपैक्ट शून्य सभी नंबर्स लीडिंग 1 से प्रारंभ होती हैं; लीडिंग 1 इम्प्लीसिट है और वास्तव में इसे स्टोर करने की आवश्यकता नहीं है जो मुफ़्त में अतिरिक्त एक्यूरेसी प्रदान करता है।

शून्य

शून्य नंबर को विशेष रूप से प्रदर्शित किया गया है:

- पॉजिटिव शून्य के लिए चिह्न = 0, नेगेटिव शून्य के लिए 1 है।

- बायस्ड एक्सपोनेंट = 0 है।

- फ्रैक्शन = 0 है।

डिनॉर्मल नंबर्स

ऊपर वर्णित नंबर रिप्रजेंटेशन को नॉर्मेलाइज़ कहा जाता है, जिसका अर्थ है कि इम्प्लीसिट लीडिंग बाइनरी अंक 1 है। अंडरफ्लो होने पर एक्यूरेसी की हानि को कम करने के लिए, आईईईई 754 में नॉर्मेलाइज़ रिप्रजेंटेशन में संभव से छोटे अंशों का रिप्रजेंटेशन करने की क्षमता सम्मिलित है। इम्प्लीसिट लीडिंग अंक 0 बनाता है। ऐसी नंबर्स को असामान्य नंबर्स कहा जाता है। उनमें नॉर्मेलाइज़ नंबर के रूप में कई सिग्नीफिकेंट डिजिट सम्मिलित नहीं होते हैं, किन्तु जब किसी ऑपरेशन का रिजल्ट शून्य नहीं होता है, किन्तु नॉर्मेलाइज़ नंबर द्वारा प्रदर्शित किये जाने के लिए शून्य के अधिक निकट होता है, तो वे एक्यूरेसी की क्रमिक हानि को सक्षम करते हैं।

असामान्य नंबर को सभी 0 बिट्स के बायस्ड एक्सपोनेंट के साथ प्रदर्शित किया जाता है, जो सिंगल एक्यूरेसी में −126 के एक्सपोनेंट का रिप्रजेंटेशन करता है (−127 नहीं), या डबल एक्यूरेसी में −1022 (−1023 नहीं) का रिप्रजेंटेशन करता है।[3] इसके विपरीत, नार्मल नंबर का रिप्रजेंटेशन करने वाला सबसे छोटा बायस्ड एक्सपोनेंट 1 है (नीचे उदाहरण देखें)।

नॉन-नंबर्स का रिप्रजेंटेशन

किसी कैलकुलेशन की इन्फिनिटी या इनवैलिड रिजल्ट को प्रदर्शित करने के लिए बायस्ड-एक्सपोनेंट फील्ड सभी 1 बिट्स से कम्पलीट है।

पॉजिटिव और नेगेटिव इनफाइनाइट

पॉजिटिव और नेगेटिव इनफाइनाइट को इस प्रकार प्रदर्शित किया गया है:

- पॉजिटिव इनफाइनाइट के लिए चिह्न = 0, नेगेटिव इनफाइनाइट के लिए 1 है।

- बायस्ड एक्सपोनेंट = सभी 1 बिट्स है।

- फ्रैक्शन = सभी 0 बिट्स है।

NaN

फ़्लोटिंग-पॉइंट अंकगणित के कुछ ऑपरेशन इनवैलिड हैं, जैसे नेगेटिव नंबर का वर्गमूल लेता है। किसी इनवैलिड रिजल्ट तक पहुंचने की क्रिया को फ़्लोटिंग-पॉइंट अपवाद कहा जाता है। असाधारण रिजल्ट को "नॉट ए नंबर" के लिए NaN नामक विशेष कोड द्वारा प्रदर्शित किया जाता है। आईईईई 754-1985 में सभी NaN का फॉर्मेट यह है:

- चिह्न = या तो 0 या 1 होता है।

- बायस्ड एक्सपोनेंट = सभी 1 बिट्स है।

- फ्रैक्शन = सभी 0 बिट्स को त्यागकर कुछ भी होता है (क्योंकि सभी 0 बिट्स इनफाइनाइट का रिप्रजेंटेशन करते हैं)।

सीरीज और एक्यूरेसी

एक्यूरेसी को दो क्रमिक मंटिसा रिप्रजेंटेशन के मध्य न्यूनतम अंतर के रूप में परिभाषित किया गया है; इस प्रकार यह केवल मंटिसा में फंक्शन है; यद्यपि अंतर को दो क्रमिक नंबर्स के मध्य के अंतर के रूप में परिभाषित किया गया है।[4]

सिंगल-एक्यूरेसी नंबर्स 32 बिट्स पर व्याप्त हैं। सिंगल एक्यूरेसी में:

- शून्य के निकटतम पॉजिटिव और नेगेटिव नंबर्स (घातक फील्ड में सभी 0 के साथ असामान्य वैल्यू और फ्रैक्शन फील्ड में बाइनरी वैल्यू 1 द्वारा प्रदर्शित की जाती हैं) हैं:

- ±2−23×2−126 ≈ ±1.40130×10−45

- शून्य के निकटतम पॉजिटिव और नेगेटिव नॉर्मेलाइज़ नंबर्स (घातक फील्ड में बाइनरी वैल्यू 1 और फ्रैक्शन फील्ड में 0 के साथ प्रदर्शित की जाती हैं) हैं:

- ±1 × 2−126 ≈ ±1.17549×10−38

- शून्य से सबसे दूर की परिमित पॉजिटिव और परिमित नेगेटिव नंबर्स (घातक फील्ड में 254 और फ्रैक्शन फील्ड में सभी 1 के साथ वैल्यू द्वारा प्रदर्शित की गई) हैं:

- ±(2−2−23) × 2127[5] ≈ ±3.40282×1038

सिंगल एक्यूरेसी में दिए गए एक्सपोनेंट के लिए कुछ उदाहरण सीमा और अंतराल वैल्यू है:

| रियल एक्सपोनेंट (अनबायस्ड) | एक्सपोनेंट (बायस्ड) | न्यूनतम | अधिकतम | गैप |

|---|---|---|---|---|

| −1 | 126 | 0.5 | ≈ 0.999999940395 | ≈ 5.96046e-8 |

| 0 | 127 | 1 | ≈ 1.999999880791 | ≈ 1.19209e-7 |

| 1 | 128 | 2 | ≈ 3.999999761581 | ≈ 2.38419e-7 |

| 2 | 129 | 4 | ≈ 7.999999523163 | ≈ 4.76837e-7 |

| 10 | 137 | 1024 | ≈ 2047.999877930 | ≈ 1.22070e-4 |

| 11 | 138 | 2048 | ≈ 4095.999755859 | ≈ 2.44141e-4 |

| 23 | 150 | 8388608 | 16777215 | 1 |

| 24 | 151 | 16777216 | 33554430 | 2 |

| 127 | 254 | ≈ 1.70141e38 | ≈ 3.40282e38 | ≈ 2.02824e31 |

उदाहरण के लिए, 16,777,217 को 32-बिट फ़्लोट के रूप में एन्कोड नहीं किया जा सकता क्योंकि इसे 16,777,216 पर रौंडिंग किया जाएगा। इससे ज्ञात होता है कि फ़्लोटिंग पॉइंट अंकगणित लेखांकन सॉफ़्टवेयर के लिए अनुपयुक्त क्यों है। चूँकि, रिप्रजेंटेशन योग्य सीमा के अंदर सभी इंटिजर्स जो 2 की पावर हैं, उन्हें बिना गोलाई के 32-बिट फ़्लोट में स्टोर किया जा सकता है।

डबल एक्यूरेसी

डबल-एक्यूरेसी नंबर्स 64 बिट्स पर व्याप्त हैं। डबल एक्यूरेसी में:

- शून्य के निकटतम पॉजिटिव और नेगेटिव नंबर्स (एक्सप फील्ड में सभी 0 के साथ असामान्य वैल्यू और फ्रैक्शन फील्ड में बाइनरी वैल्यू 1 द्वारा प्रदर्शित की जाती हैं) हैं

- ±2−52×2−1022 ≈ ±4.94066×10−324

- शून्य के निकटतम पॉजिटिव और नेगेटिव नॉर्मेलाइज़ नंबर्स (एक्सप फील्ड में बाइनरी वैल्यू 1 और फ्रैक्शन फील्ड में 0 के साथ प्रदर्शित की जाती हैं) हैं:

- ±1 × 2−1022 ≈ ±2.22507×10−308

- शून्य से सबसे दूर की परिमित पॉजिटिव और परिमित नेगेटिव नंबर्स (एक्सप फील्ड में 2046 और फ्रैक्शन फील्ड में सभी 1 के साथ वैल्यू द्वारा प्रदर्शित की गई) हैं:

- ±(2−2−52)×21023[5]≈ ±1.79769×10308

डबल एक्यूरेसी में दिए गए एक्सपोनेंट के लिए कुछ उदाहरण रेंज और गैप वैल्यू है:

| रियल एक्सपोनेंट (अनबायस्ड) | एक्सपोनेंट (बायस्ड) | न्यूनतम | अधिकतम | गैप |

|---|---|---|---|---|

| −1 | 1022 | 0.5 | ≈ 0.999999999999999888978 | ≈ 1.11022e-16 |

| 0 | 1023 | 1 | ≈ 1.999999999999999777955 | ≈ 2.22045e-16 |

| 1 | 1024 | 2 | ≈ 3.999999999999999555911 | ≈ 4.44089e-16 |

| 2 | 1025 | 4 | ≈ 7.999999999999999111822 | ≈ 8.88178e-16 |

| 10 | 1033 | 1024 | ≈ 2047.999999999999772626 | ≈ 2.27374e-13 |

| 11 | 1034 | 2048 | ≈ 4095.999999999999545253 | ≈ 4.54747e-13 |

| 52 | 1075 | 4503599627370496 | 9007199254740991 | 1 |

| 53 | 1076 | 9007199254740992 | 18014398509481982 | 2 |

| 1023 | 2046 | ≈ 8.98847e307 | ≈ 1.79769e308 | ≈ 1.99584e292 |

एक्सटेंडेड फॉर्मेट

स्टैण्डर्ड राउंड-ऑफ एरर को कम करने के लिए, अंतिम रिजल्ट के लिए आवश्यक उच्च एक्यूरेसी पर आंतरिक कैलकुलेशन करने के लिए एक्सटेंडेड फॉर्मेट का उपयोग करने का अनुरोध करता है: स्टैण्डर्ड केवल ऐसे प्रारूपों के लिए न्यूनतम एक्यूरेसी और एक्सपोनेंट आवश्यकताओं को निर्दिष्ट करता है। x87 80-बिट एक्सटेंडेड फॉर्मेट सबसे अधिक कार्यान्वित एक्सटेंडेड फॉर्मेट है जो इन आवश्यकताओं को कम्पलीट करता है।

उदाहरण

यहां सिंगल-एक्यूरेसी आईईईई 754 रिप्रजेंटेशन के कुछ उदाहरण दिए गए हैं:

| प्रकार | चिह्न | रियल एक्सपोनेंट | एक्सपोनेंट (बायस्ड) | एक्सपोनेंट फील्ड | फ्रैक्शन फील्ड | वैल्यू |

|---|---|---|---|---|---|---|

| शून्य | 0 | −126 | 0 | 0000 0000 | 000 0000 0000 0000 0000 0000 | 0.0 |

| नेगेटिव शून्य | 1 | −126 | 0 | 0000 0000 | 000 0000 0000 0000 0000 0000 | −0.0 |

| एक | 0 | 0 | 127 | 0111 1111 | 000 0000 0000 0000 0000 0000 | 1.0 |

| शून्य से एक कम | 1 | 0 | 127 | 0111 1111 | 000 0000 0000 0000 0000 0000 | −1.0 |

| सबसे छोटी असामान्यीकृत नंबर | * | −126 | 0 | 0000 0000 | 000 0000 0000 0000 0000 0001 | ±2−23 × 2−126 = ±2−149 ≈ ±1.4×10−45 |

| "मध्य" असामान्यीकृत नंबर | * | −126 | 0 | 0000 0000 | 100 0000 0000 0000 0000 0000 | ±2−1 × 2−126 = ±2−127 ≈ ±5.88×10−39 |

| सबसे बड़ी असामान्यीकृत नंबर | * | −126 | 0 | 0000 0000 | 111 1111 1111 1111 1111 1111 | ±(1−2−23) × 2−126 ≈ ±1.18×10−38 |

| सबसे छोटी नॉर्मेलाइज़ नंबर | * | −126 | 1 | 0000 0001 | 000 0000 0000 0000 0000 0000 | ±2−126 ≈ ±1.18×10−38 |

| सबसे बड़ी नॉर्मेलाइज़ नंबर | * | 127 | 254 | 1111 1110 | 111 1111 1111 1111 1111 1111 | ±(2−2−23) × 2127 ≈ ±3.4×1038 |

| पॉजिटिव अनन्तता | 0 | 128 | 255 | 1111 1111 | 000 0000 0000 0000 0000 0000 | +∞ |

| नेगेटिव अनन्तता | 1 | 128 | 255 | 1111 1111 | 000 0000 0000 0000 0000 0000 | −∞ |

| कोई नंबर नहीं | * | 128 | 255 | 1111 1111 | नॉन शून्य | NaN |

| * साइन बिट 0 या 1 हो सकता है। | ||||||

फ़्लोटिंग-पॉइंट नंबर्स को कम्पेयर करना

नेगेटिव शून्य और पॉजिटिव शून्य के लिए बिट्स के दो कॉम्बिनेशन को एक्सपैक्ट करके, प्रत्येक बिट कॉम्बिनेशन या तो NaN है या संबद्ध क्रम के साथ एफ़िनली एक्सटेंडेड रियल नंबर सिस्टम में अद्वितीय वैल्यू वाला नंबर है, जिस पर कभी-कभी विशेष ध्यान देने की आवश्यकता होती है (नीचे देखें)। बाइनरी रिप्रजेंटेशन में विशेष गुण होता है कि, NaN को एक्सपैक्ट करके, किसी भी दो नंबर्स की अपेक्षा चिह्न और परिमाण इंटिजर्स के रूप में की जा सकती है (एंडियननेस उद्देश्य इम्प्लीमेंट होते हैं)। 2 के पूरक पूर्णांकों के रूप में अपेक्षा करते समय: यदि साइन बिट फ्रैक्शन होते हैं, तो नेगेटिव नंबर पॉजिटिव नंबर से पूर्व होती है, इसलिए 2 का पूरक सही रिजल्ट देता है (इसके अतिरिक्त कि नेगेटिव शून्य और पॉजिटिव शून्य को समान माना जाना चाहिए)। यदि दोनों वैल्यू पॉजिटिव हैं, तो 2 की पूरक अपेक्षा पुनः एप्रोप्रियेट रिजल्ट देती है। अन्यथा (दो नेगेटिव नंबर्स), एप्रोप्रियेट एफपी क्रम 2 के पूरक क्रम के विपरीत है।

फ़्लोटिंग पॉइंट गणनाओं में निहित राउंडिंग एरर परिणामों की एक्यूरेसी समानता के परीक्षण के लिए अपेक्षाओं के उपयोग को सीमित कर सकती हैं। एक्सेप्टिंग लिमिट का चयन करना कम्प्लेक्सिटी विषय है। सामान्य टेक्नोलॉजी अनुमानित अपेक्षा करने के लिए अपेक्षात्मक ईपीएसलॉन वैल्यू का उपयोग करना है।[6] अपेक्षाएँ कितनी उदार हैं, इस पर निर्भर करते हुए, सामान्य मूल्यों में सिंगल-एक्यूरेसी के लिए 1e-6 या 1e-5और डबल एक्यूरेसी के लिए 1e-14 सम्मिलित हैं।[7][8] अन्य सामान्य तकनीक यूएलपी है, जो यह परीक्षण करती है कि अंतिम स्थान के अंकों में क्या अंतर है, प्रभावी रूप से यह परीक्षण करती है कि दोनों वैल्यू कितने दूर हैं।[9]

चूँकि अपेक्षात्मक उद्देश्यों के लिए नेगेटिव शून्य और पॉजिटिव शून्य को सामान्यतः समान माना जाता है, कुछ प्रोग्रामिंग लैंग्वेज रिलेशनल ऑपरेटर और समान निर्माण उन्हें फ्रैक्शन मानते हैं। जावा लैंग्वेज विशिष्टता के अनुसार,[10] अपेक्षा और समानता संचालक उन्हें समान मानते हैं, किन्तु Math.min() और Math.max() उन्हें फ्रैक्शन करते हैं (सामान्यतः जावा संस्करण 1.1 से प्रारंभ करते हैं किन्तु वास्तव में 1.1.1 के साथ), जैसा कि अपेक्षा विधियां Float और Double कक्षाओं का equals(), compareTo() और यहां तक कि compare() भी हैं।

फ़्लोटिंग-पॉइंट नंबर्स को रौंडिंग करना

आईईईई स्टैण्डर्ड में चार भिन्न-भिन्न राउंडिंग मोड हैं; प्रथम डिफ़ॉल्ट है; अन्य को निर्देशित गोलाई कहा जाता है।

- 'राउंड टू नियरेस्ट' - निकटतम वैल्यू तक राउंड; यदि नंबर मध्य में गिरती है तो इसे सम (शून्य) कम से कम महत्वपूर्ण बिट के साथ निकटतम वैल्यू तक रौंडिंग किया जाता है, जिसका अर्थ है कि इसे 50% समय तक रौंडिंग किया जाता है (आईईईई 754-2008 में इस मोड को दूसरे से अलग करने के लिए राउंडटीज़टूईवन कहा जाता है) -से-निकटतम मोड)।

- 'राउंड टुवर्ड 0' - शून्य की ओर निर्देशित गोलाई।

- 'राउंड टुवर्ड +∞' - पॉजिटिव इनफाइनाइट की ओर निर्देशित गोलाई।

- 'राउंड टुवर्ड -∞' - नेगेटिव इनफाइनाइट की ओर निर्देशित गोलाई।

रियल नंबर्स का विस्तार

आईईईई स्टैण्डर्ड भिन्न-भिन्न पॉजिटिव और नेगेटिव इन्फिनिटी के साथ, कम्पलीट रूप से एक्सटेंडेड रियल नंबर सिस्टमको नियोजित (और एक्सटेंडेड) करता है। प्रारूपण के समय, प्रोग्रामर को मोड चयन विकल्प प्रदान करके, सिंगल अहस्ताक्षरित इनफाइनाइट के साथ प्रोजेक्टिवली एक्सटेंडेड रियल नंबर सिस्टमको सम्मिलित करने के लिए स्टैण्डर्ड का प्रस्ताव था। चूँकि, अंतिम स्टैण्डर्ड की कम्प्लेक्सिटी को कम करने के हित में, प्रोजेक्टिव मोड को विस्थापित कर दिया गया था। इंटेल 8087 और इंटेल 80287 फ़्लोटिंग पॉइंट सह-प्रोसेसर दोनों इस प्रोजेक्टिव मोड का समर्थन करते हैं।[11][12][13]

फंक्शन्स और प्रेडिकेट्स

स्टैण्डर्ड ऑपरेशन

निम्नलिखित कार्य प्रदान किए जाने चाहिए:

- जोड़ें, घटाएं, मल्टीप्लाई करें, भाग करें।

- वर्गमूल

- फ़्लोटिंग पॉइंट शेष यह सामान्य मॉड्यूलो ऑपरेशन के जैसे नहीं है, यह दो पॉजिटिव नंबर्स के लिए नेगेटिव हो सकता है। यह x–(round(x/y)·y) का एक्यूरेसी वैल्यू प्रदान करता है।

- निकटतम इंटिजर्स तक पूर्णांकन अप्रत्यक्ष पूर्णांकन के लिए जब दो पूर्णांकों के मध्य आधा हो तो सम इंटिजर्स चयन किया जाता है।

- अपेक्षा ऑपरेशन. अधिक स्पष्ट परिणामों के अतिरिक्त, आईईईई 754 परिभाषित करता है कि −∞ = −∞, +∞ = +∞ और x ≠

NaNकिसी भी x के लिए (सहित)NaN) होता है।

रिकमांडेड फंक्शन्स और प्रेडिकेट्स

copysign(x,y)y के चिह्न के साथ x प्रदान करता है, इसलिएabs(x)copysign(x,1.0)के समान होती है। यह उन कुछ ऑपरेशनों में से है जो अंकगणित के समान NaN पर संचालित होता है। फ़ंक्शनcopysignC99 स्टैण्डर्ड में नया है।- −x, विपरीत चिह्न के साथ x प्रदान करता है। यह कुछ स्टेट्स में 0−x से फ्रैक्शन है, विशेष रूप से जब x 0 है। तो −(0) −0 है, किन्तु 0−0 का चिह्न पूर्णांकन मोड पर निर्भर करता है।

scalb(y, N)logb(x)finite(x)x के लिए प्रेडीकेट परिमित वैल्यू है, जो −Inf < x < Inf के समान है।isnan(x)x के लिए प्रेडीकेट NaN है, जो x ≠ x के समान है।x <> y, जिसका व्यवहार NaN के कारण NOT(x = y) से फ्रैक्शन होता है।unordered(x, y)सत्य है जब x, y के साथ अव्यवस्थित है, अर्थात, x या y NaN है।class(x)nextafter(x,y)x से y की दिशा में अगला रिप्रजेंटेशन योग्य वैल्यू प्रदान करता है।

इतिहास

1976 में, इंटेल फ्लोटिंग-पॉइंट कोप्रोसेसर का विकास प्रारंभ कर रहा था।[14][15] इंटेल को अपेक्षा थी कि वह वाइड रूप से फ्रैक्शन गणित सॉफ्टवेयर लाइब्रेरी में पाए जाने वाले सभी ऑपरेशन के उत्तम इम्प्लिमेंटेशन वाली चिप विक्रय में सक्षम होगी।[14][16]

जॉन पामर, जिन्होंने इस परियोजना का प्रबंधन किया था, इनका मानना था कि इस प्रयास को भिन्न-भिन्न प्रोसेसरों में स्टैण्डर्ड इंटीग्रेटेड फ़्लोटिंग पॉइंट ऑपरेशन द्वारा समर्थित किया जाना चाहिए। उन्होंने कैलिफोर्निया विश्वविद्यालय के विलियम काहन से संपर्क किया, जिन्होंनेहेवलेट पैकर्ड के कैलकुलेटर की एक्यूरेसी में सुधार करने में सहायता की थी। काहन ने सुझाव दिया कि इंटेल डिजिटल इक्विपमेंट कॉर्पोरेशन (डीईसी) वैक्स के फ्लोटिंग पॉइंट का उपयोग करता है। प्रथम वैक्स, वैक्स-11/780 1977 के अंत में सामने आया था, और इसके फ्लोटिंग पॉइंट को अत्यधिक महत्व दिया गया था। चूँकि, अपनी चिप को वाइड मार्केट में विक्रय के लिए, इंटेल सर्वोत्तम फ़्लोटिंग पॉइंट चाहता था, और काहन ने विशिष्टताओं को प्रस्तुत किया था।[14] काहन ने प्रारंभ में अनुरोध किया था कि फ़्लोटिंग पॉइंट बेस दशमलव हो[17] किन्तु कोप्रोसेसर का हार्डवेयर डिज़ाइन उस परिवर्तन को करने के लिए अधिक दूर था।

इंटेल के इंटरनल प्रोसेस ने अन्य विक्रेताओं को चिंतित कर दिया, जिन्होंने समान संयोग सुनिश्चित करने के लिए मानकीकरण प्रयास स्थापित किया था। काहन ने नवंबर 1977 में आयोजित दूसरी आईईईई 754 स्टैण्डर्ड प्रोसेस समूह की बैठक में भाग लिया था। अंत में उन्हें इंटेल से उनके कोप्रोसेसर के लिए उनके कार्य के आधार पर ड्राफ्ट प्रस्ताव प्रस्तुत करने की अनुमति प्राप्त हुई; उन्हें फॉर्मेट के विवरण और उसके औचित्य को समझाने की अनुमति प्रदान की गई थी, किन्तु इंटेल के प्रोसेस आर्किटेक्चर से संबंधित कुछ भी नहीं था। ड्राफ्ट जेरोम कूनन और हेरोल्ड स्टोन के साथ सह-लिखित था, और प्रारंभ में इसे काहन-कूनन-स्टोन प्रस्ताव या के-सी-एस फॉर्मेट के रूप में जाना जाता था।[14][15][16][18]

चूंकि 8-बिट एक्सपोनेंट डबल-एक्यूरेसी नंबर्स के लिए वांछित कुछ ऑपरेशन के लिए पर्याप्त नहीं था, उदाहरण के लिए दो 32-बिट नंबर्स के प्रोडक्ट को स्टोर करने के लिए,[19] काहन के प्रस्ताव और डीईसी के प्रति-प्रस्ताव दोनों में 11 बिट्स का उपयोग किया गया था, जैसे कि 1965 से सीडीसी 6600 के टाइम टेस्टेड 60-बिट फ़्लोटिंग-पॉइंट फॉर्मेट था।[15][18][20] काहन के प्रस्ताव में अनन्तताओं का भी प्रावधान किया गया है, जो विभाजन-दर-शून्य स्टेट्स के निवारण में उपयोगी होते हैं; नॉट-ए-नंबर वैल्यू, जो इनवैलिड ऑपरेशन के निवारण में उपयोगी होते हैं; डिनॉर्मल नंबर्स, जो अंडरफ्लो के कारण होने वाली प्रॉब्लम्स को कम करने में सहायता करती हैं;[18][21][22] और उत्तम संतुलित एक्सपोनेंट बायस, जो किसी नंबर का रेसीपोकल लेते टाइम ओवरफ्लो और अंडरफ्लो से विक्रय में सहायता कर सकता है।[23][24]

अनुमोदित होने से पूर्व ही, ड्राफ्ट स्टैण्डर्ड को कई मैनुफैक्चर द्वारा इम्प्लीमेंट किया गया था।[25][26] इंटेल 8087, जिसे 1980 में घोषित किया गया था, जो ड्राफ्ट स्टैण्डर्ड को इम्प्लीमेंट करने वाली प्रथम चिप थी।

1980 में, इंटेल 8087 चिप पहले ही इम्प्लीमेंट हो चुकी थी,[27] किन्तु प्रदर्शन संबंधी चिंताओं के कारण डीईसी विशेष रूप से असामान्य नंबर्स का विरोध करता रहा और चूंकि इससे डीईसी को डीईसी के फॉर्मेट पर मानकीकरण करने के लिए प्रतिस्पर्धात्मक लाभ मिलता है।

क्रमिक अंडरफ़्लो पर विचार 1981 तक चला जब इसका आकलन करने के लिए डीईसी द्वारा नियुक्त विशेषज्ञ ने असंतुष्टों का पक्ष लिया था। डीईसी ने यह प्रदर्शित करने के लिए अध्ययन करवाया था कि क्रमिक अंडरफ़्लो बुरा विचार था, किन्तु अध्ययन का निष्कर्ष विपरीत था, और डीईसी ने हार वैल्यू ली थी। 1985 में, स्टैण्डर्ड की पुष्टि की गई थी, किन्तु यह एक वर्ष पूर्व ही रियल स्टैण्डर्ड बन गया था, जिसे कई मैनुफैक्चर द्वारा कार्यान्वित किया गया था।[15][18][5]

यह भी देखें

- आईईईई 754

- आईईईई 754 फ़्लोटिंग पॉइंट नंबर्स के गुणों के सरल उदाहरणों के लिए मिनीफ्लोट

- निश्चित-बिंदु अंकगणित

टिप्पणियाँ

- ↑ Precision: The number of decimal digits precision is calculated via number_of_mantissa_bits * Log10(2). Thus ~7.2 and ~15.9 for single and double precision respectively.

संदर्भ

- ↑ बाइनरी फ़्लोटिंग-पॉइंट अंकगणित के लिए आईईईई मानक. 1985. doi:10.1109/IEEESTD.1985.82928. ISBN 0-7381-1165-1.

- ↑ "ANSI/IEEE Std 754-2019". 754r.ucbtest.org. Retrieved 2019-08-06.

- ↑ Hennessy (2009). कंप्यूटर संगठन और डिज़ाइन. Morgan Kaufmann. p. 270. ISBN 9780123744937.

- ↑ Hossam A. H. Fahmy; Shlomo Waser; Michael J. Flynn, Computer Arithmetic (PDF), archived from the original (PDF) on 2010-10-08, retrieved 2011-01-02

- ↑ 5.0 5.1 5.2 William Kahan (October 1, 1997). "Lecture Notes on the Status of IEEE 754" (PDF). University of California, Berkeley. Retrieved 2007-04-12.

{{cite journal}}: Cite journal requires|journal=(help) - ↑ "Godot math_funcs.h". GitHub.com. 30 July 2022.

- ↑ "Godot math_defs.h". GitHub.com. 30 July 2022.

- ↑ "गोडोट MathfEx.cs". GitHub.com.

- ↑ "Comparing Floating Point Numbers, 2012 Edition". randomascii.wordpress.com. 26 February 2012.

- ↑ "जावा भाषा और वर्चुअल मशीन विशिष्टताएँ". Java Documentation.

- ↑ John R. Hauser (March 1996). "संख्यात्मक कार्यक्रमों में फ़्लोटिंग-पॉइंट अपवादों को संभालना" (PDF). ACM Transactions on Programming Languages and Systems. 18 (2): 139–174. doi:10.1145/227699.227701. S2CID 9820157.

- ↑ David Stevenson (March 1981). "IEEE Task P754: A proposed standard for binary floating-point arithmetic". IEEE Computer. 14 (3): 51–62. doi:10.1109/C-M.1981.220377. S2CID 15523399.

- ↑ William Kahan and John Palmer (1979). "प्रस्तावित फ़्लोटिंग-पॉइंट मानक पर". SIGNUM Newsletter. 14 (Special): 13–21. doi:10.1145/1057520.1057522. S2CID 16981715.

- ↑ 14.0 14.1 14.2 14.3 "Intel and Floating-Point - Updating One of the Industry's Most Successful Standards - The Technology Vision for the Floating-Point Standard" (PDF). Intel. 2016. Archived from the original (PDF) on 2016-03-04. Retrieved 2016-05-30. (11 pages)

- ↑ 15.0 15.1 15.2 15.3 "An Interview with the Old Man of Floating-Point". cs.berkeley.edu. 1998-02-20. Retrieved 2016-05-30.

- ↑ 16.0 16.1 Woehr, Jack, ed. (1997-11-01). "A Conversation with William Kahan". Dr. Dobb's. drdobbs.com. Retrieved 2016-05-30.

- ↑ W. Kahan 2003, pers. comm. to Mike Cowlishaw and others after an IEEE 754 meeting

- ↑ 18.0 18.1 18.2 18.3 "IEEE 754: An Interview with William Kahan" (PDF). dr-chuck.com. Retrieved 2016-06-02.

- ↑ "IEEE vs. Microsoft Binary Format; Rounding Issues (Complete)". Microsoft Support. Microsoft. 2006-11-21. Article ID KB35826, Q35826. Archived from the original on 2020-08-28. Retrieved 2010-02-24.

- ↑ Thornton, James E. (1970). Written at Advanced Design Laboratory, Control Data Corporation. Design of a Computer: The Control Data 6600 (PDF) (1 ed.). Glenview, Illinois, USA: Scott, Foresman and Company. LCCN 74-96462. Archived (PDF) from the original on 2020-08-28. Retrieved 2016-06-02. (1+13+181+2+2 pages)

- ↑ Kahan, William Morton. "Why do we need a floating-point arithmetic standard?" (PDF). cs.berkeley.edu. Retrieved 2016-06-02.

- ↑ Kahan, William Morton; Darcy, Joseph D. "How Java's Floating-Point Hurts Everyone Everywhere" (PDF). cs.berkeley.edu. Retrieved 2016-06-02.

- ↑ Turner, Peter R. (2013-12-21). Numerical Analysis and Parallel Processing: Lectures given at The Lancaster …. Springer. ISBN 978-3-66239812-8. Retrieved 2016-05-30.

- ↑ "Names for Standardized Floating-Point Formats" (PDF). cs.berkeley.edu. Retrieved 2016-06-02.

- ↑ Charles Severance (20 February 1998). "फ़्लोटिंग-प्वाइंट के बूढ़े आदमी के साथ एक साक्षात्कार".

- ↑ Charles Severance. "आईईईई फ़्लोटिंग-पॉइंट प्रारूप का इतिहास". Connexions. Archived from the original on 2009-11-20.

- ↑ "Molecular Expressions: Science, Optics & You - Olympus MIC-D: Integrated Circuit Gallery - Intel 8087 Math Coprocessor". micro.magnet.fsu.edu. Retrieved 2016-05-30.

अग्रिम पठन

- Charles Severance (March 1998). "IEEE 754: An Interview with William Kahan" (PDF). IEEE Computer. 31 (3): 114–115. doi:10.1109/MC.1998.660194. S2CID 33291145. Archived from the original (PDF) on 2009-08-23. Retrieved 2008-04-28.

- David Goldberg (March 1991). "What Every Computer Scientist Should Know About Floating-Point Arithmetic" (PDF). ACM Computing Surveys. 23 (1): 5–48. doi:10.1145/103162.103163. S2CID 222008826. Retrieved 2008-04-28.

- Chris Hecker (February 1996). "Let's Get To The (Floating) Point" (PDF). Game Developer Magazine: 19–24. ISSN 1073-922X. Archived from the original (PDF) on 2007-02-03.

- David Monniaux (May 2008). "The pitfalls of verifying floating-point computations". ACM Transactions on Programming Languages and Systems. 30 (3): 1–41. arXiv:cs/0701192. doi:10.1145/1353445.1353446. ISSN 0164-0925. S2CID 218578808.: A compendium of non-intuitive behaviours of floating-point on popular architectures, with implications for program verification and testing.