त्रि अवस्था तर्क: Difference between revisions

No edit summary |

No edit summary |

||

| Line 1: | Line 1: | ||

{{Short description|Buffer in digital electronics}} | {{Short description|Buffer in digital electronics}} | ||

{{Redir|3- | {{Redir|3-अवस्था |डिस्केट नियंत्रक प्रारूप|3 मोड}} | ||

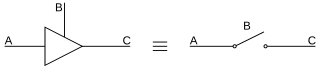

त्रि- | डिजिटल इलेक्ट्रॉनिक्स में, त्रि-अवस्था या तीन-अवस्था बफर प्रकार का डिजिटल बफर है जिसमें तीन स्थिर अवस्थाएँ होती हैं: उच्च आउटपुट अवस्था, निम्न आउटपुट अवस्था और उच्च-प्रतिबाधा अवस्था। उच्च-प्रतिबाधा अवस्था में, बफर का आउटपुट आउटपुट बस से डिस्कनेक्ट हो जाता है, जिससे अन्य डिवाइस त्रि-अवस्था बफर से हस्तक्षेप के बिना बस को चला सकते हैं। यह उन स्थितियों में उपयोगी हो सकता है जहां ही बस से कई डिवाइस जुड़े हुए हैं और इसे बारी-बारी से एक्सेस करने की आवश्यकता है। अपनी बस में तीन-अवस्था तर्क को लागू करने वाली प्रणाली को तीन-अवस्था बस या त्रि-अवस्था बस के रूप में जाना जाता है। | ||

गेट्स, फ्लिप-फ्लॉप, या अन्य डिजिटल लॉजिक | त्रि-अवस्था बफ़र्स सामान्यतः बस-आधारित सिस्टम में उपयोग किए जाते हैं, जहां कई डिवाइस ही बस से जुड़े होते हैं और इसे साझा करने की आवश्यकता होती है। उदाहरण के लिए, कंप्यूटर सिस्टम में, कई डिवाइस जैसे कि सीपीयू, मेमोरी और पेरिफेरल्स ही डेटा बस से जुड़े हो सकते हैं। यह सुनिश्चित करने के लिए कि समय में केवल डिवाइस बस में डेटा संचारित कर सकता है, प्रत्येक डिवाइस त्रि-अवस्था बफर से लैस है। जब कोई उपकरण डेटा संचारित करना चाहता है, तो वह अपने त्रि-अवस्था बफर को सक्रिय करता है, जो इसके आउटपुट को बस से जोड़ता है और इसे डेटा संचारित करने की अनुमति देता है। जब ट्रांसमिशन पूरा हो जाता है, तो डिवाइस अपने त्रि-अवस्था बफर को निष्क्रिय कर देता है, जो इसके आउटपुट को बस से डिस्कनेक्ट कर देता है और किसी अन्य डिवाइस को बस तक पहुंचने की अनुमति देता है। | ||

गेट्स, फ्लिप-फ्लॉप, या अन्य डिजिटल लॉजिक परिपथ का उपयोग करके त्रि-अवस्था बफ़र्स को लागू किया जा सकता है। वे बस में क्रॉसस्टॉक और शोर को अल्प करने के लिए उपयोगी होते हैं, और कई उपकरणों को बिना किसी हस्तक्षेप के ही बस को साझा करने की अनुमति देते हैं। | |||

{| class="wikitable" align=right style=text-align:center | {| class="wikitable" align=right style=text-align:center | ||

!colspan=2| <big>INPUT</big>|| <big>OUTPUT</big> | !colspan=2| <big>INPUT</big>|| <big>OUTPUT</big> | ||

| Line 23: | Line 24: | ||

== उपयोग == | == उपयोग == | ||

तीसरे | तीसरे अवस्था की मूल अवधारणा, उच्च प्रतिबाधा (हाय-जेड), बाकी परिपथ से डिवाइस के प्रभाव को प्रभावी ढंग से हटाना है। यदि से अधिक डिवाइस विद्युत रूप से किसी अन्य डिवाइस से जुड़े हैं, तो आउटपुट को हाई-जेड स्थिति में डालने का उपयोग प्रायः शॉर्ट परिपथ को रोकने के लिए किया जाता है, या डिवाइस उच्च ड्राइविंग (तार्किक 1) दूसरे डिवाइस के खिलाफ अल्प ड्राइविंग (तार्किक 0) करता है। | ||

कुशल [[ बहुसंकेतक |बहुसंकेतक]] ्स को लागू करने के लिए तीन- | कुशल [[ बहुसंकेतक |बहुसंकेतक]] ्स को लागू करने के लिए तीन-अवस्था बफ़र्स का भी उपयोग किया जा सकता है, विशेष रूप से बड़ी संख्या में इनपुट वाले।<ref>{{cite book |title=इलेक्ट्रॉनिक्स की कला|first=Winfield |last=Hill |first2=Paul |last2=Horowitz |publisher=Cambridge University Press |year =1989 |isbn=0-521-37095-7 |url=https://books.google.com/books?id=bkOMDgwFA28C |pages=495–497}}</ref> | ||

साझा [[बस (कंप्यूटिंग)]] के संचालन के लिए तीन- | साझा [[बस (कंप्यूटिंग)]] के संचालन के लिए तीन-अवस्था बफर आवश्यक हैं। | ||

तीन- | तीन-अवस्था तर्क एल ई डी (त्रि-अवस्था बहुसंकेतन या [[ Charlieplexing |Charlieplexing]] ) के सेट को चलाने के लिए आवश्यक तारों की संख्या को अल्प कर सकता है। | ||

== आउटपुट सक्षम बनाम चिप चयन == | == आउटपुट सक्षम बनाम चिप चयन == | ||

बस से कनेक्ट करने के लिए डिज़ाइन किए गए कई मेमोरी डिवाइस (जैसे RAM और ROM चिप) में दोनों होते हैं {{overline|CS}} ([[चिप का चयन]] करें) और {{overline|OE}} (आउटपुट इनेबल) पिन, जो सतही तौर पर ही काम करते दिखते हैं। | बस से कनेक्ट करने के लिए डिज़ाइन किए गए कई मेमोरी डिवाइस (जैसे RAM और ROM चिप) में दोनों होते हैं {{overline|CS}} ([[चिप का चयन]] करें) और {{overline|OE}} (आउटपुट इनेबल) पिन, जो सतही तौर पर ही काम करते दिखते हैं। यदि {{overline|CS}} का दावा नहीं किया गया है, आउटपुट उच्च प्रतिबाधा हैं। | ||

अंतर सिग्नल को आउटपुट करने के लिए आवश्यक समय में निहित है। जब चिप का चयन निष्क्रिय हो जाता है, तो चिप आंतरिक रूप से संचालित नहीं होती है, और पता प्रदान करने और डेटा प्राप्त करने के बीच महत्वपूर्ण विलंब होगा। (निश्चित रूप से फायदा यह है कि इस मामले में चिप न्यूनतम बिजली की खपत करती है।) | अंतर सिग्नल को आउटपुट करने के लिए आवश्यक समय में निहित है। जब चिप का चयन निष्क्रिय हो जाता है, तो चिप आंतरिक रूप से संचालित नहीं होती है, और पता प्रदान करने और डेटा प्राप्त करने के बीच महत्वपूर्ण विलंब होगा। (निश्चित रूप से फायदा यह है कि इस मामले में चिप न्यूनतम बिजली की खपत करती है।) | ||

जब चिप चयन पर जोर दिया जाता है, तो चिप आंतरिक रूप से एक्सेस करता है, और आउटपुट सक्षम करने से केवल अंतिम आउटपुट ड्राइवर अक्षम होते हैं। यह तब किया जा सकता है जब बस अन्य उद्देश्यों के लिए उपयोग में हो, और जब आउटपुट सक्षम अंत में जोर दिया जाता है, तो डेटा न्यूनतम विलंब के साथ दिखाई देगा। आउटपुट इनेबल लाइन के साथ ROM या स्टेटिक रैम चिप | जब चिप चयन पर जोर दिया जाता है, तो चिप आंतरिक रूप से एक्सेस करता है, और आउटपुट सक्षम करने से केवल अंतिम आउटपुट ड्राइवर अक्षम होते हैं। यह तब किया जा सकता है जब बस अन्य उद्देश्यों के लिए उपयोग में हो, और जब आउटपुट सक्षम अंत में जोर दिया जाता है, तो डेटा न्यूनतम विलंब के साथ दिखाई देगा। आउटपुट इनेबल लाइन के साथ ROM या स्टेटिक रैम चिप सामान्यतः दो एक्सेस टाइम को सूचीबद्ध करेगा: चिप सेलेक्ट ऐसर्ड और एड्रेस वैलिड से, और दूसरा, अल्प समय की प्रारंभ जब आउटपुट इनेबल होता है। | ||

== पुल-अप और पुल-डाउन का प्रयोग == | == पुल-अप और पुल-डाउन का प्रयोग == | ||

जब आउटपुट त्रि-कहा जाता है (हाय-जेड स्थिति में) बाकी | जब आउटपुट त्रि-कहा जाता है (हाय-जेड स्थिति में) बाकी परिपथ पर उनका प्रभाव हटा दिया जाता है, और परिपथ नोड फ्लोटिंग होगा यदि कोई अन्य परिपथ तत्व इसकी स्थिति निर्धारित नहीं करता है। परिपथ डिजाइनर प्रायः परिपथ को प्रभावित करने के लिए [[पुल-अप रोकनेवाला]] | पुल-अप या पुल-डाउन रेसिस्टर्स (सामान्यतः 1–100 kΩ की सीमा के भीतर) का उपयोग करते हैं, जब आउटपुट त्रि-कहा जाता है। | ||

[[पीसीआई स्थानीय बस]] पुल-अप प्रतिरोधक प्रदान करती है, लेकिन बस की बड़ी वितरित क्षमता को देखते हुए सिग्नल को उच्च खींचने के लिए उन्हें कई घड़ी चक्रों की आवश्यकता होगी। हाई-स्पीड ऑपरेशन को सक्षम करने के लिए, प्रोटोकॉल की आवश्यकता होती है कि हाई-जेड स्थिति में जाने से पहले | [[पीसीआई स्थानीय बस]] पुल-अप प्रतिरोधक प्रदान करती है, लेकिन बस की बड़ी वितरित क्षमता को देखते हुए सिग्नल को उच्च खींचने के लिए उन्हें कई घड़ी चक्रों की आवश्यकता होगी। हाई-स्पीड ऑपरेशन को सक्षम करने के लिए, प्रोटोकॉल की आवश्यकता होती है कि हाई-जेड स्थिति में जाने से पहले अल्प से अल्प घड़ी चक्र के लिए बस ड्राइव से कनेक्ट होने वाला प्रत्येक उपकरण महत्वपूर्ण नियंत्रण संकेतों को उच्च करता है। इस तरह, पुल-अप प्रतिरोध केवल [[रिसाव (इलेक्ट्रॉनिक्स)]] की सूरत में बस संकेतों को बनाए रखने के लिए जिम्मेदार होते हैं। | ||

इंटेल इस सम्मेलन को निरंतर त्रि- | इंटेल इस सम्मेलन को निरंतर त्रि-अवस्था के रूप में संदर्भित करता है, और इसका उपयोग [[लो पिन काउंट]] बस में भी करता है। | ||

== [[तीन-राज्य बस]] के विकल्प == | == [[तीन-राज्य बस|तीन-अवस्था बस]] के विकल्प == | ||

[[ खुला कलेक्टर | खुला कलेक्टर]] इनपुट/आउटपुट थ्री-स्टेट लॉजिक का लोकप्रिय विकल्प है। उदाहरण के लिए, I²C बस प्रोटोकॉल ( द्वि-दिशात्मक संचार बस प्रोटोकॉल जो | [[ खुला कलेक्टर | खुला कलेक्टर]] इनपुट/आउटपुट थ्री-स्टेट लॉजिक का लोकप्रिय विकल्प है। उदाहरण के लिए, I²C बस प्रोटोकॉल ( द्वि-दिशात्मक संचार बस प्रोटोकॉल जो प्रायः उपकरणों के बीच उपयोग किया जाता है) दो संचार लाइनों पर पुल-अप प्रतिरोधों के उपयोग को निर्दिष्ट करता है। जब उपकरण निष्क्रिय होते हैं, तो वे संचार लाइनें जारी करते हैं और उनके आउटपुट को त्रि-स्थिति बताते हैं, इस प्रकार परिपथ पर उनके प्रभाव को हटाते हैं। जब बस के सभी उपकरणों ने संचार लाइनें जारी कर दी हैं, तो परिपथ पर एकमात्र प्रभाव पुल-अप प्रतिरोधों का होता है, जो लाइनों को ऊंचा खींचते हैं। जब कोई उपकरण संचार करना चाहता है, तो वह हाई-जेड स्थिति से बाहर आता है और लाइन को नीचे चलाता है। इस प्रोटोकॉल का उपयोग करके संचार करने वाले डिवाइस या तो लाइन को ऊपर तैरने देते हैं, या इसे नीचे ले जाते हैं - इस प्रकार किसी भी बस विवाद की स्थिति को रोकते हैं जहां डिवाइस लाइन को ऊपर और दूसरे को नीचे चलाता है। | ||

शुरुआती [[ microcontroller |microcontroller]] ्स में | शुरुआती [[ microcontroller |microcontroller]] ्स में प्रायः कुछ पिन होते हैं जो केवल इनपुट के रूप में कार्य कर सकते हैं, अन्य पिन जो केवल पुश-पुल आउटपुट के रूप में कार्य कर सकते हैं, और कुछ पिन जो केवल ओपन कलेक्टर इनपुट/आउटपुट के रूप में कार्य कर सकते हैं। विशिष्ट आधुनिक माइक्रोकंट्रोलर में कई तीन-अवस्था सामान्य-उद्देश्य इनपुट/आउटपुट पिन होते हैं जिन्हें किसी भी प्रकार के पिन के रूप में कार्य करने के लिए प्रोग्राम किया जा सकता है। | ||

तीन- | तीन-अवस्था बस का उपयोग सामान्यतः एकल [[मुद्रित सर्किट बोर्ड|मुद्रित परिपथ बोर्ड]] (पीसीबी) पर चिप्स के बीच या कभी-कभी सामान्य [[बैकप्लेन]] में प्लग किए गए पीसीबी के बीच किया जाता है। | ||

ऑन-चिप कनेक्शन के लिए तीन- | ऑन-चिप कनेक्शन के लिए तीन-अवस्था तर्क का उपयोग करने की अनुशंसा नहीं की जाती है, बल्कि इंटर-चिप कनेक्शन के लिए।<ref> | ||

경종민, [http://vswww.kaist.ac.kr/ENGLISH/old_lecture/ee878-2002/lecture/SoC_22-OCNetwork-1113.pdf ''On-Chip Buses/Networks for SoC''] "On-Chip Buses [have] No use of tri-state signals [because] Tri-state bus is difficult for static timing analysis" | 경종민, [http://vswww.kaist.ac.kr/ENGLISH/old_lecture/ee878-2002/lecture/SoC_22-OCNetwork-1113.pdf ''On-Chip Buses/Networks for SoC''] "On-Chip Buses [have] No use of tri-state signals [because] Tri-state bus is difficult for static timing analysis" | ||

</ref> | </ref> | ||

तीन- | तीन-अवस्था बफ़र्स, जब बस (कंप्यूटिंग) पर संचार करने के लिए कई उपकरणों को सक्षम करने के लिए उपयोग किया जाता है, तो मल्टीप्लेक्सर द्वारा कार्यात्मक रूप से प्रतिस्थापित किया जा सकता है।<ref name="alternative to tri state buffers - mux">{{cite web|title=त्रि राज्य बफर|url=http://www.cs.umd.edu/class/sum2003/cmsc311/Notes/CompOrg/tristate.html}}</ref> यह उपकरणों की श्रृंखला से आउटपुट का चयन करने और को बस में लिखने में मदद करेगा। | ||

== यह भी देखें == | == यह भी देखें == | ||

Revision as of 10:33, 7 June 2023

डिजिटल इलेक्ट्रॉनिक्स में, त्रि-अवस्था या तीन-अवस्था बफर प्रकार का डिजिटल बफर है जिसमें तीन स्थिर अवस्थाएँ होती हैं: उच्च आउटपुट अवस्था, निम्न आउटपुट अवस्था और उच्च-प्रतिबाधा अवस्था। उच्च-प्रतिबाधा अवस्था में, बफर का आउटपुट आउटपुट बस से डिस्कनेक्ट हो जाता है, जिससे अन्य डिवाइस त्रि-अवस्था बफर से हस्तक्षेप के बिना बस को चला सकते हैं। यह उन स्थितियों में उपयोगी हो सकता है जहां ही बस से कई डिवाइस जुड़े हुए हैं और इसे बारी-बारी से एक्सेस करने की आवश्यकता है। अपनी बस में तीन-अवस्था तर्क को लागू करने वाली प्रणाली को तीन-अवस्था बस या त्रि-अवस्था बस के रूप में जाना जाता है।

त्रि-अवस्था बफ़र्स सामान्यतः बस-आधारित सिस्टम में उपयोग किए जाते हैं, जहां कई डिवाइस ही बस से जुड़े होते हैं और इसे साझा करने की आवश्यकता होती है। उदाहरण के लिए, कंप्यूटर सिस्टम में, कई डिवाइस जैसे कि सीपीयू, मेमोरी और पेरिफेरल्स ही डेटा बस से जुड़े हो सकते हैं। यह सुनिश्चित करने के लिए कि समय में केवल डिवाइस बस में डेटा संचारित कर सकता है, प्रत्येक डिवाइस त्रि-अवस्था बफर से लैस है। जब कोई उपकरण डेटा संचारित करना चाहता है, तो वह अपने त्रि-अवस्था बफर को सक्रिय करता है, जो इसके आउटपुट को बस से जोड़ता है और इसे डेटा संचारित करने की अनुमति देता है। जब ट्रांसमिशन पूरा हो जाता है, तो डिवाइस अपने त्रि-अवस्था बफर को निष्क्रिय कर देता है, जो इसके आउटपुट को बस से डिस्कनेक्ट कर देता है और किसी अन्य डिवाइस को बस तक पहुंचने की अनुमति देता है।

गेट्स, फ्लिप-फ्लॉप, या अन्य डिजिटल लॉजिक परिपथ का उपयोग करके त्रि-अवस्था बफ़र्स को लागू किया जा सकता है। वे बस में क्रॉसस्टॉक और शोर को अल्प करने के लिए उपयोगी होते हैं, और कई उपकरणों को बिना किसी हस्तक्षेप के ही बस को साझा करने की अनुमति देते हैं।

| INPUT | OUTPUT | |

|---|---|---|

| A | B | C |

| 0 | 0 | Z (high impedance) |

| 1 | Z (high impedance) | |

| 0 | 1 | 0 |

| 1 | 1 | |

उपयोग

तीसरे अवस्था की मूल अवधारणा, उच्च प्रतिबाधा (हाय-जेड), बाकी परिपथ से डिवाइस के प्रभाव को प्रभावी ढंग से हटाना है। यदि से अधिक डिवाइस विद्युत रूप से किसी अन्य डिवाइस से जुड़े हैं, तो आउटपुट को हाई-जेड स्थिति में डालने का उपयोग प्रायः शॉर्ट परिपथ को रोकने के लिए किया जाता है, या डिवाइस उच्च ड्राइविंग (तार्किक 1) दूसरे डिवाइस के खिलाफ अल्प ड्राइविंग (तार्किक 0) करता है।

कुशल बहुसंकेतक ्स को लागू करने के लिए तीन-अवस्था बफ़र्स का भी उपयोग किया जा सकता है, विशेष रूप से बड़ी संख्या में इनपुट वाले।[1] साझा बस (कंप्यूटिंग) के संचालन के लिए तीन-अवस्था बफर आवश्यक हैं।

तीन-अवस्था तर्क एल ई डी (त्रि-अवस्था बहुसंकेतन या Charlieplexing ) के सेट को चलाने के लिए आवश्यक तारों की संख्या को अल्प कर सकता है।

आउटपुट सक्षम बनाम चिप चयन

बस से कनेक्ट करने के लिए डिज़ाइन किए गए कई मेमोरी डिवाइस (जैसे RAM और ROM चिप) में दोनों होते हैं CS (चिप का चयन करें) और OE (आउटपुट इनेबल) पिन, जो सतही तौर पर ही काम करते दिखते हैं। यदि CS का दावा नहीं किया गया है, आउटपुट उच्च प्रतिबाधा हैं।

अंतर सिग्नल को आउटपुट करने के लिए आवश्यक समय में निहित है। जब चिप का चयन निष्क्रिय हो जाता है, तो चिप आंतरिक रूप से संचालित नहीं होती है, और पता प्रदान करने और डेटा प्राप्त करने के बीच महत्वपूर्ण विलंब होगा। (निश्चित रूप से फायदा यह है कि इस मामले में चिप न्यूनतम बिजली की खपत करती है।)

जब चिप चयन पर जोर दिया जाता है, तो चिप आंतरिक रूप से एक्सेस करता है, और आउटपुट सक्षम करने से केवल अंतिम आउटपुट ड्राइवर अक्षम होते हैं। यह तब किया जा सकता है जब बस अन्य उद्देश्यों के लिए उपयोग में हो, और जब आउटपुट सक्षम अंत में जोर दिया जाता है, तो डेटा न्यूनतम विलंब के साथ दिखाई देगा। आउटपुट इनेबल लाइन के साथ ROM या स्टेटिक रैम चिप सामान्यतः दो एक्सेस टाइम को सूचीबद्ध करेगा: चिप सेलेक्ट ऐसर्ड और एड्रेस वैलिड से, और दूसरा, अल्प समय की प्रारंभ जब आउटपुट इनेबल होता है।

पुल-अप और पुल-डाउन का प्रयोग

जब आउटपुट त्रि-कहा जाता है (हाय-जेड स्थिति में) बाकी परिपथ पर उनका प्रभाव हटा दिया जाता है, और परिपथ नोड फ्लोटिंग होगा यदि कोई अन्य परिपथ तत्व इसकी स्थिति निर्धारित नहीं करता है। परिपथ डिजाइनर प्रायः परिपथ को प्रभावित करने के लिए पुल-अप रोकनेवाला | पुल-अप या पुल-डाउन रेसिस्टर्स (सामान्यतः 1–100 kΩ की सीमा के भीतर) का उपयोग करते हैं, जब आउटपुट त्रि-कहा जाता है।

पीसीआई स्थानीय बस पुल-अप प्रतिरोधक प्रदान करती है, लेकिन बस की बड़ी वितरित क्षमता को देखते हुए सिग्नल को उच्च खींचने के लिए उन्हें कई घड़ी चक्रों की आवश्यकता होगी। हाई-स्पीड ऑपरेशन को सक्षम करने के लिए, प्रोटोकॉल की आवश्यकता होती है कि हाई-जेड स्थिति में जाने से पहले अल्प से अल्प घड़ी चक्र के लिए बस ड्राइव से कनेक्ट होने वाला प्रत्येक उपकरण महत्वपूर्ण नियंत्रण संकेतों को उच्च करता है। इस तरह, पुल-अप प्रतिरोध केवल रिसाव (इलेक्ट्रॉनिक्स) की सूरत में बस संकेतों को बनाए रखने के लिए जिम्मेदार होते हैं।

इंटेल इस सम्मेलन को निरंतर त्रि-अवस्था के रूप में संदर्भित करता है, और इसका उपयोग लो पिन काउंट बस में भी करता है।

तीन-अवस्था बस के विकल्प

खुला कलेक्टर इनपुट/आउटपुट थ्री-स्टेट लॉजिक का लोकप्रिय विकल्प है। उदाहरण के लिए, I²C बस प्रोटोकॉल ( द्वि-दिशात्मक संचार बस प्रोटोकॉल जो प्रायः उपकरणों के बीच उपयोग किया जाता है) दो संचार लाइनों पर पुल-अप प्रतिरोधों के उपयोग को निर्दिष्ट करता है। जब उपकरण निष्क्रिय होते हैं, तो वे संचार लाइनें जारी करते हैं और उनके आउटपुट को त्रि-स्थिति बताते हैं, इस प्रकार परिपथ पर उनके प्रभाव को हटाते हैं। जब बस के सभी उपकरणों ने संचार लाइनें जारी कर दी हैं, तो परिपथ पर एकमात्र प्रभाव पुल-अप प्रतिरोधों का होता है, जो लाइनों को ऊंचा खींचते हैं। जब कोई उपकरण संचार करना चाहता है, तो वह हाई-जेड स्थिति से बाहर आता है और लाइन को नीचे चलाता है। इस प्रोटोकॉल का उपयोग करके संचार करने वाले डिवाइस या तो लाइन को ऊपर तैरने देते हैं, या इसे नीचे ले जाते हैं - इस प्रकार किसी भी बस विवाद की स्थिति को रोकते हैं जहां डिवाइस लाइन को ऊपर और दूसरे को नीचे चलाता है।

शुरुआती microcontroller ्स में प्रायः कुछ पिन होते हैं जो केवल इनपुट के रूप में कार्य कर सकते हैं, अन्य पिन जो केवल पुश-पुल आउटपुट के रूप में कार्य कर सकते हैं, और कुछ पिन जो केवल ओपन कलेक्टर इनपुट/आउटपुट के रूप में कार्य कर सकते हैं। विशिष्ट आधुनिक माइक्रोकंट्रोलर में कई तीन-अवस्था सामान्य-उद्देश्य इनपुट/आउटपुट पिन होते हैं जिन्हें किसी भी प्रकार के पिन के रूप में कार्य करने के लिए प्रोग्राम किया जा सकता है।

तीन-अवस्था बस का उपयोग सामान्यतः एकल मुद्रित परिपथ बोर्ड (पीसीबी) पर चिप्स के बीच या कभी-कभी सामान्य बैकप्लेन में प्लग किए गए पीसीबी के बीच किया जाता है।

ऑन-चिप कनेक्शन के लिए तीन-अवस्था तर्क का उपयोग करने की अनुशंसा नहीं की जाती है, बल्कि इंटर-चिप कनेक्शन के लिए।[2] तीन-अवस्था बफ़र्स, जब बस (कंप्यूटिंग) पर संचार करने के लिए कई उपकरणों को सक्षम करने के लिए उपयोग किया जाता है, तो मल्टीप्लेक्सर द्वारा कार्यात्मक रूप से प्रतिस्थापित किया जा सकता है।[3] यह उपकरणों की श्रृंखला से आउटपुट का चयन करने और को बस में लिखने में मदद करेगा।

यह भी देखें

- बफर एम्पलीफायर

- तर्क स्तर

- मेटास्टेबिलिटी (इलेक्ट्रॉनिक्स)

- तीन-मूल्यवान तर्क

- चार-मूल्यवान तर्क

- नौ-मूल्यवान तर्क

- परवाह नहीं

- सिंगल पोल, सेंटर ऑफ (एसपीसीओ)

नोट्स और संदर्भ

- ↑ Hill, Winfield; Horowitz, Paul (1989). इलेक्ट्रॉनिक्स की कला. Cambridge University Press. pp. 495–497. ISBN 0-521-37095-7.

- ↑ 경종민, On-Chip Buses/Networks for SoC "On-Chip Buses [have] No use of tri-state signals [because] Tri-state bus is difficult for static timing analysis"

- ↑ "त्रि राज्य बफर".

बाहरी संबंध

- Special-output Gates on All About Circuits

- Principle of Tristate Multiplexing