राउटिंग (इलेक्ट्रॉनिक डिजाइन ऑटोमेशन): Difference between revisions

No edit summary |

No edit summary |

||

| Line 4: | Line 4: | ||

इलेक्ट्रॉनिक डिज़ाइन में, वायर राउटिंग, जिसे सामान्यतः राउटिंग कहा जाता है, प्रिंटेड सर्किट बोर्ड (पीसीबी - PCBs) और एकीकृत परिपथ (आईसी - ICs) के डिज़ाइन में एक उपाय है। यह एक पूर्ववर्ती चरण पर निर्मित होता है, जिसे प्लेसमेंट कहा जाता है, जो एक पीसीबी पर आईसी या घटक के प्रत्येक सक्रिय तत्व का स्थान निर्धारित करता है। प्लेसमेंट के बाद, राउटिंग चरण आईसी के लिए सभी आकृतियों के नियमों का पालन करते हुए रखे गए घटकों को ठीक से संयुक्त करने के लिए आवश्यक तारों को जोड़ता है। साथ में, आईसी के डिज़ाइन के लिए प्लेसमेंट और राउटिंग के चरणों को स्थान और मार्ग के रूप में जाना जाता है। | इलेक्ट्रॉनिक डिज़ाइन में, वायर राउटिंग, जिसे सामान्यतः राउटिंग कहा जाता है, प्रिंटेड सर्किट बोर्ड (पीसीबी - PCBs) और एकीकृत परिपथ (आईसी - ICs) के डिज़ाइन में एक उपाय है। यह एक पूर्ववर्ती चरण पर निर्मित होता है, जिसे प्लेसमेंट कहा जाता है, जो एक पीसीबी पर आईसी या घटक के प्रत्येक सक्रिय तत्व का स्थान निर्धारित करता है। प्लेसमेंट के बाद, राउटिंग चरण आईसी के लिए सभी आकृतियों के नियमों का पालन करते हुए रखे गए घटकों को ठीक से संयुक्त करने के लिए आवश्यक तारों को जोड़ता है। साथ में, आईसी के डिज़ाइन के लिए प्लेसमेंट और राउटिंग के चरणों को स्थान और मार्ग के रूप में जाना जाता है। | ||

सभी राउटर का कार्य समान होता है। उन्हें कुछ पूर्व आकलन पर निर्भर पालीगन दिए गए हैं जिनमें कोशिकाओं पर पिन और वैकल्पिक रूप से कुछ पूर्व तारों को प्रीरूट्स कहा जाता है। इनमें से प्रत्येक पालीगन एक जाल से जुड़ा होता है, सामान्यतः पर नाम या संख्या से। राउटर का प्राथमिक कार्य ज्यामिति बनाना है जैसे कि एक ही नेट को सौंपे गए सभी टर्मिनल जुड़े हुए हैं, अलग-अलग नेट को सौंपे गए कोई भी टर्मिनल जुड़े नहीं हैं, और सभी डिज़ाइन नियमों का पालन किया जाता है। एक राउटर उन टर्मिनलों को कनेक्ट न करने से विफल हो सकता है जिन्हें कनेक्ट किया जाना चाहिए, गलती से दो टर्मिनलों को कनेक्ट करके जो कनेक्ट नहीं होना चाहिए या डिज़ाइन नियम | सभी राउटर का कार्य समान होता है। उन्हें कुछ पूर्व आकलन पर निर्भर पालीगन दिए गए हैं जिनमें कोशिकाओं पर पिन और वैकल्पिक रूप से कुछ पूर्व तारों को प्रीरूट्स कहा जाता है। इनमें से प्रत्येक पालीगन एक जाल से जुड़ा होता है, सामान्यतः पर नाम या संख्या से। राउटर का प्राथमिक कार्य ज्यामिति बनाना है जैसे कि एक ही नेट को सौंपे गए सभी टर्मिनल जुड़े हुए हैं, अलग-अलग नेट को सौंपे गए कोई भी टर्मिनल जुड़े नहीं हैं, और सभी डिज़ाइन नियमों का पालन किया जाता है। एक राउटर उन टर्मिनलों को कनेक्ट न करने से विफल हो सकता है जिन्हें कनेक्ट किया जाना चाहिए, गलती से दो टर्मिनलों को कनेक्ट करके जो कनेक्ट नहीं होना चाहिए या डिज़ाइन नियम खंडित बनाकर इसे उपयोग करना चाहिए। इसके अलावा, नेट को सही ढंग से कनेक्ट करने के लिए, राउटर से यह सुनिश्चित करने की भी उम्मीद की जा सकती है कि डिज़ाइन समय को पूरा करता है, कोई क्रॉसस्टॉक समस्या नहीं है, किसी भी धातु घनत्व आवश्यकताओं को पूरा करता है, एंटीना प्रभाव से ग्रस्त नहीं है, और इसी तरह परस्पर विरोधी उद्देश्यों की यह लंबी सूची ही राउटिंग को बेहद कठिन बना देती है। | ||

राउटिंग से जुड़ी सामान्यतः हर समस्या को मुश्किल माना जाता है। सबसे सरल राउटिंग समस्या, जिसे स्टीनर ट्री समस्या कहा जाता है, बिना किसी बाधा के एक परत में एक जाल के लिए सबसे छोटे मार्ग को ढूंढने के लिए कोई और डिज़ाइन नियम नहीं है यदि सभी कोणों की अनुमति मिल जाती है और एनपी-पूर्ण है यदि केवल क्षैतिज और ऊर्ध्वाधर तारों की अनुमति है। चैनल राउटिंग के वेरिएंट को भी एनपी-पूर्ण दिखाया गया है, साथ ही राउटिंग जो क्रॉसस्टॉक, वायस की संख्या आदि को कम करती है। इसलिए राउटर शायद ही कभी एक इष्टतम परिणाम ढूंढने का प्रयास करते हैं। इसके स्थान पर, सामान्यतः सभी राउटिंग अनुमानों पर आधारित होते हैं जो एक ऐसा समाधान ढूंढने की कोशिश करते हैं जो इसके अतिरिक्त तुलना में अच्छा हो। | राउटिंग से जुड़ी सामान्यतः हर समस्या को मुश्किल माना जाता है। सबसे सरल राउटिंग समस्या, जिसे स्टीनर ट्री समस्या कहा जाता है, बिना किसी बाधा के एक परत में एक जाल के लिए सबसे छोटे मार्ग को ढूंढने के लिए कोई और डिज़ाइन नियम नहीं है यदि सभी कोणों की अनुमति मिल जाती है और एनपी-पूर्ण है यदि केवल क्षैतिज और ऊर्ध्वाधर तारों की अनुमति है। चैनल राउटिंग के वेरिएंट को भी एनपी-पूर्ण दिखाया गया है, साथ ही राउटिंग जो क्रॉसस्टॉक, वायस की संख्या आदि को कम करती है। इसलिए राउटर शायद ही कभी एक इष्टतम परिणाम ढूंढने का प्रयास करते हैं। इसके स्थान पर, सामान्यतः सभी राउटिंग अनुमानों पर आधारित होते हैं जो एक ऐसा समाधान ढूंढने की कोशिश करते हैं जो इसके अतिरिक्त तुलना में अच्छा हो। | ||

| Line 12: | Line 12: | ||

== राउटर के प्रकार == | == राउटर के प्रकार == | ||

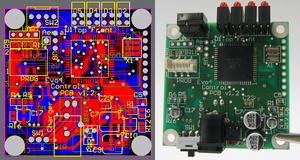

[[File:PCB design and realisation smt and through hole.png|thumb|एक पीसीबी (PCB) एक कंप्यूटर (बाएं) पर एक डिजाइन के रूप में और घटकों (दाएं) के साथ आबादी वाले बोर्ड असेंबली के रूप में महसूस किया गया। बोर्ड डबल साइडेड है, जिसमें थ्रू-होल प्लेटिंग, ग्रीन सोल्डर प्रतिरोध और एक व्हाइट लेजेंड है। दोनों सतह माउंट और थ्रू-होल घटकों का उपयोग किया गया है।]] | [[File:PCB design and realisation smt and through hole.png|thumb|एक पीसीबी (PCB) एक कंप्यूटर (बाएं) पर एक डिजाइन के रूप में और घटकों (दाएं) के साथ आबादी वाले बोर्ड असेंबली के रूप में महसूस किया गया। बोर्ड डबल साइडेड है, जिसमें थ्रू-होल प्लेटिंग, ग्रीन सोल्डर प्रतिरोध और एक व्हाइट लेजेंड है। दोनों सतह माउंट और थ्रू-होल घटकों का उपयोग किया गया है।]] | ||

ईडीए राउटर के शुरुआती प्रकार "मैनुअल राउटर" थे - ड्राफ्टर ने प्रत्येक नेट के प्रत्येक लाइन सेगमेंट के एंडपॉइंट पर एक माउस क्लिक किया। आधुनिक पीसीबी (PCB) डिजाइन सॉफ्टवेयर सामान्यतः पर "इंटरैक्टिव राउटर्स" प्रदान करता है - ड्राफ्टर एक पैड का चयन करता है और ईडीए (EDA) टूल को यह पता लगाने के लिए कुछ जगहों पर क्लिक करता है कि कहां जाना है, और ईडीए टूल तारों को उस पथ के जितना संभव हो सके बिना | ईडीए राउटर के शुरुआती प्रकार "मैनुअल राउटर" थे - ड्राफ्टर ने प्रत्येक नेट के प्रत्येक लाइन सेगमेंट के एंडपॉइंट पर एक माउस क्लिक किया। आधुनिक पीसीबी (PCB) डिजाइन सॉफ्टवेयर सामान्यतः पर "इंटरैक्टिव राउटर्स" प्रदान करता है - ड्राफ्टर एक पैड का चयन करता है और ईडीए (EDA) टूल को यह पता लगाने के लिए कुछ जगहों पर क्लिक करता है कि कहां जाना है, और ईडीए टूल तारों को उस पथ के जितना संभव हो सके बिना खंडित किए रखने की कोशिश करता है। डिज़ाइन नियम जाँच डीआरसी (DRC)। कुछ और उन्नत इंटरएक्टिव राउटर में एक इंटरेक्टिव राउटर में "पुश एंड शॉव" विशेषताएं होती हैं, ईडीए उपकरण अन्य नेट को रास्ते से हटा देता है, यदि संभव हो तो, एक नया तार लगाने के लिए जहां ड्राफ्टर इसे चाहता है और फिर भी डीआरसी का खंडित करने से बचता है। | ||

आधुनिक पीसीबी डिजाइन सॉफ्टवेयर भी आम तौर पर "ऑटोराउटर" प्रदान करता है जो मानव हस्तक्षेप के बिना सभी शेष अनियंत्रित कनेक्शनों को रूट करता है। | आधुनिक पीसीबी डिजाइन सॉफ्टवेयर भी आम तौर पर "ऑटोराउटर" प्रदान करता है जो मानव हस्तक्षेप के बिना सभी शेष अनियंत्रित कनेक्शनों को रूट करता है। | ||

| Line 59: | Line 59: | ||

यह प्रक्रिया तब तक दोहराई जाती है जब तक कि सभी नेट रूट नहीं हो जाते या प्रोग्राम हार नहीं मान लेता। | यह प्रक्रिया तब तक दोहराई जाती है जब तक कि सभी नेट रूट नहीं हो जाते या प्रोग्राम हार नहीं मान लेता। | ||

एक वैकल्पिक तरीका यह है कि शॉर्ट्स, डिज़ाइन नियमों के | एक वैकल्पिक तरीका यह है कि शॉर्ट्स, डिज़ाइन नियमों के खंडित, अवरोधों आदि को तार की अतिरिक्त लंबाई के समान स्तर पर माना जाए - यानी, परिमित लागतों को कम करने के लिए के बजाय निरपेक्षता से बचा जाना चाहिए। यह बहु-पास "पुनरावृत्ति-सुधार" राउटिंग विधि<ref name="Rubin_1974" /> निम्न एल्गोरिथम द्वारा वर्णित है: | ||

* कई पुनरावृत्त पासों में से प्रत्येक के लिए: | * कई पुनरावृत्त पासों में से प्रत्येक के लिए: | ||

* "ऑब्जेक्टिव फंक्शन" के वजन मापदंडों को निर्धारित या समायोजित करें (अतिरिक्त तार लंबाई की प्रत्येक इकाई के लिए वजन पैरामीटर मान और प्रत्येक प्रकार के | * "ऑब्जेक्टिव फंक्शन" के वजन मापदंडों को निर्धारित या समायोजित करें (अतिरिक्त तार लंबाई की प्रत्येक इकाई के लिए वजन पैरामीटर मान और प्रत्येक प्रकार के खंडित के लिए)। उदाहरण के लिए, पहले पास के लिए, अतिरिक्त तार की लंबाई को आमतौर पर एक उच्च लागत दी जा सकती है, जबकि डिजाइन के खंडित जैसे कि शॉर्ट्स, आसन्नता, आदि को कम लागत दी जाती है। बाद के पासों में, लागतों का सापेक्ष क्रम बदल दिया जाता है ताकि खंडित उच्च लागत वाले हों, या पूरी तरह से प्रतिबंधित हो सकते हैं। | ||

* एक अनुक्रम चुनें जिसमें इस पास के दौरान जाल को रूट किया जाना है। | * एक अनुक्रम चुनें जिसमें इस पास के दौरान जाल को रूट किया जाना है। | ||

* "रिप अप" और बदले में प्रत्येक नेट को फिर से रूट करें, ताकि उस नेट के उद्देश्य फ़ंक्शन के मूल्य को कम किया जा सके। (कुछ राउटिंग में सामान्य रूप से शॉर्ट्स या अन्य डिज़ाइन | * "रिप अप" और बदले में प्रत्येक नेट को फिर से रूट करें, ताकि उस नेट के उद्देश्य फ़ंक्शन के मूल्य को कम किया जा सके। (कुछ राउटिंग में सामान्य रूप से शॉर्ट्स या अन्य डिज़ाइन खंडित होंगे।) | ||

* राउटिंग पूर्ण और सही होने तक अगले पुनरावृत्त पास पर आगे बढ़ें, इसमें और सुधार नहीं किया गया है, या कुछ अन्य समाप्ति मानदंड संतुष्ट हैं। | * राउटिंग पूर्ण और सही होने तक अगले पुनरावृत्त पास पर आगे बढ़ें, इसमें और सुधार नहीं किया गया है, या कुछ अन्य समाप्ति मानदंड संतुष्ट हैं। | ||

Revision as of 12:56, 28 October 2022

इलेक्ट्रॉनिक डिज़ाइन में, वायर राउटिंग, जिसे सामान्यतः राउटिंग कहा जाता है, प्रिंटेड सर्किट बोर्ड (पीसीबी - PCBs) और एकीकृत परिपथ (आईसी - ICs) के डिज़ाइन में एक उपाय है। यह एक पूर्ववर्ती चरण पर निर्मित होता है, जिसे प्लेसमेंट कहा जाता है, जो एक पीसीबी पर आईसी या घटक के प्रत्येक सक्रिय तत्व का स्थान निर्धारित करता है। प्लेसमेंट के बाद, राउटिंग चरण आईसी के लिए सभी आकृतियों के नियमों का पालन करते हुए रखे गए घटकों को ठीक से संयुक्त करने के लिए आवश्यक तारों को जोड़ता है। साथ में, आईसी के डिज़ाइन के लिए प्लेसमेंट और राउटिंग के चरणों को स्थान और मार्ग के रूप में जाना जाता है।

सभी राउटर का कार्य समान होता है। उन्हें कुछ पूर्व आकलन पर निर्भर पालीगन दिए गए हैं जिनमें कोशिकाओं पर पिन और वैकल्पिक रूप से कुछ पूर्व तारों को प्रीरूट्स कहा जाता है। इनमें से प्रत्येक पालीगन एक जाल से जुड़ा होता है, सामान्यतः पर नाम या संख्या से। राउटर का प्राथमिक कार्य ज्यामिति बनाना है जैसे कि एक ही नेट को सौंपे गए सभी टर्मिनल जुड़े हुए हैं, अलग-अलग नेट को सौंपे गए कोई भी टर्मिनल जुड़े नहीं हैं, और सभी डिज़ाइन नियमों का पालन किया जाता है। एक राउटर उन टर्मिनलों को कनेक्ट न करने से विफल हो सकता है जिन्हें कनेक्ट किया जाना चाहिए, गलती से दो टर्मिनलों को कनेक्ट करके जो कनेक्ट नहीं होना चाहिए या डिज़ाइन नियम खंडित बनाकर इसे उपयोग करना चाहिए। इसके अलावा, नेट को सही ढंग से कनेक्ट करने के लिए, राउटर से यह सुनिश्चित करने की भी उम्मीद की जा सकती है कि डिज़ाइन समय को पूरा करता है, कोई क्रॉसस्टॉक समस्या नहीं है, किसी भी धातु घनत्व आवश्यकताओं को पूरा करता है, एंटीना प्रभाव से ग्रस्त नहीं है, और इसी तरह परस्पर विरोधी उद्देश्यों की यह लंबी सूची ही राउटिंग को बेहद कठिन बना देती है।

राउटिंग से जुड़ी सामान्यतः हर समस्या को मुश्किल माना जाता है। सबसे सरल राउटिंग समस्या, जिसे स्टीनर ट्री समस्या कहा जाता है, बिना किसी बाधा के एक परत में एक जाल के लिए सबसे छोटे मार्ग को ढूंढने के लिए कोई और डिज़ाइन नियम नहीं है यदि सभी कोणों की अनुमति मिल जाती है और एनपी-पूर्ण है यदि केवल क्षैतिज और ऊर्ध्वाधर तारों की अनुमति है। चैनल राउटिंग के वेरिएंट को भी एनपी-पूर्ण दिखाया गया है, साथ ही राउटिंग जो क्रॉसस्टॉक, वायस की संख्या आदि को कम करती है। इसलिए राउटर शायद ही कभी एक इष्टतम परिणाम ढूंढने का प्रयास करते हैं। इसके स्थान पर, सामान्यतः सभी राउटिंग अनुमानों पर आधारित होते हैं जो एक ऐसा समाधान ढूंढने की कोशिश करते हैं जो इसके अतिरिक्त तुलना में अच्छा हो।

डिज़ाइन नियम कभी-कभी परत से परत में काफी भिन्न होते हैं। उदाहरण के लिए, निचली परतों पर अनुमत चौड़ाई और रिक्ति ऊपरी परतों पर अनुमत चौड़ाई और रिक्ति से चार या अधिक गुना छोटी हो सकती है। यह कई अतिरिक्त जटिलताओं का परिचय देता है जो अन्य अनुप्रयोगों जैसे कि मुद्रित सर्किट बोर्ड या मल्टी-चिप मॉड्यूल डिज़ाइन के लिए राउटर के सामने नहीं आती हैं। विशेष रूप से कठिनाइयाँ तब आती हैं जब नियम एक-दूसरे के सरल गुणक नहीं होते हैं, और जब विअस को विभिन्न नियमों के साथ परतों के बीच से गुजरना पड़ता है।

राउटर के प्रकार

ईडीए राउटर के शुरुआती प्रकार "मैनुअल राउटर" थे - ड्राफ्टर ने प्रत्येक नेट के प्रत्येक लाइन सेगमेंट के एंडपॉइंट पर एक माउस क्लिक किया। आधुनिक पीसीबी (PCB) डिजाइन सॉफ्टवेयर सामान्यतः पर "इंटरैक्टिव राउटर्स" प्रदान करता है - ड्राफ्टर एक पैड का चयन करता है और ईडीए (EDA) टूल को यह पता लगाने के लिए कुछ जगहों पर क्लिक करता है कि कहां जाना है, और ईडीए टूल तारों को उस पथ के जितना संभव हो सके बिना खंडित किए रखने की कोशिश करता है। डिज़ाइन नियम जाँच डीआरसी (DRC)। कुछ और उन्नत इंटरएक्टिव राउटर में एक इंटरेक्टिव राउटर में "पुश एंड शॉव" विशेषताएं होती हैं, ईडीए उपकरण अन्य नेट को रास्ते से हटा देता है, यदि संभव हो तो, एक नया तार लगाने के लिए जहां ड्राफ्टर इसे चाहता है और फिर भी डीआरसी का खंडित करने से बचता है।

आधुनिक पीसीबी डिजाइन सॉफ्टवेयर भी आम तौर पर "ऑटोराउटर" प्रदान करता है जो मानव हस्तक्षेप के बिना सभी शेष अनियंत्रित कनेक्शनों को रूट करता है।

ऑटोराउटर के मुख्य प्रकार हैं:

- ग्रिडलेस राउटर[12][8][4][13]

- एरिया राउटर

- ग्राफ सिद्धांत-आधारित राउटर[14]

- टोपोलॉजिकल राउटर

- फ्री स्टाइल राउटर (उर्फ स्पीडवे, पी-सीएडी के लिए डॉस-आधारित ऑटोराउटर)

- टॉप राउटर (एक विंडोज़-आधारित ऑटोराउटर, जिसका उपयोग एरेमेक्स के डेल्टा डिज़ाइन में भी किया जाता है)

- टॉप राउटर (जीईडीए सूट के पीसीबी में एंथनी ब्लेक का ओपन-सोर्स राउटर)

- टॉप राउटर(कैडसॉफ्ट/ऑटो डेस्क ईगल 7.0 और उच्चतर में टोपोलॉजिकल प्री-राउटर)

- पीसीबी को सरल बनाएं (हैंड-राउटिंग परिणामों के साथ बंडल राउटिंग पर ध्यान देने वाला एक टोपोलॉजिकल राउटर)[18]

राउटर कैसे काम करते हैं

कई राउटर निम्नलिखित संयुक्त एल्गोरिदम निष्पादित करते हैं:

- सबसे पहले, मोटे ग्रिड पर राउटिंग करके, प्रत्येक नेट के लिए एक अनुमानित पाठ्यक्रम निर्धारित करता हैं। इस चरण को वैश्विक राउटिंग[19] कहा जाता है और इसमें वैकल्पिक रूप से परतों से जुड़े कार्य शामिल हो सकते है। ग्लोबल राउटिंग निम्नलिखित विस्तृत राउटिंग चरणों के आकार और जटिलता को सीमित करता है, जिसे ग्रिड स्क्वायर द्वारा ग्रिड स्क्वायर किया जा सकता है।

विस्तृत राउटिंग के लिए, सबसे सामान्य तकनीक है रिप-अप और रीरूट जिसे रिप-अप और पुनः रिट्राई के नाम से भी जाना जाता हैं।[1]

उस क्रम का चयन करें जिसमें नेट को रूट किया जाना है।

- प्रत्येक नेट को क्रम से रूट करें

- यदि सभी नेट को सफलतापूर्वक रूट नहीं किया जा सकता है, तो विभिन्न प्रकार की "क्लीनअप" विधियों में से कोई भी लागू करें, जिसमें चयनित राउटिंग हटा दिए जाते हैं, शेष नेट को रूट करने का क्रम बदल दिया जाता है, और शेष राउटिंग को फिर से करने का प्रयास किया जाता है।

यह प्रक्रिया तब तक दोहराई जाती है जब तक कि सभी नेट रूट नहीं हो जाते या प्रोग्राम हार नहीं मान लेता।

एक वैकल्पिक तरीका यह है कि शॉर्ट्स, डिज़ाइन नियमों के खंडित, अवरोधों आदि को तार की अतिरिक्त लंबाई के समान स्तर पर माना जाए - यानी, परिमित लागतों को कम करने के लिए के बजाय निरपेक्षता से बचा जाना चाहिए। यह बहु-पास "पुनरावृत्ति-सुधार" राउटिंग विधि[20] निम्न एल्गोरिथम द्वारा वर्णित है:

- कई पुनरावृत्त पासों में से प्रत्येक के लिए:

- "ऑब्जेक्टिव फंक्शन" के वजन मापदंडों को निर्धारित या समायोजित करें (अतिरिक्त तार लंबाई की प्रत्येक इकाई के लिए वजन पैरामीटर मान और प्रत्येक प्रकार के खंडित के लिए)। उदाहरण के लिए, पहले पास के लिए, अतिरिक्त तार की लंबाई को आमतौर पर एक उच्च लागत दी जा सकती है, जबकि डिजाइन के खंडित जैसे कि शॉर्ट्स, आसन्नता, आदि को कम लागत दी जाती है। बाद के पासों में, लागतों का सापेक्ष क्रम बदल दिया जाता है ताकि खंडित उच्च लागत वाले हों, या पूरी तरह से प्रतिबंधित हो सकते हैं।

- एक अनुक्रम चुनें जिसमें इस पास के दौरान जाल को रूट किया जाना है।

- "रिप अप" और बदले में प्रत्येक नेट को फिर से रूट करें, ताकि उस नेट के उद्देश्य फ़ंक्शन के मूल्य को कम किया जा सके। (कुछ राउटिंग में सामान्य रूप से शॉर्ट्स या अन्य डिज़ाइन खंडित होंगे।)

- राउटिंग पूर्ण और सही होने तक अगले पुनरावृत्त पास पर आगे बढ़ें, इसमें और सुधार नहीं किया गया है, या कुछ अन्य समाप्ति मानदंड संतुष्ट हैं।

अधिकांश राउटर मुख्य रूप से "x" या "y" दिशात्मक तारों को ले जाने के लिए तारों की परतें प्रदान करते हैं, चूंकि ऐसे राउटर हैं जो इस तरह के असाइनमेंट की आवश्यकता से बचते हैं या कम करते हैं।[21] प्रत्येक दृष्टिकोण के फायदे और नुकसान हैं। प्रतिबंधित दिशाएँ बिजली आपूर्ति डिज़ाइन और इंटर-लेयर क्रॉसस्टॉक के नियंत्रण को आसान बनाती हैं, लेकिन मनमाने मार्गों की अनुमति देने से वायस की आवश्यकता कम हो सकती है और आवश्यक वायरिंग परतों की संख्या कम हो सकती है।

यह भी देखें

- इलेक्ट्रॉनिक डिजाइन स्वचालन

- डिजाइन प्रवाह (ईडीए)

- एकीकृत परिपथ डिजाइन

- स्थान और मार्ग

- ऑटो ध्रुवीयता (अंतर जोड़े)

- ऑटो क्रॉसओवर (ईथरनेट)

संदर्भ

- ↑ 1.0 1.1 1.2 1.3 1.4 Byers, T. J. (1991-08-01). Printed Circuit Board Design with Microcomputers (1 ed.). New York, USA: Intertext Publications/Multiscience Press, Inc., McGraw-Hill Book Company. pp. 99–101. ISBN 978-0-07-009558-8. LCCN 91-72187.

- ↑ Ritchey, Lee W. (December 1999). "PCB routers and routing methods" (PDF). PC Design Magazine. Speeding Edge (February 1999). Archived (PDF) from the original on 2018-10-22. Retrieved 2018-10-22.

- ↑ Lee, Chester Y. (September 1961). "An algorithm for path connections and its applications". IRE Transactions on Electronic Computers. EC-10 (3): 346–365. doi:10.1109/TEC.1961.5219222. S2CID 40700386.

- ↑ 4.0 4.1 4.2 4.3 4.4 Kollipara, Ravindranath; Tripathi, Vijai K.; Sergent, Jerry E.; Blackwell, Glenn R.; White, Donald; Staszak, Zbigniew J. (2005). "11.1.3 Packaging Electronic Systems - Design of Printed Wiring Boards" (PDF). In Whitaker, Jerry C.; Dorf, Richard C. (eds.). The Electronics Handbook (2 ed.). CRC Press, Taylor & Francis Group, LLC. p. 1266. ISBN 978-0-8493-1889-4. LCCN 2004057106. Archived (PDF) from the original on 2017-09-25. Retrieved 2017-09-25.

- ↑ Hadlock, Frank O. (1977-12-01). "A shortest path algorithm for grid graphs". Networks. 7 (4): 323–334. doi:10.1002/net.3230070404.

- ↑ Mikami, Koichi; Tabuchi, Kinya (1968). A computer program for optimal routing of printed circuit connectors. IFIPS Proceedings. Vol. H47. pp. 1745–1478.

- ↑ Hightower, David W. (1969). "A solution to line-routing problems on the continuous plane". DAC'69: Proceedings of the 6th Annual Conference on Design Automation. ACM Press. pp. 1–24.

{{cite conference}}: External link in|title= - ↑ 8.0 8.1 8.2 8.3 Minges, Merrill L. (1989). Electronic Materials Handbook: Packaging. Vol. 1. ASM International. ISBN 978-0-87170-285-2. Retrieved 2017-09-27.

- ↑ Reed, James B.; Sangiovanni-Vincentelli, Alberto; Santamauro, Mauro (1985). "A new symbolic channel router: YACR2". IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 4 (3): 203–219. doi:10.1109/TCAD.1985.1270117. S2CID 17065773. [1]

- ↑ 10.0 10.1 10.2 Shankar, Ravi; Fernandez, Eduardo B. (2014-01-12). Einspruch, Norman G. (ed.). VLSI and Computer Architecture. VLSI Electronics Microstructure Science. Vol. 20. Academic Press. ISBN 978-1-48321784-0. Retrieved 2018-10-22.

- ↑ McLellan, Paul (2012-04-23). "Channel Routing Memories". Archived from the original on 2021-05-18. Retrieved 2022-01-01.

- ↑ Finch, Alan C.; Mackenzie, Ken J.; Balsdon, G. J.; Symonds, G. (1985-06-23). A Method for Gridless Routing of Printed Circuit Boards (PDF). 22nd ACM/IEEE Design Automation Conference, Las Vegas, Nevada, USA. Design Automation Conference, 2009. Dac '09. 46th ACM/IEEE. Newtown, Tewkesbury, Gloucestershire, UK: Racal-Redac Ltd. pp. 509–515. doi:10.1109/DAC.1985.1585990. ISBN 0-8186-0635-5. ISSN 0738-100X. Archived (PDF) from the original on 2018-10-22. Retrieved 2018-10-22.

- ↑ Webb, Darrell (2012-12-20). "A Tribute to Alan Finch, the Father of Gridless Autorouting". Archived from the original on 2018-10-22. Retrieved 2018-10-22.

- ↑ Wu, Bo (April 1992). Graph Theory Based Routing Algorithms (PDF) (Thesis). Western Michigan University. S2CID 3357923. Archived from the original (PDF) on 2018-10-22. Retrieved 2018-10-22.

- ↑ "Computer-Partner Kiel GmbH: "Bloodhound" entflechtet Leiterplatten auf 16 Lagen". Computerwoche (in Deutsch). 1992-03-13. Archived from the original on 2018-10-21. Retrieved 2018-10-20.

- ↑ Pfeil, Charles (2017-11-02). "A lifetime designing PCBs: From design to software". EDN Network. Archived from the original on 2018-10-21. Retrieved 2018-10-20.

- ↑ 17.0 17.1 Redlich, Detlef. "1.6. Rechnergestützter Leiterplattenentwurf - Entflechtung" (PDF). Schaltungsdesign (in Deutsch). Ernst-Abbe-Hochschule Jena (EAH). Archived from the original (PDF) on 2018-10-21. Retrieved 2018-10-20.

- ↑ "Simplify Design Automation – the next generation in design methodology".

- ↑ Soukup, Jirí (1979). "Global Router". Proceedings of the 16th Design Automation Conference. San Diego, CA, USA: IEEE Press. pp. 481–489.

- ↑ Rubin, Frank (1974). "An iterative technique for printed wire routing". Proceedings 11th Design Automation Workshop. pp. 308–13.

- ↑ Linsker, Ralph (1984). "An iterative-improvement penalty-function-driven wire routing system" (PDF). IBM Journal of Research and Development. 28 (5): 613–624. doi:10.1147/rd.285.0613.

अग्रिम पठन

- Scheffer, Louis K.; Lavagno, Luciano; Martin, Grant (2006). "Chapter 8: Routing". Electronic Design Automation For Integrated Circuits Handbook. Vol. II. Boca Raton, FL, USA: CRC Press / Taylor & Francis. ISBN 978-0-8493-3096-4.