मेमोरी ज्यामिति: Difference between revisions

No edit summary |

No edit summary |

||

| Line 4: | Line 4: | ||

{{more footnotes|date=September 2010}} | {{more footnotes|date=September 2010}} | ||

}} | }} | ||

'''मेमोरी ज्योमेट्री''' आधुनिक कंप्यूटरों के डिज़ाइनों में [[ रैंडम एक्सेस मेमोरी |रैंडम एक्सेस मेमोरी]] की आंतरिक संरचना का वर्णन करती है। मेमोरी ज्योमेट्री अपने कंप्यूटर को अपग्रेड करने वाले उपभोक्ताओं के लिए चिंता का विषय है क्योंकि पुराने मेमोरी कंट्रोलर बाद के कंप्यूटरों के साथ संगत नहीं हो सकते हैं। ओवरलैपिंग संख्या के कारण मेमोरी ज्योमेट्री टर्मिनोलॉजी भ्रमित करने वाली हो सकती है। | |||

मेमोरी सिस्टम की | मेमोरी सिस्टम की ज्योमेट्री को एक मल्टी-डायमेंशनल ऐरे के रूप में समझा जा सकता है। प्रत्येक डायमेंशन की अपनी विशेषताएं और भौतिक स्थितियाँ होती है। उदाहरण के लिए मेमोरी मॉड्यूल पर डेटा पिन की संख्या एक डायमेंशन होती है। | ||

==भौतिक विशेषताएं== | ==भौतिक विशेषताएं== | ||

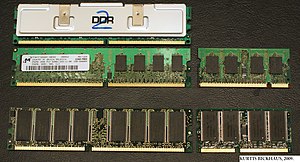

[[File:RamTypes.JPG|thumb|right|शीर्ष L-R, [[DDR2 SDRAM]] DIMM हीट-स्प्रेडर के साथ, | [[File:RamTypes.JPG|thumb|right|शीर्ष L-R, [[DDR2 SDRAM|डीडीआर-2 SDRAM]] DIMM हीट-स्प्रेडर के साथ, डीडीआर-2 DIMM बिना हीट-स्प्रेडर के, SO-DIMM डीडीआर-2, डीडीआर-, SO-DIMM डीडीआर-]]मेमोरी ज्योमेट्री रैंडम एक्सेस मेमोरी मॉड्यूल के लॉजिकल कॉन्फ़िगरेशन का वर्णन करती है लेकिन उपभोक्ताओं के लिए भौतिक कॉन्फ़िगरेशन को समझना सदैव साधारण होता है। मेमोरी ज्योमेट्री को लेकर अधिकांश भ्रम तब होता है जब भौतिक कॉन्फ़िगरेशन लॉजिकल कॉन्फ़िगरेशन को अस्पष्ट कर देता है। रैम की पहली परिभाषित विशेषता फॉर्म फैक्टर है। रैम मॉड्यूल [[लैपटॉप]], [[प्रिंटर (कंप्यूटिंग)|प्रिंटर]], एम्बेडेड कंप्यूटर और छोटे फॉर्म फैक्टर कंप्यूटर जैसे स्थान सीमित एप्लीकेशनों के लिए कॉम्पैक्ट एसओ-डीआईएमएम मॉड्यूल या [[डीआईएमएम|डीआईएमएम मॉड्यूल]] के रूप में हो सकते हैं, जिसका उपयोग प्रायः डेस्कटॉप कंप्यूटरों में किया जाता है।{{Citation needed |date=November 2015}} | ||

भौतिक परीक्षण द्वारा निर्धारित अन्य भौतिक विशेषताएँ, मेमोरी चिप्स की संख्याएँ हैं और मेमोरी स्टिक के दोनों किनारे भरे हुए होते हैं जो दो मेमोरी स्टिक की क्षमता के बराबर रैम चिप्स की संख्या वाले मॉड्यूल मेमोरी त्रुटि का पता लगाने या सुधार का समर्थन नहीं करते हैं। यदि अतिरिक्त रैम चिप्स (दो की क्षमता के बीच) हैं, तो इनका उपयोग ईसीसी के लिए किया जाता है। | |||

रैम मॉड्यूल को किनारों पर और मॉड्यूल के नीचे इंडेंटेशन द्वारा ' | रैम मॉड्यूल को किनारों पर और मॉड्यूल के नीचे इंडेंटेशन द्वारा 'कीड' किया जाता है। यह मॉड्यूल की तकनीक और वर्गीकरण को निर्दिष्ट करता है, उदाहरण के लिए यह डीडीआर-2 या डीडीआर-3 है और यह सामान्यतः डेस्कटॉप या सर्वर के लिए उपयुक्त होता है। कीड को सिस्टम में गलत मॉड्यूल को जटिल प्रकार से इंस्टॉल करने के लिए डिज़ाइन किया गया था लेकिन कुंजी में स्थित आवश्यकताओं की तुलना में अधिक आवश्यकताएं हैं। इसमे यह सुनिश्चित करना महत्वपूर्ण है कि मॉड्यूल की कुंजी उस स्लॉट की कुंजी के अनुरूप है या उसके अनुरूप नही है जिसे पर वह अधिकृत करना चाहता है। मॉड्यूल पर अतिरिक्त मेमोरी चिप्स संकेत हो सकता है जिसे सर्वरों मे हाई पावर मेमोरी सिस्टम के लिए डिजाइन किया गया था{{By whom |date=November 2015}} और मॉड्यूल बड़े पैमाने पर विणपन सिस्टम के साथ असंगत हो सकता है।{{Citation needed |date=November 2015}} | ||

चूंकि इस आलेख का अगला भाग लॉजिकल आर्किटेक्चर को सूचित करता है जो सिस्टम में प्रत्येक संख्या वाले स्लॉट में लॉजिकल स्ट्रक्चर का वर्णन करता है। स्लॉट की भौतिक विशेषताएं स्वयं महत्वपूर्ण हो जाती हैं जब मदरबोर्ड के दस्तावेज़ीकरण या बोर्ड पर लेबल स्लॉट की मूल लॉजिकल संरचना निर्धारित की जाती है।{{Citation needed |date=November 2015}} जब एक से अधिक स्लॉट होते हैं तो उन्हें क्रमांकित किया जाता है और जब एक से अधिक चैनल होते हैं तो अलग-अलग स्लॉट को भी उसी प्रकार से कोडित किया जाता है।{{Citation needed |date=November 2015}} | |||

== लॉजिकल विशेषताएं == | |||

1990 के दशक में विशेष कंप्यूटर{{Which |date=November 2015}} प्रारम्भ किए गए थे जहां दो कंप्यूटर जिनमें प्रत्येक का अपना मेमोरी कंट्रोलर होता था जिन्हें लो-लेवल नेटवर्क पर सक्रिय किया जा सकता था। सॉफ़्टवेयर चलाने के लिए किसी भी कंप्यूटर की मेमोरी या सीपीयू का उपयोग किया जा सकता था। वे सामान्यतः एक यूनिट के थे।{{clarify|date=July 2016}} इन कंप्यूटरों के लिए नॉन-यूनिफॉर्म मेमोरी आर्किटेक्चर जैसी योजनाओं का उपयोग किया जाता है।{{Citation needed |date=November 2015}}{{Citation needed |date=November 2015}} | |||

'''चैनल लोकल मेमोरी कंट्रोलर लेवल पर हाई-लेवल''' स्ट्रक्चर हैं। आधुनिक कंप्यूटर में दो, तीन या इससे भी अधिक चैनल हो सकते हैं। आमतौर पर यह महत्वपूर्ण है कि, किसी एक चैनल में प्रत्येक मॉड्यूल के लिए, अन्य आबादी वाले चैनलों में से प्रत्येक पर एक ही स्थान पर एक लॉजिकल रूप से समान मॉड्यूल हो।{{Citation needed |date=November 2015}} | |||

चैनल | |||

मॉड्यूल क्षमता एक मॉड्यूल में कुल स्थान है जिसे बाइट्स में मापा जाता है, या - अधिक सामान्यतः - शब्दों में। मॉड्यूल क्षमता रैंकों की संख्या और रैंक घनत्व के उत्पाद के बराबर है, और जहां रैंक घनत्व रैंक गहराई और रैंक चौड़ाई का उत्पाद है।<ref>{{Citation | archiveurl = https://web.archive.org/web/20110713152954/http://www.kingston.com/tools/umg/pdf/umg.pdf | publisher = Kingston | title = Ultimate Memory Guide | year = 2007 | archivedate = 2011-07-13 | url = http://www.kingston.com/tools/umg/pdf/umg.pdf }}.</ref> इस विनिर्देश को व्यक्त करने के लिए मानक प्रारूप (रैंक गहराई) एमबीटी × (रैंक चौड़ाई) × (रैंक की संख्या) है।{{Citation needed |date=November 2015}} | मॉड्यूल क्षमता एक मॉड्यूल में कुल स्थान है जिसे बाइट्स में मापा जाता है, या - अधिक सामान्यतः - शब्दों में। मॉड्यूल क्षमता रैंकों की संख्या और रैंक घनत्व के उत्पाद के बराबर है, और जहां रैंक घनत्व रैंक गहराई और रैंक चौड़ाई का उत्पाद है।<ref>{{Citation | archiveurl = https://web.archive.org/web/20110713152954/http://www.kingston.com/tools/umg/pdf/umg.pdf | publisher = Kingston | title = Ultimate Memory Guide | year = 2007 | archivedate = 2011-07-13 | url = http://www.kingston.com/tools/umg/pdf/umg.pdf }}.</ref> इस विनिर्देश को व्यक्त करने के लिए मानक प्रारूप (रैंक गहराई) एमबीटी × (रैंक चौड़ाई) × (रैंक की संख्या) है।{{Citation needed |date=November 2015}} | ||

[[मेमोरी रैंक]] एक मेमोरी मॉड्यूल की उप-इकाइयाँ हैं जो समान पते और डेटा बसों को साझा करती हैं और निम्न-स्तरीय एड्रेसिंग में चिप चयन (सीएस) द्वारा चुनी जाती हैं। उदाहरण के लिए, प्रत्येक पक्ष पर 8 चिप्स वाला एक मेमोरी मॉड्यूल, प्रत्येक चिप में 8-बिट-चौड़ा डेटा बस होता है, कुल 2 रैंक के लिए प्रत्येक पक्ष के लिए एक रैंक होगा, यदि हम एक रैंक को 64 बिट चौड़ा परिभाषित करते हैं . 128 Mib × 16 संगठन के साथ माइक्रोन टेक्नोलॉजी MT47H128M16 चिप्स से बना एक मॉड्यूल, जिसका अर्थ है 128 Mi मेमोरी गहराई और प्रति चिप 16-बिट-वाइड डेटा बस; यदि मॉड्यूल में बोर्ड के प्रत्येक तरफ इनमें से 8 चिप्स हैं, तो कुल 16 चिप्स × 16-बिट-वाइड डेटा = 256 कुल बिट्स चौड़ाई का डेटा होगा। 64-बिट-वाइड मेमोरी डेटा इंटरफ़ेस के लिए, यह 4 रैंक के बराबर है, जहां प्रत्येक रैंक को 2-बिट चिप चयन सिग्नल द्वारा चुना जा सकता है। इंटेल 945 [[चिपसेट]] जैसे मेमोरी नियंत्रक उन कॉन्फ़िगरेशन को सूचीबद्ध करते हैं जिनका वे समर्थन करते हैं: "×8 और ×16 उपकरणों के लिए 256-एमआईबी, 512-एमआईबी और 1-गीब डीडीआर2 प्रौद्योगिकियां", "512-एमआईबिट तक के सभी डीडीआर2 उपकरणों के लिए चार रैंक घनत्व", "1-गीबिट | [[मेमोरी रैंक]] एक मेमोरी मॉड्यूल की उप-इकाइयाँ हैं जो समान पते और डेटा बसों को साझा करती हैं और निम्न-स्तरीय एड्रेसिंग में चिप चयन (सीएस) द्वारा चुनी जाती हैं। उदाहरण के लिए, प्रत्येक पक्ष पर 8 चिप्स वाला एक मेमोरी मॉड्यूल, प्रत्येक चिप में 8-बिट-चौड़ा डेटा बस होता है, कुल 2 रैंक के लिए प्रत्येक पक्ष के लिए एक रैंक होगा, यदि हम एक रैंक को 64 बिट चौड़ा परिभाषित करते हैं . 128 Mib × 16 संगठन के साथ माइक्रोन टेक्नोलॉजी MT47H128M16 चिप्स से बना एक मॉड्यूल, जिसका अर्थ है 128 Mi मेमोरी गहराई और प्रति चिप 16-बिट-वाइड डेटा बस; यदि मॉड्यूल में बोर्ड के प्रत्येक तरफ इनमें से 8 चिप्स हैं, तो कुल 16 चिप्स × 16-बिट-वाइड डेटा = 256 कुल बिट्स चौड़ाई का डेटा होगा। 64-बिट-वाइड मेमोरी डेटा इंटरफ़ेस के लिए, यह 4 रैंक के बराबर है, जहां प्रत्येक रैंक को 2-बिट चिप चयन सिग्नल द्वारा चुना जा सकता है। इंटेल 945 [[चिपसेट]] जैसे मेमोरी नियंत्रक उन कॉन्फ़िगरेशन को सूचीबद्ध करते हैं जिनका वे समर्थन करते हैं: "×8 और ×16 उपकरणों के लिए 256-एमआईबी, 512-एमआईबी और 1-गीब डीडीआर2 प्रौद्योगिकियां", "512-एमआईबिट तक के सभी डीडीआर2 उपकरणों के लिए चार रैंक घनत्व", "1-गीबिट डीडीआर-2 उपकरणों के लिए आठ रैंक"। उदाहरण के तौर पर, चार [[किंग्स्टन टेक्नोलॉजी]] KHX6400D2/1G मेमोरी मॉड्यूल के साथ एक i945 मेमोरी कंट्रोलर लें, जहां प्रत्येक मॉड्यूल की क्षमता 1 [[गिबिबाइट]] है।<ref>{{Cite web |title=KHX6400D2/1G |url=https://www.kingston.com/datasheets/KHX6400D2_1G.pdf |website=Kingston Technology}}</ref> किंग्स्टन प्रत्येक मॉड्यूल को 16 "64M×8-बिट" चिप्स से बना बताता है, प्रत्येक चिप में 8-बिट-वाइड डेटा बस होती है। 16 × 8, 128 के बराबर है, इसलिए, प्रत्येक मॉड्यूल में 64 बिट्स की दो रैंक हैं। तो [[नॉर्थब्रिज (कंप्यूटिंग)]] के दृष्टिकोण से चार 1 जीबी मॉड्यूल हैं। उच्च लॉजिकल स्तर पर, एमसीएच दो चैनल भी देखता है, जिनमें से प्रत्येक में चार रैंक हैं। | ||

इसके विपरीत, बैंक, रैंक के | इसके विपरीत, बैंक, रैंक के लॉजिकल दृष्टिकोण से समान होते हुए भी, भौतिक हार्डवेयर में काफी अलग तरीके से कार्यान्वित किए जाते हैं। बैंक एक एकल मेमोरी चिप के अंदर उप-इकाइयाँ हैं, जबकि रैंक एक मॉड्यूल पर चिप्स के सबसेट से बनी उप-इकाइयाँ हैं। चिप चयन के समान, बैंकों का चयन बैंक चयन बिट्स द्वारा किया जाता है, जो मेमोरी इंटरफ़ेस का हिस्सा हैं।{{Citation needed |date=November 2015}} | ||

==संगठन का पदानुक्रम== | ==संगठन का पदानुक्रम== | ||

===मेमोरी चिप=== | ===मेमोरी चिप=== | ||

मेमोरी ज्योमेट्री द्वारा कवर किया गया संगठन का निम्नतम रूप, जिसे कभी-कभी "मेमोरी डिवाइस" भी कहा जाता है। ये घटक IC हैं जो RAM के प्रत्येक मॉड्यूल या मॉड्यूल को बनाते हैं। किसी चिप का सबसे महत्वपूर्ण माप उसका घनत्व है, जिसे बिट्स में मापा जाता है। क्योंकि मेमोरी बस की चौड़ाई आमतौर पर चिप्स की संख्या से बड़ी होती है, अधिकांश चिप्स को चौड़ाई के लिए डिज़ाइन किया जाता है, जिसका अर्थ है कि वे आंतरिक रूप से समान भागों में विभाजित होते हैं, और जब एक पते "गहराई" को बुलाया जाता है, तो केवल एक मान वापस करने के बजाय, अधिक एक से अधिक मान लौटाया जाता है। गहराई के अलावा, चिप स्तर, बैंकों पर एक दूसरा एड्रेसिंग | मेमोरी ज्योमेट्री द्वारा कवर किया गया संगठन का निम्नतम रूप, जिसे कभी-कभी "मेमोरी डिवाइस" भी कहा जाता है। ये घटक IC हैं जो RAM के प्रत्येक मॉड्यूल या मॉड्यूल को बनाते हैं। किसी चिप का सबसे महत्वपूर्ण माप उसका घनत्व है, जिसे बिट्स में मापा जाता है। क्योंकि मेमोरी बस की चौड़ाई आमतौर पर चिप्स की संख्या से बड़ी होती है, अधिकांश चिप्स को चौड़ाई के लिए डिज़ाइन किया जाता है, जिसका अर्थ है कि वे आंतरिक रूप से समान भागों में विभाजित होते हैं, और जब एक पते "गहराई" को बुलाया जाता है, तो केवल एक मान वापस करने के बजाय, अधिक एक से अधिक मान लौटाया जाता है। गहराई के अलावा, चिप स्तर, बैंकों पर एक दूसरा एड्रेसिंग डायमेंशनल जोड़ा गया है। बैंक एक बैंक को उपलब्ध होने की अनुमति देते हैं, जबकि दूसरा बैंक अनुपलब्ध है क्योंकि यह ताज़ा है।{{Citation needed |date=November 2015}} | ||

===मेमोरी मॉड्यूल=== | ===मेमोरी मॉड्यूल=== | ||

{{Main articles| | {{Main articles|मेमोरी मॉड्यूल}} | ||

मॉड्यूल के कुछ माप आकार, चौड़ाई, गति और विलंबता हैं। एक मेमोरी मॉड्यूल में वांछित मॉड्यूल चौड़ाई के बराबर कई मेमोरी चिप्स होते हैं। तो एक 32-बिट [[SIMM]] मॉड्यूल चार 8-बिट वाइड (×8) चिप्स से बना हो सकता है। जैसा कि मेमोरी चैनल भाग में बताया गया है, एक भौतिक मॉड्यूल एक या अधिक | मॉड्यूल के कुछ माप आकार, चौड़ाई, गति और विलंबता हैं। एक मेमोरी मॉड्यूल में वांछित मॉड्यूल चौड़ाई के बराबर कई मेमोरी चिप्स होते हैं। तो एक 32-बिट [[SIMM]] मॉड्यूल चार 8-बिट वाइड (×8) चिप्स से बना हो सकता है। जैसा कि मेमोरी चैनल भाग में बताया गया है, एक भौतिक मॉड्यूल एक या अधिक लॉजिकल रैंक से बना हो सकता है। यदि वह 32-बिट SIMM आठ 8-बिट चिप्स से बना होता तो SIMM की दो रैंक होती।{{Citation needed |date=November 2015}} | ||

===मेमोरी चैनल=== | ===मेमोरी चैनल=== | ||

{{See also| | {{See also|मल्टी-चैनल मेमोरी आर्किटेक्चर}} | ||

एक मेमोरी चैनल रैंकों से बना होता है। भौतिक रूप से केवल एक मेमोरी मॉड्यूल वाला एक मेमोरी चैनल खुद को एक या अधिक | |||

एक मेमोरी चैनल रैंकों से बना होता है। भौतिक रूप से केवल एक मेमोरी मॉड्यूल वाला एक मेमोरी चैनल खुद को एक या अधिक लॉजिकल रैंक के रूप में प्रस्तुत कर सकता है।{{Citation needed |date=November 2015}} | |||

===नियंत्रक संगठन=== | ===नियंत्रक संगठन=== | ||

यह उच्चतम स्तर है. एक सामान्य कंप्यूटर में केवल एक मेमोरी कंट्रोलर होता है जिसमें केवल एक या दो चैनल होते हैं। | यह उच्चतम स्तर है. एक सामान्य कंप्यूटर में केवल एक मेमोरी कंट्रोलर होता है जिसमें केवल एक या दो चैनल होते हैं। लॉजिकल विशेषता अनुभाग में NUMA कॉन्फ़िगरेशन का वर्णन किया गया है, जो मेमोरी नियंत्रकों के नेटवर्क का रूप ले सकता है। उदाहरण के लिए, दो-सॉकेट [[AMD]] K8 के प्रत्येक सॉकेट में दो-चैनल मेमोरी नियंत्रक हो सकता है, जिससे सिस्टम को कुल चार मेमोरी चैनल मिलते हैं। | ||

==मेमोरी ज्योमेट्री नोटेशन== | ==मेमोरी ज्योमेट्री नोटेशन== | ||

| Line 55: | Line 54: | ||

===चिप=== | ===चिप=== | ||

मेमोरी डेनसिटी - यह चिप की कुल मेमोरी कैपेसिटी है। | |||

128 Mib ''(memory depth) × (memory width)'' | |||

यह चिप की कुल मेमोरी | मेमोरी डेप्थ और मेमोरी डेनसिटी को मेमोरी विड्थ (चौड़ाई) से विभाजित किया जाता है। उदाहरण के लिए 128 एमआईबी और 8-बिट डेटा वाली मेमोरी चिप के लिए इसे 1(6 मेगा × 8) के रूप में निर्दिष्ट किया जा सकता है। कभी-कभी "एमआई" को 16 × 8 के रूप में निर्दिष्ट किया जाता है। | ||

''(memory depth per bank) × (memory width) × (number of banks)'' | |||

मेमोरी | |||

( | |||

उदाहरण: उपरोक्त के समान क्षमता और मेमोरी चौड़ाई वाली लेकिन 4 बैंकों के साथ निर्मित एक चिप को 4 Mi × 8 × 4 के रूप में निर्दिष्ट किया जाएगा। | उदाहरण: उपरोक्त के समान क्षमता और मेमोरी चौड़ाई वाली लेकिन 4 बैंकों के साथ निर्मित एक चिप को 4 Mi × 8 × 4 के रूप में निर्दिष्ट किया जाएगा। | ||

| Line 70: | Line 65: | ||

*[[गतिशील रैंडम एक्सेस मेमोरी|डायनामिक रैंडम एक्सेस मेमोरी]] | *[[गतिशील रैंडम एक्सेस मेमोरी|डायनामिक रैंडम एक्सेस मेमोरी]] | ||

*रैंडम एक्सेस मेमोरी | *रैंडम एक्सेस मेमोरी | ||

*[[स्मृति संगठन|मेमोरी | *[[स्मृति संगठन|मेमोरी संस्था]] | ||

*मेमोरी एड्रेस | *मेमोरी एड्रेस | ||

*मेमोरी बैंक | *मेमोरी बैंक | ||

Revision as of 11:56, 8 October 2023

This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these template messages)

(Learn how and when to remove this template message)

|

मेमोरी ज्योमेट्री आधुनिक कंप्यूटरों के डिज़ाइनों में रैंडम एक्सेस मेमोरी की आंतरिक संरचना का वर्णन करती है। मेमोरी ज्योमेट्री अपने कंप्यूटर को अपग्रेड करने वाले उपभोक्ताओं के लिए चिंता का विषय है क्योंकि पुराने मेमोरी कंट्रोलर बाद के कंप्यूटरों के साथ संगत नहीं हो सकते हैं। ओवरलैपिंग संख्या के कारण मेमोरी ज्योमेट्री टर्मिनोलॉजी भ्रमित करने वाली हो सकती है।

मेमोरी सिस्टम की ज्योमेट्री को एक मल्टी-डायमेंशनल ऐरे के रूप में समझा जा सकता है। प्रत्येक डायमेंशन की अपनी विशेषताएं और भौतिक स्थितियाँ होती है। उदाहरण के लिए मेमोरी मॉड्यूल पर डेटा पिन की संख्या एक डायमेंशन होती है।

भौतिक विशेषताएं

मेमोरी ज्योमेट्री रैंडम एक्सेस मेमोरी मॉड्यूल के लॉजिकल कॉन्फ़िगरेशन का वर्णन करती है लेकिन उपभोक्ताओं के लिए भौतिक कॉन्फ़िगरेशन को समझना सदैव साधारण होता है। मेमोरी ज्योमेट्री को लेकर अधिकांश भ्रम तब होता है जब भौतिक कॉन्फ़िगरेशन लॉजिकल कॉन्फ़िगरेशन को अस्पष्ट कर देता है। रैम की पहली परिभाषित विशेषता फॉर्म फैक्टर है। रैम मॉड्यूल लैपटॉप, प्रिंटर, एम्बेडेड कंप्यूटर और छोटे फॉर्म फैक्टर कंप्यूटर जैसे स्थान सीमित एप्लीकेशनों के लिए कॉम्पैक्ट एसओ-डीआईएमएम मॉड्यूल या डीआईएमएम मॉड्यूल के रूप में हो सकते हैं, जिसका उपयोग प्रायः डेस्कटॉप कंप्यूटरों में किया जाता है।[citation needed]

भौतिक परीक्षण द्वारा निर्धारित अन्य भौतिक विशेषताएँ, मेमोरी चिप्स की संख्याएँ हैं और मेमोरी स्टिक के दोनों किनारे भरे हुए होते हैं जो दो मेमोरी स्टिक की क्षमता के बराबर रैम चिप्स की संख्या वाले मॉड्यूल मेमोरी त्रुटि का पता लगाने या सुधार का समर्थन नहीं करते हैं। यदि अतिरिक्त रैम चिप्स (दो की क्षमता के बीच) हैं, तो इनका उपयोग ईसीसी के लिए किया जाता है।

रैम मॉड्यूल को किनारों पर और मॉड्यूल के नीचे इंडेंटेशन द्वारा 'कीड' किया जाता है। यह मॉड्यूल की तकनीक और वर्गीकरण को निर्दिष्ट करता है, उदाहरण के लिए यह डीडीआर-2 या डीडीआर-3 है और यह सामान्यतः डेस्कटॉप या सर्वर के लिए उपयुक्त होता है। कीड को सिस्टम में गलत मॉड्यूल को जटिल प्रकार से इंस्टॉल करने के लिए डिज़ाइन किया गया था लेकिन कुंजी में स्थित आवश्यकताओं की तुलना में अधिक आवश्यकताएं हैं। इसमे यह सुनिश्चित करना महत्वपूर्ण है कि मॉड्यूल की कुंजी उस स्लॉट की कुंजी के अनुरूप है या उसके अनुरूप नही है जिसे पर वह अधिकृत करना चाहता है। मॉड्यूल पर अतिरिक्त मेमोरी चिप्स संकेत हो सकता है जिसे सर्वरों मे हाई पावर मेमोरी सिस्टम के लिए डिजाइन किया गया था[by whom?] और मॉड्यूल बड़े पैमाने पर विणपन सिस्टम के साथ असंगत हो सकता है।[citation needed]

चूंकि इस आलेख का अगला भाग लॉजिकल आर्किटेक्चर को सूचित करता है जो सिस्टम में प्रत्येक संख्या वाले स्लॉट में लॉजिकल स्ट्रक्चर का वर्णन करता है। स्लॉट की भौतिक विशेषताएं स्वयं महत्वपूर्ण हो जाती हैं जब मदरबोर्ड के दस्तावेज़ीकरण या बोर्ड पर लेबल स्लॉट की मूल लॉजिकल संरचना निर्धारित की जाती है।[citation needed] जब एक से अधिक स्लॉट होते हैं तो उन्हें क्रमांकित किया जाता है और जब एक से अधिक चैनल होते हैं तो अलग-अलग स्लॉट को भी उसी प्रकार से कोडित किया जाता है।[citation needed]

लॉजिकल विशेषताएं

1990 के दशक में विशेष कंप्यूटर[which?] प्रारम्भ किए गए थे जहां दो कंप्यूटर जिनमें प्रत्येक का अपना मेमोरी कंट्रोलर होता था जिन्हें लो-लेवल नेटवर्क पर सक्रिय किया जा सकता था। सॉफ़्टवेयर चलाने के लिए किसी भी कंप्यूटर की मेमोरी या सीपीयू का उपयोग किया जा सकता था। वे सामान्यतः एक यूनिट के थे।[clarification needed] इन कंप्यूटरों के लिए नॉन-यूनिफॉर्म मेमोरी आर्किटेक्चर जैसी योजनाओं का उपयोग किया जाता है।[citation needed][citation needed]

चैनल लोकल मेमोरी कंट्रोलर लेवल पर हाई-लेवल स्ट्रक्चर हैं। आधुनिक कंप्यूटर में दो, तीन या इससे भी अधिक चैनल हो सकते हैं। आमतौर पर यह महत्वपूर्ण है कि, किसी एक चैनल में प्रत्येक मॉड्यूल के लिए, अन्य आबादी वाले चैनलों में से प्रत्येक पर एक ही स्थान पर एक लॉजिकल रूप से समान मॉड्यूल हो।[citation needed]

मॉड्यूल क्षमता एक मॉड्यूल में कुल स्थान है जिसे बाइट्स में मापा जाता है, या - अधिक सामान्यतः - शब्दों में। मॉड्यूल क्षमता रैंकों की संख्या और रैंक घनत्व के उत्पाद के बराबर है, और जहां रैंक घनत्व रैंक गहराई और रैंक चौड़ाई का उत्पाद है।[1] इस विनिर्देश को व्यक्त करने के लिए मानक प्रारूप (रैंक गहराई) एमबीटी × (रैंक चौड़ाई) × (रैंक की संख्या) है।[citation needed]

मेमोरी रैंक एक मेमोरी मॉड्यूल की उप-इकाइयाँ हैं जो समान पते और डेटा बसों को साझा करती हैं और निम्न-स्तरीय एड्रेसिंग में चिप चयन (सीएस) द्वारा चुनी जाती हैं। उदाहरण के लिए, प्रत्येक पक्ष पर 8 चिप्स वाला एक मेमोरी मॉड्यूल, प्रत्येक चिप में 8-बिट-चौड़ा डेटा बस होता है, कुल 2 रैंक के लिए प्रत्येक पक्ष के लिए एक रैंक होगा, यदि हम एक रैंक को 64 बिट चौड़ा परिभाषित करते हैं . 128 Mib × 16 संगठन के साथ माइक्रोन टेक्नोलॉजी MT47H128M16 चिप्स से बना एक मॉड्यूल, जिसका अर्थ है 128 Mi मेमोरी गहराई और प्रति चिप 16-बिट-वाइड डेटा बस; यदि मॉड्यूल में बोर्ड के प्रत्येक तरफ इनमें से 8 चिप्स हैं, तो कुल 16 चिप्स × 16-बिट-वाइड डेटा = 256 कुल बिट्स चौड़ाई का डेटा होगा। 64-बिट-वाइड मेमोरी डेटा इंटरफ़ेस के लिए, यह 4 रैंक के बराबर है, जहां प्रत्येक रैंक को 2-बिट चिप चयन सिग्नल द्वारा चुना जा सकता है। इंटेल 945 चिपसेट जैसे मेमोरी नियंत्रक उन कॉन्फ़िगरेशन को सूचीबद्ध करते हैं जिनका वे समर्थन करते हैं: "×8 और ×16 उपकरणों के लिए 256-एमआईबी, 512-एमआईबी और 1-गीब डीडीआर2 प्रौद्योगिकियां", "512-एमआईबिट तक के सभी डीडीआर2 उपकरणों के लिए चार रैंक घनत्व", "1-गीबिट डीडीआर-2 उपकरणों के लिए आठ रैंक"। उदाहरण के तौर पर, चार किंग्स्टन टेक्नोलॉजी KHX6400D2/1G मेमोरी मॉड्यूल के साथ एक i945 मेमोरी कंट्रोलर लें, जहां प्रत्येक मॉड्यूल की क्षमता 1 गिबिबाइट है।[2] किंग्स्टन प्रत्येक मॉड्यूल को 16 "64M×8-बिट" चिप्स से बना बताता है, प्रत्येक चिप में 8-बिट-वाइड डेटा बस होती है। 16 × 8, 128 के बराबर है, इसलिए, प्रत्येक मॉड्यूल में 64 बिट्स की दो रैंक हैं। तो नॉर्थब्रिज (कंप्यूटिंग) के दृष्टिकोण से चार 1 जीबी मॉड्यूल हैं। उच्च लॉजिकल स्तर पर, एमसीएच दो चैनल भी देखता है, जिनमें से प्रत्येक में चार रैंक हैं।

इसके विपरीत, बैंक, रैंक के लॉजिकल दृष्टिकोण से समान होते हुए भी, भौतिक हार्डवेयर में काफी अलग तरीके से कार्यान्वित किए जाते हैं। बैंक एक एकल मेमोरी चिप के अंदर उप-इकाइयाँ हैं, जबकि रैंक एक मॉड्यूल पर चिप्स के सबसेट से बनी उप-इकाइयाँ हैं। चिप चयन के समान, बैंकों का चयन बैंक चयन बिट्स द्वारा किया जाता है, जो मेमोरी इंटरफ़ेस का हिस्सा हैं।[citation needed]

संगठन का पदानुक्रम

मेमोरी चिप

मेमोरी ज्योमेट्री द्वारा कवर किया गया संगठन का निम्नतम रूप, जिसे कभी-कभी "मेमोरी डिवाइस" भी कहा जाता है। ये घटक IC हैं जो RAM के प्रत्येक मॉड्यूल या मॉड्यूल को बनाते हैं। किसी चिप का सबसे महत्वपूर्ण माप उसका घनत्व है, जिसे बिट्स में मापा जाता है। क्योंकि मेमोरी बस की चौड़ाई आमतौर पर चिप्स की संख्या से बड़ी होती है, अधिकांश चिप्स को चौड़ाई के लिए डिज़ाइन किया जाता है, जिसका अर्थ है कि वे आंतरिक रूप से समान भागों में विभाजित होते हैं, और जब एक पते "गहराई" को बुलाया जाता है, तो केवल एक मान वापस करने के बजाय, अधिक एक से अधिक मान लौटाया जाता है। गहराई के अलावा, चिप स्तर, बैंकों पर एक दूसरा एड्रेसिंग डायमेंशनल जोड़ा गया है। बैंक एक बैंक को उपलब्ध होने की अनुमति देते हैं, जबकि दूसरा बैंक अनुपलब्ध है क्योंकि यह ताज़ा है।[citation needed]

मेमोरी मॉड्यूल

मॉड्यूल के कुछ माप आकार, चौड़ाई, गति और विलंबता हैं। एक मेमोरी मॉड्यूल में वांछित मॉड्यूल चौड़ाई के बराबर कई मेमोरी चिप्स होते हैं। तो एक 32-बिट SIMM मॉड्यूल चार 8-बिट वाइड (×8) चिप्स से बना हो सकता है। जैसा कि मेमोरी चैनल भाग में बताया गया है, एक भौतिक मॉड्यूल एक या अधिक लॉजिकल रैंक से बना हो सकता है। यदि वह 32-बिट SIMM आठ 8-बिट चिप्स से बना होता तो SIMM की दो रैंक होती।[citation needed]

मेमोरी चैनल

एक मेमोरी चैनल रैंकों से बना होता है। भौतिक रूप से केवल एक मेमोरी मॉड्यूल वाला एक मेमोरी चैनल खुद को एक या अधिक लॉजिकल रैंक के रूप में प्रस्तुत कर सकता है।[citation needed]

नियंत्रक संगठन

यह उच्चतम स्तर है. एक सामान्य कंप्यूटर में केवल एक मेमोरी कंट्रोलर होता है जिसमें केवल एक या दो चैनल होते हैं। लॉजिकल विशेषता अनुभाग में NUMA कॉन्फ़िगरेशन का वर्णन किया गया है, जो मेमोरी नियंत्रकों के नेटवर्क का रूप ले सकता है। उदाहरण के लिए, दो-सॉकेट AMD K8 के प्रत्येक सॉकेट में दो-चैनल मेमोरी नियंत्रक हो सकता है, जिससे सिस्टम को कुल चार मेमोरी चैनल मिलते हैं।

मेमोरी ज्योमेट्री नोटेशन

मेमोरी ज्योमेट्री को निर्दिष्ट करने के विभिन्न तरीकों का सामना किया जा सकता है, जो विभिन्न प्रकार की जानकारी देते हैं।

मॉड्यूल

(मेमोरी गहराई) × (मेमोरी चौड़ाई)

मेमोरी चौड़ाई बिट्स में मेमोरी मॉड्यूल इंटरफ़ेस की डेटा चौड़ाई निर्दिष्ट करती है। उदाहरण के लिए, 64 64-बिट डेटा चौड़ाई को इंगित करेगा, जैसा कि रैम के एसडीआर और डीडीआर1-4 परिवारों में आम गैर-ईसीसी डीआईएमएम पर पाया जाता है। 72 की चौड़ाई वाली मेमोरी एक ईसीसी मॉड्यूल को इंगित करेगी, जिसमें त्रुटि-सुधार कोड सिंड्रोम के लिए डेटा चौड़ाई में 8 अतिरिक्त बिट्स होंगे। (ईसीसी सिंड्रोम एकल-बिट त्रुटियों को ठीक करने की अनुमति देता है)। मेमोरी गहराई गैर-समता मेमोरी चौड़ाई से विभाजित बिट्स में कुल मेमोरी क्षमता है। कभी-कभी मेमोरी की गहराई मेग (220) की इकाइयों में इंगित की जाती है, जैसे 32×64 या 64×64, जो क्रमशः 32 एमआई गहराई और 64 एमआई गहराई का संकेत देती है।

चिप

मेमोरी डेनसिटी - यह चिप की कुल मेमोरी कैपेसिटी है।

128 Mib (memory depth) × (memory width)

मेमोरी डेप्थ और मेमोरी डेनसिटी को मेमोरी विड्थ (चौड़ाई) से विभाजित किया जाता है। उदाहरण के लिए 128 एमआईबी और 8-बिट डेटा वाली मेमोरी चिप के लिए इसे 1(6 मेगा × 8) के रूप में निर्दिष्ट किया जा सकता है। कभी-कभी "एमआई" को 16 × 8 के रूप में निर्दिष्ट किया जाता है।

(memory depth per bank) × (memory width) × (number of banks)

उदाहरण: उपरोक्त के समान क्षमता और मेमोरी चौड़ाई वाली लेकिन 4 बैंकों के साथ निर्मित एक चिप को 4 Mi × 8 × 4 के रूप में निर्दिष्ट किया जाएगा।

यह भी देखें

- डीआईएमएम

- डिवाइस बैंडविड्थ की सूची

- डायनामिक रैंडम एक्सेस मेमोरी

- रैंडम एक्सेस मेमोरी

- मेमोरी संस्था

- मेमोरी एड्रेस

- मेमोरी बैंक

- बैंक स्विचिंग

- दो तरफा रैम

- दोहरे चैनल आर्किटेक्चर

- पेज एड्रेस रजिस्टर

संदर्भ

- ↑ Ultimate Memory Guide (PDF), Kingston, 2007, archived from the original (PDF) on 2011-07-13.

- ↑ "KHX6400D2/1G" (PDF). Kingston Technology.

बाहरी

- "RAM", Mainboard (FAQ), IXT labs, 2006.

- FAQ, RAMpedia, archived from the original on 2010-05-16.

- "Part 1", RAM guide, Ars technica.

- "Banks", RAM, PC guide.

- KHX6400D2 1G (PDF) (data sheet), Value RAM, archived from the original (PDF) on 2012-03-10, retrieved 2010-08-05.

- 307502 (PDF) (data sheet), Intel.

श्रेणी:कंप्यूटिंग शब्दावली श्रेणी:कंप्यूटर मेमोरी