फ्लैश एडीसी

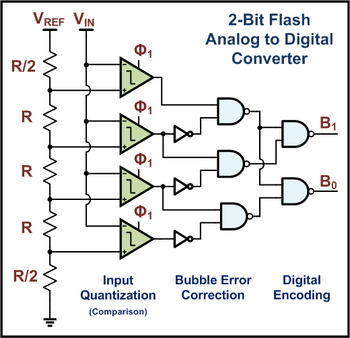

फ्लैश एडीसी (प्रत्यक्ष-रूपांतरण एडीसी के रूप में भी जाना जाता है) एक प्रकार का एनॉलॉग से डिजिटल परिवर्तित करने वाला उपकरण है जो इनपुट वोल्टेज की तुलना क्रमिक संदर्भ वोल्टेज से करने के लिए लैडर के प्रत्येक पायदान पर तुलनित्र के साथ रैखिक वोल्टेज लैडर का उपयोग करता है। अधिकांश ये संदर्भ लैडर कई प्रतिरोधों से निर्मित होती हैं; चूँकि, आधुनिक कार्यान्वयन से पता चलता है कि धारिता वोल्टेज विभाजन भी संभव है। इन तुलनित्रों के आउटपुट को सामान्यतः डिजिटल एनकोडर में फीड किया जाता है, जो इनपुट को बाइनरी मान (तुलनित्रों से एकत्रित आउटपुट को यूनरी अंक प्रणाली मान के रूप में माना जा सकता है) में परिवर्तित करता है।

लाभ और कमियां

फ्लैश कन्वर्टर्स कई अन्य एडीसी की तुलना में उच्च गति वाले होते हैं, जो सामान्यतः चरणों की एक श्रृंखला में सही उत्तर पर संकीर्ण होते हैं। चूँकि, इनकी तुलना में एक फ्लैश कन्वर्टर भी काफी सरल है और, एनालॉग तुलनित्रों के अतिरिक्त, बाइनरी अंक प्रणाली में अंतिम रूपांतरण के लिए केवल डिजिटल इलेक्ट्रॉनिक्स की आवश्यकता होती है।

सर्वोत्तम शुद्धता के लिए, एक ट्रैक-एंड-होल्ड परिपथ अधिकांश एडीसी इनपुट के सामने डाला जाता है। यह कई एडीसी प्रकारों (जैसे क्रमिक सन्निकटन एडीसी) के लिए आवश्यक है, किन्तु फ्लैश एडीसी के लिए इसकी कोई वास्तविक आवश्यकता नहीं है, क्योंकि तुलनित्र नमूना उपकरण हैं।

एक फ्लैश कनवर्टर को अन्य एडीसी की तुलना में विशेष रूप से शुद्धता बढ़ने के साथ बड़ी संख्या में तुलनित्रों की आवश्यकता होती है। उदाहरण के लिए, एक फ्लैश कन्वर्टर को n-बिट रूपांतरण के लिए तुलनित्र की आवश्यकता होती है। उन सभी तुलनित्रों का आकार, विद्युत का व्यय और लागत फ्लैश कन्वर्टर्स को सामान्यतः 8 बिट्स (255 तुलनित्र) से अधिक शुद्धता के लिए अव्यावहारिक बनाती है। इन तुलनित्रों के स्थान पर, अधिकांश अन्य एडीसी अधिक जटिल डिजिटल परिपथ और/या एनालॉग सर्किट्री को प्रतिस्थापित करते हैं जिन्हें बढ़ी हुई शुद्धता और शुद्धता के लिए अधिक आसानी से बढ़ाया जा सकता है।

कार्यान्वयन

फ्लैश एडीसी को कई तकनीकों में लागू किया गया है, जो सिलिकॉन-आधारित द्विध्रुवी जंक्शन ट्रांजिस्टर (बीजेटी) और पूरक धातु-ऑक्साइड फील्ड इफ़ेक्ट ट्रांजिस्टर (सीएमओएस) प्रौद्योगिकियों से लेकर शायद ही कभी उपयोग की जाने वाली सेमीकंडक्टर सामग्री की सूची|III-V प्रौद्योगिकियों से भिन्न हैं। अधिकांश इस प्रकार के एडीसी का उपयोग पहले मध्यम आकार के एनालॉग परिपथ सत्यापन के रूप में किया जाता है।

शुरुआती कार्यान्वयन में संदर्भ वोल्टेज से जुड़े अच्छी तरह से मेल खाने वाले प्रतिरोधों की संदर्भ लैडर शामिल थी। रोकनेवाला लैडर पर प्रत्येक नल तुलनित्र के लिए उपयोग किया जाता है, संभवतः एम्पलीफायर चरण से पहले होता है, और इस प्रकार मापा वोल्टेज वोल्टेज विभक्त के वोल्टेज संदर्भ से ऊपर या नीचे के आधार पर तार्किक 0 या 1 उत्पन्न करता है। एम्पलीफायर जोड़ने का कारण दुगना है: यह वोल्टेज अंतर को बढ़ाता है और इसलिए तुलनित्र ऑफसेट को दबा देता है, और संदर्भ लैडर की ओर तुलनित्र के किक-बैक शोर को भी दृढ़ता से दबा दिया जाता है। विशिष्ट रूप से 4-बिट से 6-बिट तक और कभी-कभी 7-बिट से डिजाइन तैयार किए जाते हैं।

विद्युत की बचत धारिता रेफरेंस लैडर के साथ डिजाइन का प्रदर्शन किया गया है। तुलनित्र को क्लॉक करने के अतिरिक्त, ये सिस्टम इनपुट चरण पर संदर्भ मान का नमूना भी लेते हैं। जैसा कि नमूनाकरण बहुत उच्च दर पर किया जाता है, कैपेसिटर का रिसाव नगण्य होता है।

हाल ही में, ऑफसेट अंशांकन को फ्लैश एडीसी डिजाइनों में पेश किया गया है। उच्च-परिशुद्धता एनालॉग परिपथ (जो भिन्नता को दबाने के लिए घटक आकार को बढ़ाते हैं) के बजाय अपेक्षाकृत बड़ी ऑफसेट त्रुटियों वाले तुलनित्रों को मापा और समायोजित किया जाता है। परीक्षण संकेत लागू किया जाता है, और प्रत्येक तुलनित्र के ऑफसेट को एडीसी के कम महत्वपूर्ण बिट मान से नीचे कैलिब्रेट किया जाता है।

कई फ्लैश एडीसी में और सुधार डिजिटल त्रुटि सुधार को शामिल करना है। जब ADC का उपयोग कठोर वातावरण में किया जाता है या बहुत छोटी एकीकृत परिपथ प्रक्रियाओं से निर्मित होता है, तो बड़ा जोखिम होता है कि एकल तुलनित्र बेतरतीब ढंग से राज्य को बदल देगा जिसके परिणामस्वरूप गलत कोड होगा। बबल एरर करेक्शन डिजिटल करेक्शन मैकेनिज्म है जो तुलनित्र को रोकता है, उदाहरण के लिए, लॉजिक हाई रिपोर्टिंग से हाई ट्रिप हो गया है, अगर यह तुलनित्रों से घिरा हुआ है जो लॉजिक को कम रिपोर्ट कर रहे हैं।

तह एडीसी

तुलनित्रों की संख्या को सामने फोल्डिंग परिपथ जोड़कर, तथाकथित फोल्डिंग एडीसी बनाकर कुछ हद तक कम किया जा सकता है। रैंप इनपुट सिग्नल के दौरान केवल बार फ्लैश एडीसी में तुलनित्रों का उपयोग करने के बजाय, फोल्डिंग एडीसी तुलनित्रों का कई बार पुन: उपयोग करता है। यदि n-बिट ADC में m-गुना फोल्डिंग परिपथ का उपयोग किया जाता है, तो तुलनित्र की वास्तविक संख्या को कम किया जा सकता है को (रेंज क्रॉसओवर का पता लगाने के लिए हमेशा की जरूरत होती है)। विशिष्ट फोल्डिंग परिपथ गिल्बर्ट सेल और एनालॉग या गेट#वायर्ड-ओआर|वायर्ड-ओआर परिपथ हैं।

आवेदन

इस प्रकार के एडीसी की बहुत उच्च नमूना दर राडार पहचान, अल्ट्रा वाइड बैंड रिसीवर, इलेक्ट्रॉनिक परीक्षण उपकरण और ऑप्टिकल संचार लिंक जैसे उच्च-आवृत्ति अनुप्रयोगों (सामान्यतः कुछ गीगाहर्ट्ज रेंज में) को सक्षम बनाती है। अधिक बार फ्लैश एडीसी बड़े एकीकृत परिपथ में एम्बेडेड होता है जिसमें कई डिजिटल डिकोडिंग फ़ंक्शन होते हैं।

डेल्टा-सिग्मा मॉड्यूलेशन लूप के अंदर छोटा फ्लैश एडीसी परिपथ भी मौजूद हो सकता है।

फ्लैश एडीसी का उपयोग एनएएनडी फ्लैश मेमोरी में भी किया जाता है, जहां फ्लोटिंग गेट्स पर 8 वोल्टेज स्तर के रूप में प्रति मेमोरी सेल (कंप्यूटिंग) में 3 बिट तक संग्रहीत किया जाता है।

संदर्भ

- Analog-to-Digital Conversion

- Understanding Flash ADCs

- "Integrated Analog-to-Digital and Digital-to-Analog Converters", R. van de Plassche, ADCs, Kluwer Academic Publishers, 1994.

- "A Precise Four-Quadrant Multiplier with Subnanosecond Response", Barrie Gilbert, IEEE Journal of Solid-State Circuits, Vol. 3, No. 4 (1968), pp. 365–373