फ्रीक्वेंसी डिवाइडर

आवृत्ति डिवाइडर जिसे क्लॉक डिवाइडर या स्केलर या प्रीस्केलर भी कहा जाता है एक विद्युत परिपथ है जो आवृत्ति का इनपुट संकेत लेता है, , और आवृत्ति का आउटपुट संकेत उत्पन्न करता है:

जहाँ एक पूर्णांक है। चरण बंद लूप आवृत्ति सिंथेसाइज़र आवृत्ति डिवाइडर का उपयोग एक आवृत्ति उत्पन्न करने के लिए करते हैं जो एक संदर्भ आवृत्ति का गुणक होता है। आवृत्ति डिवाइडर को एनालॉग इलेक्ट्रॉनिक्स और डिजिटल डाटा एप्लिकेशन दोनों के लिए प्रयुक्त किया जा सकता है।

एनालॉग

एनालॉग आवृत्ति डिवाइडर कम समान्य हैं और केवल बहुत उच्च आवृत्तियों पर उपयोग किए जाते हैं। आधुनिक आईसी प्रौद्योगिकियों में प्रयुक्त डिजिटल डिवाइडर दसियों गीगाहर्ट्ज तक काम कर सकते हैं।

पुनर्योजी

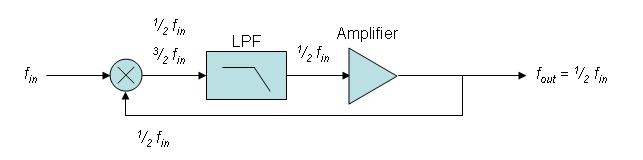

पुनर्योजी आवृत्ति विभाजक जिसे मिलर आवृत्ति विभाजक के रूप में भी जाना जाता है[1] मिक्सर से फीडबैक संकेत के साथ इनपुट संकेत को मिलाता है।

प्रतिक्रिया संकेत है। यह योग और अंतर आवृत्तियों का उत्पादन करता है , मिक्सर के आउटपुट पर एक कम पास फिल्टर उच्च आवृत्ति को हटा देता है और आवृत्ति को बढ़ाया जाता है और मिक्सर में वापस फीड किया जाता है।

इंजेक्शन-लॉक

एक फ्री-रनिंग ऑसिलेटर जिसके पास उच्च-आवृत्ति संकेत की थोड़ी मात्रा होती है वह इनपुट संकेत के साथ दोलन करता है। टेलीविजन के विकास में ऐसे आवृत्ति डिवाइडर आवश्यक थे।

यह एक इंजेक्शन बंद ऑसिलेटर के समान काम करता है। एक इंजेक्शन लॉक आवृत्ति डिवाइडर में इनपुट संकेत की आवृत्ति ऑसिलेटर की फ्री-रनिंग आवृत्ति की मल्टीपल (या अंश) होती है। जबकि ये आवृत्ति डिवाइडर ब्रॉडबैंड स्टैटिक (या फ़्लिप-फ़्लॉप आधारित) आवृत्ति डिवाइडर की तुलना में कम शक्ति वाले होते हैं दोष उनकी कम लॉकिंग सीमा है। आईएलएफडी लॉकिंग सीमा ऑसिलेटर टैंक के गुणवत्ता कारक (Q) के व्युत्क्रमानुपाती होती है। एकीकृत परिपथ डिजाइनों में, यह आईएलएफडी को प्रक्रिया विविधताओं के प्रति संवेदनशील बनाता है। ड्राइविंग परिपथ की ट्यूनिंग सीमा सुनिश्चित करने के लिए देखभाल की जानी चाहिए (उदाहरण के लिए वोल्टेज-नियंत्रित ऑसीलेटर) आईएलएफडी की इनपुट लॉकिंग सीमा के अंदर आना चाहिए।

डिजिटल

पावर-ऑफ़-2 पूर्णांक विभाजन के लिए एक साधारण बाइनरी काउंटर का उपयोग किया जा सकता है, जिसे इनपुट संकेत द्वारा क्लॉक किया जाता है। कम से कम महत्वपूर्ण आउटपुट बिट इनपुट क्लॉक की दर के 1/2 पर वैकल्पिक होता है अगला बिट 1/4 दर पर तीसरा बिट 1/8 दर पर आदि। फ्लिप-फ्लॉप (इलेक्ट्रॉनिक्स) की व्यवस्था है पूर्णांक-एन विभाजन के लिए एक क्लासिक विधि ऐसा विभाजन तापमान सहित पर्यावरणीय विविधताओं पर स्रोत के लिए आवृत्ति और चरण सुसंगत है। सबसे आसान विन्यास एक श्रृंखला है जहां प्रत्येक फ्लिप-फ्लॉप एक विभाजित-दर-2 है। इनमें से तीन की एक श्रृंखला के लिए ऐसी प्रणाली एक विभाजित-8 होगी। फ्लिप फ्लॉप की श्रृंखला में अतिरिक्त लॉजिक गेट जोड़कर अन्य विभाजन अनुपात प्राप्त किए जा सकते हैं। एकीकृत परिपथ तर्क परिवार कुछ सामान्य विभाजन अनुपातों के लिए एकल चिप समाधान प्रदान कर सकते हैं।

एक अन्य लोकप्रिय परिपथ एक डिजिटल संकेत को एक सम पूर्णांक गुणक से विभाजित करने के लिए एक जॉनसन काउंटर है। यह एक प्रकार का शिफ्ट का रजिस्टर नेटवर्क है जिसे इनपुट संकेत द्वारा क्लॉक किया जाता है। अंतिम रजिस्टर का पूरक आउटपुट पहले रजिस्टर के इनपुट पर वापस आ जाता है। आउटपुट संकेत एक या अधिक रजिस्टर आउटपुट से प्राप्त होता है। उदाहरण के लिए, एक 3-रजिस्टर जॉनसन काउंटर के साथ एक डिवाइड-बाय-6 डिवाइडर का निर्माण किया जा सकता है। काउंटर के छह वैध मान 000, 100, 110, 111, 011 और 001 हैं। यह पैटर्न हर बार दोहराता है जब नेटवर्क को इनपुट संकेत द्वारा देखा जाता है। रजिस्टरों के बीच 120 डिग्री फेज शिफ्ट के साथ प्रत्येक रजिस्टर का आउटपुट f/6 स्क्वायर वेव है। अतिरिक्त पूर्णांक विभाजक प्रदान करने के लिए अतिरिक्त रजिस्टर जोड़े जा सकते हैं।

मिश्रित संकेत

(वर्गीकरण: अतुल्यकालिक परिपथ अनुक्रमिक तर्क)

पूर्णांक-एन विभाजन के लिए डी फ्लिप-फ्लॉप की व्यवस्था एक क्लासिक विधि है। ऐसा विभाजन तापमान सहित पर्यावरणीय विविधताओं पर स्रोत के लिए आवृत्ति और चरण सुसंगत है। सबसे आसान विन्यास एक श्रृंखला है जहां प्रत्येक डी फ्लिप-फ्लॉप एक विभाजित-दर-2 है। इनमें से तीन की एक श्रृंखला के लिए, ऐसी प्रणाली एक विभाजित-8 होगी। अधिक जटिल विन्यास पाए गए हैं जो विषम कारकों को उत्पन्न करते हैं जैसे कि विभाजित-बाय-5 मानक क्लासिक लॉजिक चिप्स जो इस या समान आवृत्ति विभाजन कार्यों को प्रयुक्त करते हैं उनमें 7456, 7457, 74292, और 74294 सम्मिलित हैं। (7400 श्रृंखला एकीकृत परिपथ की सूची और 4000 श्रृंखला एकीकृत परिपथ लॉजिक चिप्स की सूची देखें)

आंशिक-एन संश्लेषण

एक आंशिक-एन आवृत्ति सिंथेसाइज़र दो पूर्णांक डिवाइडर एक डिवाइड-बाय-एन और एक डिवाइड-बाय-(एन + 1) आवृत्ति डिवाइडर का उपयोग करके बनाया जा सकता है। मापांक नियंत्रक के साथ, n को दो मानों के बीच टॉगल किया जाता है जिससे वोल्टेज-नियंत्रित ऑसिलेटर एक बंद आवृत्ति और दूसरे के बीच वैकल्पिक हो वीसीओ एक आवृत्ति पर स्थिर होता है जो कि दो बंद आवृत्तियों का समय औसत है। आवृत्ति डिवाइडर द्वारा दो डिवाइडर मूल्यों पर खर्च किए जाने वाले समय के प्रतिशत को अलग-अलग करके लॉक किए गए वीसीओ की आवृत्ति को बहुत समीप ग्रैन्युलैरिटी के साथ चुना जा सकता है।

डेल्टा-सिग्मा

यदि n द्वारा विभाजित करने और (n + 1) द्वारा विभाजित करने का क्रम आवधिक है, तो वांछित आवृत्ति के अतिरिक्त वीसीओ आउटपुट में नकली संकेत दिखाई देते हैं। डेल्टा-सिग्मा भिन्नात्मक-एन डिवाइडर समय-औसत अनुपात को बनाए रखते हुए, एन और (एन + 1) के चयन को यादृच्छिक बनाकर इस समस्या को दूर करते हैं।

है जहां प्रत्येक डी फ्लिप-फ्लॉप एक विभाजित-दर-2 है। इनमें से तीन की एक श्रृंखला के लिए, ऐसी प्रणाली एक विभाजित-8 होगी। अधिक जटिल विन्यास पाए गए हैं जो विषम कारकों को उत्पन्न करते हैं जैसे कि विभाजित-बाय-5 मानक क्लासिक लॉजिक

यह भी देखें

- चरण बंद लूप

- प्रीस्कूलर

- पल्स-निगलने वाला काउंटर और पल्स-निगलने वाला डिवाइडर

संदर्भ

- ↑ R. L. Miller (1939). "पुनर्योजी मॉड्यूलेशन का उपयोग करते हुए आंशिक आवृत्ति जेनरेटर". Proceedings of the IRE. 27 (7): 446–457. doi:10.1109/JRPROC.1939.228513.