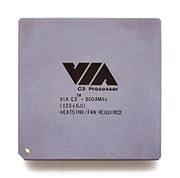

वीआईए C3

| |

| General information | |

|---|---|

| Launched | 2001 |

| Common manufacturer(s) |

|

| Performance | |

| Max. CPU clock rate | 500 MHz to 1.4 GHz |

| FSB speeds | 100 MHz to 133 MHz |

| Cache | |

| L1 cache | 64 KiB instruction + 64 KiB data |

| L2 cache | 64 KiB |

| Architecture and classification | |

| Technology node | 0.13 to 0.15 |

| Instruction set | x86 |

| Physical specifications | |

| Cores |

|

| Socket(s) |

|

| Products, models, variants | |

| Core name(s) |

|

| History | |

| Predecessor | Cyrix III |

| Successor | VIA C7 |

VIA C3 Centaur Technology द्वारा डिज़ाइन किए गए और VIA Technologies द्वारा बेचे गए व्यक्तिगत कंप्यूटरों के लिए x86 केंद्रीय प्रसंस्करण इकाइयों का परिवार है। विभिन्न CPU कोर Centaur Technology#Design पद्धति के अनुसार बनाए गए हैं।

X86 निर्देशों के अलावा, VIA C3 CPUs में गैर-दस्तावेजी वैकल्पिक निर्देश सेट होता है जो CPU तक निम्न-स्तर की पहुंच और कुछ मामलों में विशेषाधिकार वृद्धि की अनुमति देता है।[1]

कोर

शमूएल 2 और एज्रा कोर

उन्नत शमूएल 2 (C5B) कोर में स्विच के साथ साइरिक्स III का नाम बदलकर VIA C3 कर दिया गया। ऑन-डाई CPU कैश जोड़ने से प्रदर्शन में कुछ सुधार हुआ।[2] चूंकि यह सिरिक्स तकनीक पर बिल्कुल भी नहीं बनाया गया था, नया नाम सिर्फ एक तार्किक कदम था। बिजली की खपत में सुधार करने और निर्माण लागत को कम करने के लिए, सैमुअल 2 को 150 एनएम प्रोसेस टेक्नोलॉजी के साथ तैयार किया गया था।

VIA C3 प्रोसेसर ने बिजली की खपत को कम करने पर जोर देना जारी रखा और अगली डाई सिकुड़ कर मिश्रित 130/150 nm प्रक्रिया में बदल गई। एज्रा (सी5सी) और एज्रा-टी (सी5एन) इंटेल के पेंटियम III ट्यूलैटिन कोर के साथ संगतता से मेल खाने के लिए एज्रा-टी के बस प्रोटोकॉल में कुछ मामूली संशोधनों के साथ सैमुअल 2 कोर के केवल नए संशोधन थे। कई वर्षों तक VIA ने x86 CPU बाजार में सबसे कम बिजली का उपयोग किया। हालाँकि, डिजाइन में सुधार की कमी के कारण प्रदर्शन पिछड़ गया।[3]

विशिष्ट रूप से, खुदरा C3 CPU टिन का बॉक्स के अंदर भेज दिया जाता है।[3]

नहेमायाह कोर

नहेमायाह (C5XL) प्रमुख मूल संशोधन था। उस समय, वीआईए के विपणन प्रयासों में हुए परिवर्तनों को पूरी तरह से प्रतिबिंबित नहीं किया गया था। कंपनी ने पुराने कोर की कई डिजाइन कमियों को दूर किया, जिसमें हाफ-स्पीड फ्लोटिंग-पॉइंट यूनिट भी शामिल है। घड़ी की गति में निरंतर वृद्धि की अनुमति देने के लिए पाइपलाइन चरणों की संख्या 12 से बढ़ाकर 16 कर दी गई। इसके अतिरिक्त, इसने cmov निर्देश को लागू किया, जिससे यह 686-श्रेणी का प्रोसेसर बन गया। लिनक्स कर्नेल इस कोर को C3-2 के रूप में संदर्भित करता है। यह 3DNow को भी हटा देता है! स्ट्रीमिंग SIMD एक्सटेंशन लागू करने के पक्ष में निर्देश। हालांकि, यह अभी भी पुराने सॉकेट 370 पर आधारित था, जो सिर्फ 133 मेगाहर्ट्ज पर पम्पिंग (कंप्यूटर सिस्टम) सामने की ओर बस चला रहा था।

क्योंकि एम्बेडेड सिस्टम मार्केटप्लेस कम-शक्ति, कम लागत वाले CPU डिज़ाइनों को पसंद करता है, VIA ने इस सेगमेंट को अधिक आक्रामक रूप से लक्षित करना शुरू किया क्योंकि C3 उन लक्षणों को अच्छी तरह से फिट करता है। Centaur Technology एम्बेडेड मार्केटप्लेस के लिए आकर्षक सुविधाओं को जोड़ने पर केंद्रित है। पहले नहेमायाह (C5XL) कोर में निर्मित उदाहरण जुड़वां हार्डवेयर यादृच्छिक संख्या जनरेटर थे। (इन जनरेटरों को गलती से VIA के मार्केटिंग साहित्य में "क्वांटम-आधारित" कहा जाता है। जनरेटर का विस्तृत विश्लेषण यह स्पष्ट करता है कि यादृच्छिकता का स्रोत थर्मल है, क्वांटम नहीं।[4])

Nehemiah+ (C5P) (स्टेपिंग 8) संशोधन कुछ और उन्नतियां लेकर आया, जिसमें उच्च-प्रदर्शन उन्नत एन्क्रिप्शन मानक एन्क्रिप्शन इंजन के साथ-साथ विशेष रूप से छोटे बॉल ग्रिड ऐरे चिप पैकेज के साथ Cent (संयुक्त राज्य अमेरिका का सिक्का) का आकार शामिल है। उस समय VIA ने भी FSB को 200 MHz तक बढ़ाया और इसे समर्थन देने के लिए CN400 जैसे नए चिपसेट पेश किए। नए 200 मेगाहर्ट्ज एफएसबी चिप्स केवल बीजीए पैकेज में उपलब्ध हैं, क्योंकि वे मौजूदा सॉकेट 370 मदरबोर्ड के साथ संगत नहीं हैं।

जब इस वास्तुकला का विपणन किया गया तो इसे अक्सर VIA C5 के रूप में जाना जाता था।

तकनीकी जानकारी

तुलनात्मक मरने का आकार

| Processor | Secondary Cache (KiB) |

Die size 180 nm (mm²) |

Die size 150 nm (mm²) |

Die size 130 nm (mm²) |

Die size 90 nm (mm²) |

|---|---|---|---|---|---|

| C3 Samuel | N/A | ? | N/A | N/A | N/A |

| C3 Samuel 2 | 64 | N/A | ? | N/A | N/A |

| C3 Ezra | 64 | N/A | N/A | 52 | N/A |

| C3 Nehemiah | 64 | N/A | N/A | 52 | N/A |

| C7 Esther | 128 | N/A | N/A | N/A | 30 |

| Athlon XP | 256 | N/A | N/A | 84 | N/A |

| Athlon 64 | 512 | N/A | N/A | 144 | 84 |

| Pentium M | 2048 | N/A | N/A | N/A | 84 |

| P4 Northwood | 512 | N/A | N/A | 146 | N/A |

| P4 Prescott | 1024 | N/A | N/A | N/A | 110 |

डिजाइन पद्धति

एएमडी और इंटेल द्वारा बेचे जा रहे x86 सीपीयू की तुलना में धीमी गति से, पूर्ण रूप से और घड़ी-दर-घड़ी के आधार पर, VIA के चिप्स बहुत छोटे, निर्माण के लिए सस्ते और कम शक्ति वाले थे। इसने उन्हें एम्बेडेड मार्केटप्लेस में अत्यधिक आकर्षक बना दिया।

इसने वीआईए को प्रत्येक निर्माण प्रक्रिया के मरने के साथ उनके चिप्स की आवृत्तियों को स्केल करना जारी रखने में सक्षम बनाया, जबकि इंटेल के प्रतिस्पर्धी उत्पादों (जैसे पेंटियम 4 # प्रेस्कॉट) को गंभीर थर्मल प्रबंधन मुद्दों का सामना करना पड़ा, हालांकि बाद में चिप्स की इण्टेल कोर पीढ़ी काफी हद तक खराब हो गई थी। कूलर।

3

* क्योंकि स्मृति प्रदर्शन कई बेंचमार्क में सीमित कारक है, अन्य संवर्द्धन के साथ वीआईए प्रोसेसर बड़े सीपीयू कैश, बड़े अनुवाद लुकसाइड बफर और आक्रामक निर्देश प्रीफैच को लागू करते हैं। जबकि ये सुविधाएँ VIA के लिए अद्वितीय नहीं हैं, मेमोरी एक्सेस ऑप्टिमाइज़ेशन ऐसा क्षेत्र है जहाँ उन्होंने डाई स्पेस को बचाने के लिए सुविधाओं को नहीं छोड़ा है।

- क्लॉक फ्रीक्वेंसी सामान्य शब्दों में प्रति चक्र बढ़ते निर्देशों के पक्ष में है। आउट-ऑफ-ऑर्डर निष्पादन जैसी जटिल विशेषताएं। ऑर्डर-ऑफ-ऑर्डर निर्देश निष्पादन जानबूझकर लागू नहीं किया जाता है, क्योंकि वे घड़ी की दर को बढ़ाने की क्षमता को प्रभावित करते हैं, बहुत अधिक अतिरिक्त स्थान और शक्ति की आवश्यकता होती है, और प्रदर्शन पर बहुत कम प्रभाव पड़ता है। कई सामान्य अनुप्रयोग परिदृश्यों में।

- x86 निर्देशों के अत्यधिक उपयोग किए जाने वाले रजिस्टर-मेमोरी और मेमोरी-रजिस्टर रूपों के एक-घड़ी निष्पादन प्रदान करने के लिए पाइपलाइन की व्यवस्था की गई है। कई अक्सर उपयोग किए जाने वाले निर्देशों के लिए अन्य x86 प्रोसेसर की तुलना में कम पाइपलाइन घड़ियों की आवश्यकता होती है।

- कभी-कभी उपयोग किए जाने वाले x86 निर्देशों को माइक्रोकोड और अनुकरण में लागू किया जाता है। यह मरने की जगह बचाता है और बिजली की खपत को कम करता है। अधिकांश वास्तविक-विश्व अनुप्रयोग परिदृश्यों पर प्रभाव कम से कम है।

- ये डिज़ाइन दिशानिर्देश मूल RISC अधिवक्ताओं से व्युत्पन्न हैं, जिन्होंने निर्देशों का छोटा सेट, बेहतर अनुकूलित, तेजी से समग्र CPU प्रदर्शन प्रदान करेगा। चूंकि यह स्रोत और गंतव्य दोनों के रूप में मेमोरी ऑपरेशंस का भारी उपयोग करता है, सी 3 डिज़ाइन स्वयं जोखिम के रूप में योग्य नहीं हो सकता है।

व्यवसाय

अनुबंध

VIA के एम्बेडेड प्लेटफॉर्म उत्पादों को कथित तौर पर (2005) निसान की कार श्रृंखला में अपनाया गया है,[5] निसान लाफे से , निसान गांव और निसान प्रेसेज। ये और अन्य उच्च मात्रा वाले औद्योगिक अनुप्रयोग VIA के लिए बड़े लाभ उत्पन्न करना शुरू कर रहे हैं क्योंकि छोटे फॉर्म फैक्टर और कम बिजली के फायदे करीबी एम्बेडेड सौदे हैं।

कानूनी मुद्दे

IDT Centaur अधिग्रहण के आधार पर,[6] ऐसा प्रतीत होता है कि VIA के पास कम से कम तीन पेटेंट हैं, जो Intel द्वारा उपयोग की जाने वाली प्रोसेसर तकनीक के प्रमुख पहलुओं को कवर करते हैं। 2003 में पेश किए गए इन पेटेंटों के बातचीत के लाभ के आधार पर, VIA इंटेल के साथ समझौते पर पहुंचा, जिसने दस साल के पेटेंट क्रॉस लाइसेंस की अनुमति दी, जिससे VIA को x86 संगत CPU का डिजाइन और निर्माण जारी रखने में मदद मिली। VIA को तीन साल की मोहलत भी दी गई थी जिसमें वह इंटेल सॉकेट इंफ्रास्ट्रक्चर का उपयोग करना जारी रख सकता था।

यह भी देखें

- VIA C3 माइक्रोप्रोसेसरों की सूची

- वीआईए ईडन माइक्रोप्रोसेसरों की सूची

- VIA माइक्रोप्रोसेसरों की सूची

संदर्भ

- ↑ Wagenseil, Paul (9 August 2018). "Hacker Finds Hidden 'God Mode' on Old x86 CPUs". Tom's Hardware. Retrieved 10 August 2018.

- ↑ Poluvyalov, Alexander. VIA Cyrix III (Samuel 2) 600 and 667 MHz, Digit-Life, accessed January 15, 2007.

- ↑ 3.0 3.1 Rutter, Daniel (2011-12-03). "Review: 800MHz Via C3 CPU". Dan's Data. Archived from the original on 2018-03-25. Retrieved 2018-10-15.

- ↑ "Evaluation of VIA C3 "Nehemiah" Random Number Generator" (PDF). Cryptography Research, Inc. Archived from the original (PDF) on 2006-12-31. Retrieved 2007-03-12.

- ↑ The Inquirer report, Friday 30 December 2005

- ↑ "वीआईए और इंटेल सेटल पेटेंट उल्लंघन मामले". VIA Technologies, Inc. Archived from the original on 2007-03-11. Retrieved 2007-03-12.

अग्रिम पठन

- Diefendorff, Keith (7 December 1998). "WinChip 4 Thumbs Nose at ILP" (PDF). Microprocessor Report. MDR Electronic Publishing Group. Retrieved 14 August 2018.

बाहरी संबंध

- VIA-C3-Nehemiah review

- VIA C3 Gold CPU - 1 GHz

- VIA's Small & Quiet Eden Platform

- GHz_processor_review/ VIA C3 1 GHz Processor Review

- BlueSmoke - Review : VIA C3 Processor

- http://www.cpushack.com/VIA.html

- https://web.archive.org/web/20070717014946/http://www.sandpile.org/impl/c5.htm

- https://web.archive.org/web/20060615180950/http://www.sandpile.org/impl/c5xl.htm

- VIA C3 Kernel for FreeBSD Archived 2011-07-23 at the Wayback Machine