अनुक्रमिक स्थिरता

अनुक्रमिक संगति एक संगति मॉडल है जिसका उपयोग समवर्ती कंप्यूटिंग के क्षेत्र में किया जाता है (उदाहरण के लिए वितरित साझा मेमोरी, वितरित लेनदेन, आदि में)।

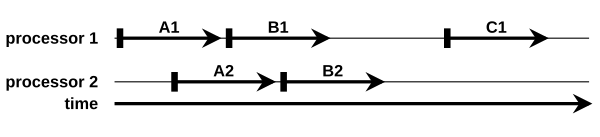

यह संपत्ति है कि ... किसी भी निष्पादन का नतीजा वही होता है जैसे कि सभी प्रोसेसर के संचालन को किसी अनुक्रमिक क्रम में निष्पादित किया गया था, और प्रत्येक व्यक्तिगत प्रोसेसर के संचालन इस क्रम में उसके कार्यक्रम द्वारा निर्दिष्ट क्रम में दिखाई देते हैं।[1] अर्थात्, एक ही प्रोसेसर (या थ्रेड) में एक प्रोग्राम का निष्पादन क्रम प्रोग्राम ऑर्डर के समान होता है, जबकि विभिन्न प्रोसेसर (या थ्रेड्स) पर एक प्रोग्राम का निष्पादन क्रम अपरिभाषित होता है। इस तरह एक उदाहरण में:

A1, B1 और C1 के बीच निष्पादन क्रम संरक्षित है, अर्थात A1 B1 से पहले चलता है, और B1 C1 से पहले चलता है। A2 और B2 के लिए समान। लेकिन, जैसा कि प्रोसेसर के बीच निष्पादन क्रम अपरिभाषित है, B2 C1 से पहले या बाद में चल सकता है (B2 शारीरिक रूप से C1 से पहले चल सकता है, लेकिन B2 का प्रभाव C1 के बाद देखा जा सकता है, जो कि C1 के बाद B2 रन के समान है)

A1, B1 और C1 के बीच निष्पादन क्रम संरक्षित है, अर्थात A1 B1 से पहले चलता है, और B1 C1 से पहले चलता है। A2 और B2 के लिए समान। लेकिन, जैसा कि प्रोसेसर के बीच निष्पादन क्रम अपरिभाषित है, B2 C1 से पहले या बाद में चल सकता है (B2 शारीरिक रूप से C1 से पहले चल सकता है, लेकिन B2 का प्रभाव C1 के बाद देखा जा सकता है, जो कि C1 के बाद B2 रन के समान है)

संकल्पनात्मक रूप से, एकल वैश्विक मेमोरी और एक स्विच है जो किसी भी समय कदम पर मनमाने ढंग से प्रोसेसर को मेमोरी से जोड़ता है। प्रत्येक प्रोसेसर प्रोग्राम ऑर्डर में मेमोरी ऑपरेशंस जारी करता है और स्विच सभी मेमोरी ऑपरेशंस के बीच ग्लोबल सीरियलाइजेशन प्रदान करता है[2]

अनुक्रमिक स्थिरता सख्त स्थिरता से कमजोर है, जिसके लिए उस स्थान पर अंतिम लेखन के मूल्य को वापस करने के लिए किसी स्थान से पढ़ने की आवश्यकता होती है; सख्त स्थिरता की मांग है कि संचालन को उस क्रम में देखा जाए जिसमें वे वास्तव में जारी किए गए थे।

यह भी देखें

संदर्भ

- ↑ Leslie Lamport, "How to Make a Multiprocessor Computer That Correctly Executes Multiprocess Programs", IEEE Trans. Comput. C-28,9 (Sept. 1979), 690-691.

- ↑ Sarita V. Adve, Kourosh Gharachorloo, "Shared Memory Consistency Models: A Tutorial"