इलेक्ट्रॉनिक डिजाइन स्वचालन

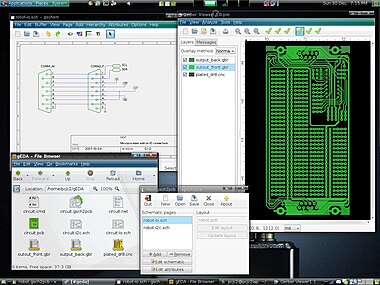

इलेक्ट्रॉनिक डिज़ाइन स्वचालन (ईडीए), जिसे इलेक्ट्रॉनिक कंप्यूटर एडेड डिज़ाइन (ईसीएडी) भी कहा जाता है,[1] एकीकृत परिपथ और मुद्रित परिपथ बोर्ड जैसे इलेक्ट्रानिक्स डिजाइन करने के लिए सॉफ्टवेयर उपकरण की एक श्रेणी है। उपकरण एक डिजाइन प्रवाह (ईडीए) में एक साथ काम करते हैं जो चिप डिजाइनर संपूर्ण अर्धचालक चिप्स को डिजाइन और विश्लेषण करने के लिए उपयोग करते हैं। चूंकि एक आधुनिक अर्धचालक चिप में अरबों घटक हो सकते हैं, ईडीए उपकरण उनके डिजाइन के लिए आवश्यक हैं; यह आलेख विशेष रूप से एकीकृत परिपथ (आईसी) के संबंध में विशेष रूप से ईडीए का वर्णन करता है।

इतिहास

प्रारंभिक दिन

1950 के दशक में अपने 700 श्रृंखला के कंप्यूटरों के प्रलेखन के साथ जल्द से जल्द इलेक्ट्रॉनिक डिजाइन स्वचालन का श्रेय आईबीएम को दिया जाता है

ईडीए के विकास से पहले, एकीकृत परिपथ हाथ से डिजाइन किए गए थे और मैन्युअल रूप से रखे गए थे। कुछ उन्नत दुकानों ने एक गेरबर प्रारूप फोटोप्लॉटर के लिए टेप उत्पन्न करने के लिए ज्यामितीय सॉफ़्टवेयर का उपयोग किया, जो एक मोनोक्रोमैटिक अनावरण छवि बनाने के लिए ज़िम्मेदार था, किन्तु यहां तक कि यांत्रिक रूप से तैयार घटकों की डिजिटल रिकॉर्डिंग की प्रतिलिपि बनाई गई थी। यह प्रक्रिया मौलिक रूप से ग्राफिक थी, जिसमें इलेक्ट्रॉनिक्स से ग्राफिक्स में मैन्युअल रूप से अनुवाद किया गया था; इस युग की सबसे प्रसिद्ध कंपनी Calma थी, जिसका जीडीएसआईआई प्रारूप आज भी उपयोग में है। 1970 के दशक के मध्य तक, विकासकर्ता ने प्रारूपण के अतिरिक्त परिपथ डिजाइन को स्वचालित करना प्रारंभ कर दिया और पहले स्थान और मार्ग उपकरण विकसित किए गए; क्योंकि यह डिजाइन स्वचालन सम्मेलन की कार्यवाही में उस समय के अधिकांश विकासों को सूचीबद्ध किया गया था।

1980 में कार्वर मीड और लिन कॉनवे द्वारा वीएलएसआई प्रणालियों का परिचय के प्रकाशन के बाद अगले युग का प्रारंभ हुआ था; चिप डिजाइन के लिए मानक पाठ्यपुस्तक माना जाता है। परिणाम चिप्स की जटिलता में वृद्धि थी जिसे डिज़ाइन किया जा सकता था, जिसमें कार्यात्मक सत्यापन उपकरण तक उत्तम पहुंच थी जो तर्क सतत का उपयोग करते थे। अधिकांश चिप्स को रखना आसान होता था और उनके सही ढंग से काम करने की अधिक संभावना होती थी, क्योंकि उनके डिजाइनों को निर्माण से पहले अधिक अच्छी प्रकार से अनुकरण किया जा सकता था। चूँकि भाषाएँ और उपकरण विकसित हो गए हैं, एक पाठ्य प्रोग्रामिंग भाषा में वांछित व्यवहार को निर्दिष्ट करने और उपकरणों को विस्तृत भौतिक डिज़ाइन प्राप्त करने देने का यह सामान्य दृष्टिकोण आज भी डिजिटल आईसी डिज़ाइन का आधार बना हुआ है।

प्रारंभिक ईडीए उपकरण अकादमिक रूप से तैयार किए गए थे। सबसे प्रसिद्ध में से एक बर्कले वीएलएसआई उपकरणों टैरबॉल था, यूनिक्स उपयोगिताओं का एक समुच्चय जो प्रारंभिक वीएलएसआई प्रणाली को डिजाइन करने के लिए उपयोग किया जाता था। अभी भी विस्तृत रूप से उपयोग किए जाने वाले एस्प्रेसो हेयुरिस्टिक लॉजिक मिनिमाइज़र हैं, जो परिपथ जटिलता में कमी और मैजिक (सॉफ़्टवेयर), एक कंप्यूटर-एडेड डिज़ाइन प्लेटफ़ॉर्म के लिए जिम्मेदार हैं। एक अन्य महत्वपूर्ण विकास मोसिस का गठन था, विश्वविद्यालयों और फैब्रिकेटरों का एक संघ जिसने वास्तविक एकीकृत परिपथ का निर्माण करके छात्र चिप डिजाइनरों को प्रशिक्षित करने की एक सस्ता विधि विकसित की गई थी। मूल अवधारणा विश्वसनीय, कम लागत वाली, अपेक्षाकृत कम-प्रौद्योगिकी आईसी प्रक्रियाओं का उपयोग करना और प्रति वेफर (इलेक्ट्रॉनिक्स) में बड़ी संख्या में परियोजनाओं को पैक करना था, जिसमें प्रत्येक परियोजना से चिप्स की कई प्रतियां संरक्षित रहती थीं। सहयोगी फैब्रिकेटरों ने या तो प्रसंस्कृत वेफर्स को दान कर दिया या उन्हें कीमत पर बेच दिया, क्योंकि उन्होंने कार्यक्रम को अपने दीर्घकालिक विकास के लिए सहायक देखा था।

वाणिज्यिक ईडीए का जन्म

1981 ने एक उद्योग के रूप में ईडीए की प्रारंभ को चिह्नित किया। कई वर्षों के लिए, बड़ी इलेक्ट्रॉनिक कंपनियों, जैसे कि हेवलेट पैकर्ड , टेक्ट्रोनिक्स और इंटेल ने आंतरिक रूप से ईडीए का अनुसरण किया था, प्रबंधकों और विकासकर्ता ने इन कंपनियों से बाहर निकलने के लिए ईडीए पर एक व्यवसाय के रूप में ध्यान केंद्रित करना प्रारंभ कर दिया था। डेज़ी प्रणालियों , मेंटर ग्राफिक्स और वैध तर्क प्रणाली सभी इसी समय के आसपास स्थापित किए गए थे और सामूहिक रूप से डीएमवी के रूप में संदर्भित किए गए थे। 1981 में, अमेरिकी रक्षा विभाग ने अतिरिक्त रूप से VHDL को एक हार्डवेयर विवरण भाषा के रूप में वित्तपोषित करना प्रारंभ किया। कुछ वर्षों के अन्दर, ईडीए में विशेषज्ञता वाली कई कंपनियां थीं, जिनमें से प्रत्येक पर थोड़ा अलग जोर था।

ईडीए के लिए पहला व्यापार शो 1984 में डिजाइन स्वचालन सम्मेलन में आयोजित किया गया था और 1986 में, गेटवे डिजाइन स्वचालन द्वारा एक और लोकप्रिय उच्च स्तरीय डिजाइन भाषा, वेरिलॉग को पहली बार हार्डवेयर विवरण भाषा के रूप में प्रस्तुत किया गया था। सिमुलेटर ने जल्दी से इन परिचयों का पालन किया, चिप डिजाइन और निष्पादन योग्य विनिर्देशों के प्रत्यक्ष अनुकरण की अनुमति दी। कई वर्षों के अन्दर, तर्क संश्लेषण करने के लिए बैक-एंड विकसित किए गए थे।

वर्तमान स्थिति

वर्तमान डिजिटल प्रवाह अधिक मॉड्यूलर हैं, सामने के छोर से मानकीकृत डिजाइन विवरण तैयार होते हैं जो कि उनकी व्यक्तिगत विधि की परवाह किए बिना कोशिकाओं के समान इकाइयों के आह्वान में संकलित होते हैं। सेल एक विशेष एकीकृत परिपथ प्रौद्योगिकी के उपयोग के माध्यम से तर्क या अन्य इलेक्ट्रॉनिक कार्यों को प्रायुक्त करते हैं। फैब्रिकेटर सामान्यतः अपनी उत्पादन प्रक्रियाओं के लिए घटकों के पुस्तकालय प्रदान करते हैं, जिसमें सतत मॉडल होते हैं जो मानक सतत टूल में फिट होते हैं।

अधिकांश एनालॉग परिपथ अभी भी एक मैनुअल फैशन में डिज़ाइन किए गए हैं, जिसके लिए विशेषज्ञ ज्ञान की आवश्यकता होती है जो एनालॉग डिज़ाइन (जैसे मिलान अवधारणाओं) के लिए अद्वितीय है।[2] इसलिए, एनालॉग ईडीए उपकरण बहुत कम मॉड्यूलर हैं, क्योंकि कई और कार्यों की आवश्यकता होती है, वे अधिक दृढ़ता से बातचीत करते हैं और घटक सामान्य रूप से कम आदर्श होते हैं।

अर्धचालक प्रौद्योगिकी के निरंतर विस्तार के साथ इलेक्ट्रॉनिक्स के लिए ईडीए का महत्व तेजी से बढ़ा है। कुछ उपयोगकर्ता फाउंड्री (इलेक्ट्रॉनिक्स) ऑपरेटर हैं, जो अर्धचालक निर्माण सुविधाओं (फैब्स) का संचालन करते हैं और विधिी डिजाइन-सेवा कंपनियों के उपयोग के लिए जिम्मेदार अतिरिक्त व्यक्ति हैं जो विनिर्माण तत्परता के लिए आने वाले डिजाइन का मूल्यांकन करने के लिए ईडीए सॉफ्टवेयर का उपयोग करते हैं। ईडीए टूल का उपयोग एफपीजीए एस या फील्ड-प्रोग्रामेबल गेट एरेज़, अनुकूलन योग्य एकीकृत परिपथ डिज़ाइन में प्रोग्रामिंग डिज़ाइन कार्यक्षमता के लिए भी किया जाता है।

सॉफ्टवेयर फोकस

डिजाइन

डिजाइन प्रवाह मुख्य रूप से कई प्राथमिक घटकों के माध्यम से विशेषता रहता है; इसमे सम्मिलित है:

- उच्च-स्तरीय संश्लेषण (इसके अतिरिक्त व्यवहार संश्लेषण या एल्गोरिथम संश्लेषण के रूप में जाना जाता है) - उच्च-स्तरीय डिज़ाइन विवरण (उदाहरण के लिए C/C++ में) को RTL या रजिस्टर ट्रांसफर स्तर में परिवर्तित किया जाता है, जो रजिस्टरों के बीच बातचीत के उपयोग के माध्यम से सर्किटरी का प्रतिनिधित्व करने के लिए जिम्मेदार होता है।

- लॉजिक सिंथेसिस - रजिस्टर-स्थानांतरण स्तर डिज़ाइन विवरण (जैसे वेरिलोग या वीएचडीएल में लिखा गया) का असतत नेटलिस्ट या लॉजिक गेट्स के प्रतिनिधित्व में अनुवाद।

- योजनाबद्ध कब्जा - मानक सेल डिजिटल, एनालॉग, आरएफ-जैसे कैप्चर सीआईएस इन ऑर्कैड बाय कैडेंस और आईएसआईएस इन प्रोटियस के लिए।[clarification needed]

- प्लेसमेंट (ईडीए) - सामान्यतः योजनाबद्ध-संचालित लेआउट, जैसे ताल द्वारा ऑर्कैड में लेआउट, प्रोटियस में एआरईएस

सतत

- मसाला - एक योजनाबद्ध/लेआउट के व्यवहार का निम्न-स्तरीय ट्रांजिस्टर-सतत, डिवाइस-स्तर पर त्रुटिहीन।

- लॉजिक सतत - एक रजिस्टर-ट्रांसफर स्तर या गेट-नेटलिस्ट के डिजिटल (बूलियन बीजगणित 0/1) व्यवहार का डिजिटल-सतत, बूलियन-स्तर पर त्रुटिहीन।

- व्यवहार अनुकरण - एक डिजाइन के वास्तुशिल्प संचालन का उच्च-स्तरीय अनुकरण, चक्र-स्तर या इंटरफ़ेस-स्तर पर त्रुटिहीन।

- हार्डवेयर अनुकरण - प्रस्तावित डिजाइन के तर्क का अनुकरण करने के लिए विशेष प्रयोजन हार्डवेयर का उपयोग। कभी-कभी अभी तक बनने वाली चिप के स्थान पर प्रणालियों में प्लग किया जा सकता है; इसे इन-परिपथ इम्यूलेशन कहा जाता है।

- प्रौद्योगिकी सीएडी अंतर्निहित प्रक्रिया प्रौद्योगिकी का अनुकरण और विश्लेषण करती है। उपकरणों के विद्युत गुण सीधे उपकरण भौतिकी से प्राप्त होते हैं।

- विद्युत चुम्बकीय क्षेत्र सॉल्वर , या सिर्फ इलेक्ट्रोमैग्नेटिक फील्ड सॉल्वर, आईसी और पीसीबी डिजाइन में रुचि के स्थितियों के लिए सीधे मैक्सवेल के समीकरणों को समाधान करते हैं। वे धीमे होने के लिए जाने जाते हैं किन्तु ऊपर दिए गए लेआउट निष्कर्षण की तुलना में अधिक त्रुटिहीन होते हैं।[where?]

विश्लेषण और सत्यापन

- कार्यात्मक सत्यापन

- घड़ी डोमेन क्रॉसिंग वेरिफिकेशन (सीडीसी चेक): लिंट प्रोग्रामिंग टूल के समान, किन्तु ये चेक/टूल डिजाइन में कई क्लॉक डोमेन के उपयोग के कारण डेटा हानि, इलेक्ट्रॉनिक्स में मेटास्टेबिलिटी जैसे संभावित मुद्दों का पता लगाने और रिपोर्ट करने में विशेषज्ञ हैं।

- औपचारिक सत्यापन , मॉडल जाँच भी: गणितीय विधियों से यह सिद्ध करने का प्रयास कि प्रणाली में कुछ वांछित गुण हैं, और कुछ अवांछित प्रभाव (जैसे गतिरोध ) नहीं हो सकते हैं।

- औपचारिक तुल्यता जाँच : तार्किक स्तर पर कार्यात्मक तुल्यता सुनिश्चित करने के लिए चिप के आरटी लाइनक्स -विवरण और संश्लेषित गेट-नेटलिस्ट के बीच एल्गोरिथम तुलना।

- स्थिर समय विश्लेषण: एक इनपुट-स्वतंत्र विधियों से एक परिपथ के समय का विश्लेषण, इसलिए सभी संभावित इनपुट पर सबसे खराब स्थिति का पता लगाना।

- भौतिक सत्यापन , पीवी: यह जांचना कि क्या कोई डिज़ाइन भौतिक रूप से निर्माण योग्य है, और परिणामी चिप्स में कोई फ़ंक्शन नहीं होगा-भौतिक दोषों को रोकना, और मूल विनिर्देशों को पूरा करेगा।

निर्माण की तैयारी

- मास्क डेटा तैयार करना या एमडीपी - वास्तविक फोटोलिथोग्राफी फोटोमास्क की पीढ़ी, जिसका उपयोग भौतिक रूप से चिप के निर्माण के लिए किया जाता है।

- चिप फिनिशिंग जिसमें लेआउट की मैन्युफैक्चरिबिलिटी (आईसी) के लिए डिजाइन में सुधार के लिए कस्टम पदनाम और संरचनाएं सम्मिलित हैं। उत्तरार्द्ध के उदाहरण एक सील की रिंग और भराव संरचनाएं हैं।[3]

- परीक्षण पैटर्न और संरेखण चिह्नों के साथ एक लजीला व्यक्ति लेआउट का निर्माण।

- लेआउट-टू-मास्क तैयारी जो ग्राफिक्स संचालन के साथ लेआउट डेटा को बढ़ाती है, जैसे संकल्प बढ़ाने की विधि या आरईटी - अंतिम फोटोमास्क की गुणवत्ता बढ़ाने के विधियों। इसमें ऑप्टिकल निकटता सुधार या ओपीसी भी सम्मिलित है - विवर्तन और हस्तक्षेप (तरंग प्रसार) प्रभावों के लिए अप-फ्रंट मुआवजा बाद में होता है जब इस मास्क का उपयोग करके चिप का निर्माण किया जाता है।

- मुखौटा पीढ़ी - पदानुक्रमित डिज़ाइन से फ़्लैट मास्क छवि का निर्माण।

- स्वचालित परीक्षण पैटर्न पीढ़ी या एटीपीजी - अधिक से अधिक लॉजिक-गेट्स और अन्य घटकों का उपयोग करने के लिए व्यवस्थित रूप से पैटर्न डेटा की पीढ़ी।

- अंतर्निहित स्व-परीक्षण या बीआईएसटी - डिजाइन में तर्क या स्मृति संरचना का स्वचालित रूप से परीक्षण करने के लिए स्वयं निहित परीक्षण-नियंत्रकों की स्थापना

कार्यात्मक सुरक्षा

- वांछित सुरक्षा अखंडता स्तरों के लिए अनुपालन आवश्यकताओं को पूरा करने के लिए कार्यात्मक सुरक्षा विश्लेषण , समय में विफलता (एफआईटी) दरों की व्यवस्थित गणना और डिजाइन के लिए नैदानिक कवरेज मेट्रिक्स।

- कार्यात्मक सुरक्षा संश्लेषण , गलती का पता लगाने / गलती सहनशीलता में सुधार के लिए संरचित तत्वों (मॉड्यूल, रैम, रोम, रजिस्टर फाइल, फीफो) में विश्वसनीयता वृद्धि जोड़ें। इनमें (सीमित नहीं), त्रुटि का पता लगाने और / या सुधार कोड (हैमिंग), गलती का पता लगाने के लिए अनावश्यक तर्क और गलती सहनशीलता (डुप्लिकेट / ट्रिपलेट) और प्रोटोकॉल जांच (इंटरफ़ेस समता, पता संरेखण, बीट गिनती) सम्मिलित है।

- कार्यात्मक सुरक्षा सत्यापन , एक गलती अभियान चलाना, जिसमें डिजाइन और सत्यापन में दोषों को सम्मिलित करना सम्मिलित है कि सुरक्षा तंत्र उन दोषों के लिए उपयुक्त विधियों से प्रतिक्रिया करता है जिन्हें कवर किया गया माना जाता है।

कंपनियां

पुरानी कंपनियां

दिसंबर 2011 तकबाजार पूंजीकरण और कंपनी का नाम:[4]

- $ 5.77 बिलियन[5] - सिनोप्सिस

- $4.46 बिलियन[6] - ताल डिजाइन प्रणाली

- $3.41 बिलियन - अल्टियम

- $ 2.33 बिलियन - मेंटर ग्राफिक्स

- 507 मिलियन डॉलर - मैग्मा डिजाइन स्वचालन; सिनोप्सिस ने फरवरी 2012 में मैग्मा का अधिग्रहण किया[7][8]

- नया ताइवान डॉलर|NT$6.44 बिलियन - स्प्रिंगसॉफ्ट ; सिनोप्सिस ने अगस्त 2012 में स्प्रिंगसॉफ्ट का अधिग्रहण किया

- 11.95 बिलियन - ज़ुकेन इंक।

नोट: ईईसोफ़ इस सूची में होने की संभावना है,[9] किन्तु इसका मार्केट कैप नहीं है क्योंकि यह कीसाइट का ईडीए डिवीजन है।

अधिग्रहण

कई ईडीए कंपनियां सॉफ्टवेयर या अन्य विधि के साथ छोटी कंपनियों का अधिग्रहण करती हैं जिन्हें उनके मुख्य व्यवसाय के लिए अनुकूलित किया जा सकता है।[10] बाजार के अधिकांश नेता कई छोटी कंपनियों के समामेलन हैं और इस प्रवृत्ति को सॉफ्टवेयर कंपनियों द्वारा सहायक उपकरण के रूप में उपकरण डिजाइन करने की प्रवृत्ति से सहायता मिलती है जो डिजिटल परिपथरी पर कार्यक्रमों के बड़े विक्रेता के सूट में स्वाभाविक रूप से फिट होते हैं; कई नए टूल में एनालॉग डिज़ाइन और मिश्रित प्रणाली सम्मिलित हैं।[11] ऐसा प्रणाली को चिप पर रखने की प्रवृत्ति के कारण हो रहा है।

यह भी देखें

- कंप्यूटर एडेड डिजाइन (सीएडी)

- परिपथ डिज़ाइन

- एक डेटाबेस

- साइनऑफ़ (इलेक्ट्रॉनिक डिज़ाइन स्वचालन)

- ईडीए सॉफ्टवेयर की तुलना

- प्लेटफॉर्म आधारित डिजाइन

संदर्भ

- ↑ "About the EDA Industry". Electronic Design Automation Consortium. Archived from the original on August 2, 2015. Retrieved July 29, 2015.

- ↑ J. Lienig, J. Scheible (2020). "Chap. 6: Special Layout Techniques for Analog IC Design". Fundamentals of Layout Design for Electronic Circuits. Springer. p. 213-256. doi:10.1007/978-3-030-39284-0. ISBN 978-3-030-39284-0. S2CID 215840278.

- ↑ J. Lienig, J. Scheible (2020). "Chap. 3.3: Mask Data: Layout Post Processing". Fundamentals of Layout Design for Electronic Circuits. Springer. p. 102-110. doi:10.1007/978-3-030-39284-0. ISBN 978-3-030-39284-0. S2CID 215840278.

- ↑ Company Comparison - Google Finance. Google.com. Retrieved on 2013-08-10.

- ↑ Synopsys, Inc.: NASDAQ:SNPS quotes & news - Google Finance. Google.com (2013-05-22). Retrieved on 2013-08-10.

- ↑ CDNS Key Statistics | Cadence Design Systems, Inc. Stock - Yahoo! Finance. Finance.yahoo.com. Retrieved on 2013-08-10.

- ↑ Dylan McGrath (30 Nov 2011). "Synopsys to buy Magma for $507 million". EETimes. Archived from the original on October 25, 2012. Retrieved July 17, 2012.

- ↑ "Synopsys to Acquire Magma Design Automation".

- ↑ "Agilent EEsof EDA – Part I".

- ↑ Kirti Sikri Desai (2006). "EDA Innovation through Merger and Acquisitions". EDA Cafe. Retrieved March 23, 2010.

- ↑ "Semi Wiki:EDA Mergers and Acquisitions Wiki". SemiWiki.com (in English). 2011-01-16. Archived from the original on April 3, 2019. Retrieved 2019-04-03.

- Notes

- http://www.staticfreesoft.com/documentsTextbook.html Computer Aids for VLSI Design by Steven M. Rubin

- Fundamentals of Layout Design for Electronic Circuits, by Lienig, Scheible, Springer, doi:10.1007/978-3-030-39284-0ISBN 978-3-030-39284-0, 2020

- VLSI Physical Design: From Graph Partitioning to Timing Closure, by Kahng, Lienig, Markov and Hu, doi:10.1007/978-90-481-9591-6ISBN 978-90-481-9590-9, 2011

- Electronic Design Automation For Integrated Circuits Handbook, by Lavagno, Martin, and Scheffer, ISBN 0-8493-3096-3, 2006

- The Electronic Design Automation Handbook, by Dirk Jansen et al., Kluwer Academic Publishers, ISBN 1-4020-7502-2, 2003, available also in German ISBN 3-446-21288-4 (2005)

- Combinatorial Algorithms for Integrated Circuit Layout, by Thomas Lengauer, ISBN 3-519-02110-2, Teubner Verlag, 1997.