विडलर विद्युत धारा स्रोत

एक विडलर वर्तमान स्रोत मूल दो-अवरोध वर्तमान दर्पण का संशोधन है जो केवल आउटपुट ट्रांजिस्टर के लिए उत्सर्जक अध: पतन रोकनेवाला को सम्मिलित करता है, जो वर्तमान स्रोत को केवल मध्यम प्रतिरोधक मानों का उपयोग करके कम धाराओं को उत्पन्न करने में सक्षम बनाता है।[1][2][3]

विडलर परिपथ का उपयोग द्विध्रु[4]वी ट्रांजिस्टर, एमओएसएफईटी और यहां तक कि शून्यक-नाली के साथ भी किया जा सकता है। उदाहरण अनुप्रयोग 741-प्रकार के ऑप एम्प का परिचालन प्रवर्धक#आंतरिक परिपथ है,[5] और विडलर ने परिपथ को कई बनावट में हिस्से के रूप में इस्तेमाल किया जाता है।

इस परिपथ का नाम इसके आविष्कारक बॉब विडलर के नाम पर रखा गया है और 1967 में इसका पेटेंट कराया गया था।[6][7]

डीसी विश्लेषण

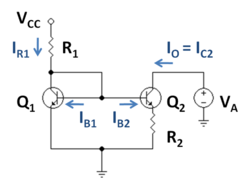

चित्रा 1 द्विध्रुवी ट्रांजिस्टर का उपयोग करते हुए विडलर वर्तमान स्रोत का उदाहरण है, जहां उत्सर्जक रोकनेवाला आर2 आउटपुट ट्रांजिस्टर क्यू से जुड़ा है2, और क्यू में वाहक को कम करने का प्रभाव है2 क्यू के सापेक्ष1. इस सर्किट की कुंजी यह है कि प्रतिरोधक आर के पार वोल्टेज गिरता है2 ट्रांजिस्टर क्यू के आधारित उत्सर्जन वोल्टेज से घटाता है2, जिससे इस ट्रांजिस्टर को ट्रांजिस्टर क्यू की तुलना में समाप्त कर दिया जाता है1. यह अवलोकन चित्र 1 में परिपथ के दोनों ओर पाए जाने वाले आधार वोल्टेज अभिव्यक्ति की बराबरी करके व्यक्त किया गया है:

जहां बी2 आउटपुट ट्रांजिस्टर का बीटा-मान है, जो इनपुट ट्रांजिस्टर के समान नहीं है, आंशिक रूप से क्योंकि दो ट्रांजिस्टर में धाराएं बहुत भिन्न हैं।[8] चर IB2 आउटपुट ट्रांजिस्टर, V का आधार वाहक हैBE आधारित उत्सर्जन वोल्टेज को संदर्भित करता है। इस समीकरण का अर्थ है (शॉकली डायोड समीकरण का उपयोग करके):

सम। 1

जहां वीT बोल्ट्जमान स्थिरांक है # सेमीकंडक्टर भौतिकी में भूमिका: थर्मल वोल्टेज है।

यह समीकरण सन्निकटन करता है कि धाराएँ स्केल धाराओं, I की तुलना में बहुत बड़ी हैंS1 और मैंS2; द्विध्रुवी जंक्शन ट्रांजिस्टर # ऑपरेशन के क्षेत्रों के निकट वर्तमान स्तरों को छोड़कर सन्निकटन मान्य है। निम्नलिखित में, स्केल धाराओं को समान माना जाता है; व्यवहार में, इसे विशेष रूप से व्यवस्थित करने की आवश्यकता है।

निर्दिष्ट धाराओं के साथ डिजाइन प्रक्रिया

दर्पण को डिजाइन करने के लिए, आउटपुट करंट को दो प्रतिरोधक मान R से संबंधित होना चाहिए1 और आर2. एक बुनियादी अवलोकन यह है कि आउटपुट ट्रांजिस्टर बाइपोलर जंक्शन ट्रांजिस्टर # ऑपरेशन के क्षेत्रों में केवल तभी तक होता है जब तक इसका कलेक्टर-बेस वोल्टेज गैर-शून्य होता है। इस प्रकार, दर्पण के डिजाइन के लिए सबसे सरल पूर्वाग्रह स्थिति लागू वोल्टेज वी सेट करती हैA बेस वोल्टेज वी के बराबर करने के लिएB. वी का यह न्यूनतम उपयोगी मूल्यA वर्तमान दर्पण # वर्तमान स्रोत का अनुपालन वोल्टेज कहा जाता है। उस पूर्वाग्रह की स्थिति के साथ, प्रारंभिक प्रभाव डिजाइन में कोई भूमिका नहीं निभाता है।[9] ये विचार निम्नलिखित डिजाइन प्रक्रिया का सुझाव देते हैं:

- वांछित आउटपुट करंट का चयन करें, IO = मैंC2.

- संदर्भ वर्तमान का चयन करें, IR1, आउटपुट करंट से बड़ा माना जाता है, शायद काफी बड़ा (यही सर्किट का उद्देश्य है)।

- क्यू के इनपुट कलेक्टर वर्तमान का निर्धारण करें1, मैंC1:

- बेस वोल्टेज वी निर्धारित करेंBE1 डायोड मॉडलिंग#शॉकली डायोड मॉडल का उपयोग करना

- जहां मैंS एक डिवाइस पैरामीटर है जिसे कभी-कभी स्केल करंट कहा जाता है।

- बेस वोल्टेज का मान भी अनुपालन वोल्टेज वी सेट करता हैA = वीBE1. यह वोल्टेज सबसे कम वोल्टेज है जिसके लिए दर्पण ठीक से काम करता है।

- आर निर्धारित करें1:

- {{anchor|R2}उत्सर्जक लेग प्रतिरोध R ज्ञात कीजिए2 #Eq1|Eq का उपयोग करना। 1 (अव्यवस्था को कम करने के लिए, पैमाने की धाराओं को बराबर चुना जाता है):

दिए गए प्रतिरोधक मानों के साथ करंट का पता लगाना

डिज़ाइन की समस्या का व्युत्क्रम वर्तमान का पता लगाना है जब प्रतिरोधक मान ज्ञात होते हैं। आगे एक पुनरावृत्त विधि का वर्णन किया गया है। मान लें कि वर्तमान स्रोत पक्षपाती है इसलिए आउटपुट ट्रांजिस्टर क्यू का कलेक्टर-बेस वोल्टेज2 शून्य है। आर के माध्यम से वर्तमान1 इनपुट या संदर्भ वर्तमान के रूप में दिया गया है,

पुनर्व्यवस्थित, आईC1 के रूप में पाया जाता है:

सम। 2

डायोड समीकरण प्रदान करता है:

{{anchor|Eq3}समीकरण। 3

- Eq1|Eq.1 प्रदान करता है:

ये तीन संबंध धाराओं के लिए एक गैर-रैखिक, निहित निर्धारण हैं जिन्हें पुनरावृति द्वारा हल किया जा सकता है।

- हम I के लिए शुरुआती मानों का अनुमान लगाते हैंC1 और मैंC2.

- हम वी के लिए एक मान पाते हैंBE1:

- हम I के लिए एक नया मान पाते हैंC1:

- हम I के लिए एक नया मान पाते हैंC2:

यह प्रक्रिया अभिसरण के लिए दोहराई जाती है, और एक स्प्रेडशीट में आसानी से स्थापित की जाती है। लघु क्रम में समाधान प्राप्त करने के लिए प्रारंभिक मानों को धारण करने वाली स्प्रेडशीट कोशिकाओं में नए मानों को कॉपी करने के लिए बस एक मैक्रो का उपयोग करता है।

ध्यान दें कि दिखाए गए सर्किट के साथ, यदि VCC परिवर्तन, आउटपुट करंट बदल जाएगा। इसलिए, V में उतार-चढ़ाव के बावजूद आउटपुट करंट को स्थिर रखने के लिएCC, प्रतिरोध आर का उपयोग करने के बजाय सर्किट को वर्तमान स्रोत द्वारा संचालित किया जाना चाहिए1.

सटीक समाधान

उपर्युक्त ट्रान्सेंडैंटल समीकरणों को ठीक लैम्बर्ट डब्ल्यू समारोह के संदर्भ में हल किया जा सकता है।

आउटपुट प्रतिबाधा

वर्तमान स्रोत की एक महत्वपूर्ण संपत्ति इसका छोटा संकेत वृद्धिशील आउटपुट प्रतिबाधा है, जो आदर्श रूप से अनंत होना चाहिए। विडलर सर्किट ट्रांजिस्टर के लिए स्थानीय करंट फीडबैक पेश करता है . क्यू में वर्तमान में कोई वृद्धि2 आर भर में वोल्टेज ड्रॉप बढ़ाता है2, वी को कम करनाBE क्यू के लिए2, जिससे करंट में वृद्धि का मुकाबला किया जा सके। इस प्रतिक्रिया का मतलब है कि सर्किट का आउटपुट प्रतिबाधा बढ़ गया है, क्योंकि प्रतिक्रिया में आर शामिल है2 किसी दिए गए करंट को चलाने के लिए एक बड़े वोल्टेज का उपयोग करने के लिए मजबूर करता है।

सर्किट के लिए एक छोटे-सिग्नल मॉडल का उपयोग करके आउटपुट प्रतिरोध पाया जाता है, चित्र 2 में दिखाया गया है। ट्रांजिस्टर क्यू1 इसके छोटे-सिग्नल उत्सर्जक प्रतिरोध आर द्वारा प्रतिस्थापित किया जाता हैE क्योंकि यह डायोड जुड़ा हुआ है।[10] ट्रांजिस्टर Q2 इसके हाइब्रिड-पाई मॉडल के साथ बदल दिया गया है। एक परीक्षण वर्तमान Ix आउटपुट पर संलग्न है।

आकृति का उपयोग करते हुए, किरचॉफ के नियमों का उपयोग करके आउटपुट प्रतिरोध निर्धारित किया जाता है। किरचॉफ के वोल्टेज कानून का उपयोग जमीन से बाईं ओर आर के जमीन कनेक्शन के लिए2:

पुनर्व्यवस्थित:

आर के ग्राउंड कनेक्शन से किरचॉफ के वोल्टेज कानून का उपयोग करना2 परीक्षण वर्तमान के आधार पर:

या, I के लिए प्रतिस्थापनb:

{{anchor|Eq4}समीकरण। 4

- Eq4|Eq के अनुसार। 4, Widlar करंट सोर्स का आउटपुट रेजिस्टेंस आउटपुट ट्रांजिस्टर के ही ऊपर बढ़ जाता है (जो कि r हैO) जब तक आर2 r की तुलना में काफी बड़ा हैπ आउटपुट ट्रांजिस्टर (बड़े प्रतिरोध आर2 कारक गुणा आर बनाओO मूल्य (β + 1) तक पहुंचें)। आउटपुट ट्रांजिस्टर में कम करंट होता है, जिससे r बनता हैπ बड़ा, और आर में वृद्धि2 इस धारा को और कम करता है, जिससे r में सहसंबद्ध वृद्धि होती हैπ. इसलिए, आर का एक लक्ष्य2 ≫ आरπ अवास्तविक हो सकता है, और आगे की चर्चा प्रदान की जाती है # आउटपुट प्रतिरोध की वर्तमान निर्भरता। प्रतिरोध आर1∥rE आमतौर पर छोटा होता है क्योंकि उत्सर्जक प्रतिरोध आरE आमतौर पर केवल कुछ ओम होते हैं।

आउटपुट प्रतिरोध की वर्तमान निर्भरता

प्रतिरोधों की वर्तमान निर्भरता आरπ और आरO लेख हाइब्रिड-पीआई मॉडल में चर्चा की गई है। प्रतिरोधक मानों की वर्तमान निर्भरता है:

और

प्रारंभिक प्रभाव के कारण आउटपुट प्रतिरोध है जब VCB = 0 वी (डिवाइस पैरामीटर वीA प्रारंभिक वोल्टेज है)।

इस लेख में #R2 से (सुविधा के लिए स्केल धाराओं को बराबर सेट करना): {{anchor|Eq5}समीकरण। 5

नतीजतन, छोटे आर के सामान्य मामले के लिएE, और R में दूसरे कार्यकाल की उपेक्षा करनाO इस अपेक्षा के साथ कि अग्रणी शब्द जिसमें r शामिल हैO बहुत बड़ा है: {{Anchor|Eq6}समीकरण। 6

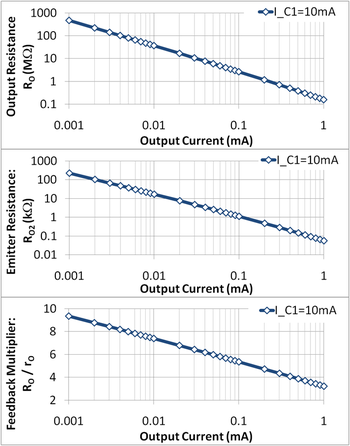

जहाँ #Eq5|Eq को प्रतिस्थापित करके अंतिम रूप प्राप्त होता है। आर के लिए 52. #Eq6|Eq. 6 से पता चलता है कि आउटपुट प्रतिरोध का मान r से बहुत बड़ा हैO केवल I के साथ डिज़ाइन के लिए आउटपुट ट्रांजिस्टर परिणामC1 >> मैंC2. चित्रा 3 दिखाता है कि सर्किट आउटपुट प्रतिरोध आरO फीडबैक द्वारा इतना अधिक निर्धारित नहीं किया जाता है जितना कि प्रतिरोध r की वर्तमान निर्भरता द्वाराO आउटपुट ट्रांजिस्टर का (चित्र 3 में आउटपुट प्रतिरोध परिमाण के चार क्रमों में भिन्न होता है, जबकि प्रतिक्रिया कारक केवल परिमाण के एक क्रम से भिन्न होता है)।

आई की वृद्धिC1 प्रतिक्रिया कारक को बढ़ाने के लिए भी अनुपालन वोल्टेज में वृद्धि हुई है, अच्छी बात नहीं है क्योंकि इसका मतलब है कि वर्तमान स्रोत अधिक प्रतिबंधित वोल्टेज रेंज पर काम करता है। इसलिए, उदाहरण के लिए, अनुपालन वोल्टेज सेट के लक्ष्य के साथ, I पर ऊपरी सीमा रखकरC1, और आउटपुट प्रतिरोध को पूरा करने के लक्ष्य के साथ, आउटपुट करंट I का अधिकतम मानC2 सीमित है।

चित्र 3 में केंद्र पैनल एमिटर लेग रेजिस्टेंस और आउटपुट करंट के बीच डिज़ाइन ट्रेड-ऑफ दिखाता है: कम आउटपुट करंट के लिए बड़े लेग रेसिस्टर की आवश्यकता होती है, और इसलिए डिज़ाइन के लिए एक बड़ा क्षेत्र। क्षेत्र पर एक ऊपरी सीमा इसलिए आउटपुट करंट पर एक निचली सीमा और सर्किट आउटपुट प्रतिरोध पर एक ऊपरी सीमा निर्धारित करती है।

- Eq6|Eq. आर के लिए 6O R के मान के चयन पर निर्भर करता है2 #Eq5|Eq के अनुसार। 5. इसका मतलब #Eq6|Eq. 6 एक सर्किट व्यवहार सूत्र नहीं है, बल्कि एक डिज़ाइन मान समीकरण है। एक बार आर2 #Eq5|Eq का उपयोग करके किसी विशेष डिज़ाइन उद्देश्य के लिए चयन किया जाता है। 5, उसके बाद इसका मूल्य तय हो गया है। यदि सर्किट ऑपरेशन के कारण करंट, वोल्टेज या तापमान डिज़ाइन किए गए मानों से विचलित हो जाते हैं; फिर आर में परिवर्तन की भविष्यवाणी करने के लिएO ऐसे विचलन के कारण, #Eq4|Eq. 4 का उपयोग किया जाना चाहिए, #Eq6|Eq का नहीं। 6.

यह भी देखें

- वर्तमान स्रोत

- वर्तमान दर्पण

- विल्सन वर्तमान स्रोत

संदर्भ

- ↑ PR Gray, PJ Hurst, SH Lewis & RG Meyer (2001). एनालॉग इंटीग्रेटेड सर्किट का विश्लेषण और डिजाइन (4th ed.). John Wiley and Sons. pp. §4.4.1.1 pp. 299–303. ISBN 0-471-32168-0.

{{cite book}}: CS1 maint: multiple names: authors list (link) - ↑ AS Sedra & KC Smith (2004). माइक्रोइलेक्ट्रॉनिक सर्किट (5th ed.). Oxford University Press. Example 6.14, pp. 654–655. ISBN 0-19-514251-9.

- ↑ MH Rashid (1999). Microelectronic circuits: analysis and design. PWS Publishing Co. pp. 661–665. ISBN 0-534-95174-0.

- ↑ See, for example, Figure 2 in IC voltage regulators.

- ↑ AS Sedra & KC Smith (2004). §9.4.2, p. 899 (5th ed.). ISBN 0-19-514251-9.

- ↑ RJ Widlar: US Patent Number 03320439; Filed May 26, 1965; Granted May 16, 1967: Low-value current source for integrated circuits

- ↑ See Widlar: Some circuit design techniques for linear integrated circuits and Design techniques for monolithic operational amplifiers

- ↑ PR Gray, PJ Hurst, SH Lewis & RG Meyer (2001). Figure 2.38, p. 115. ISBN 0-471-32168-0.

{{cite book}}: CS1 maint: multiple names: authors list (link) - ↑ Of course, one might imagine a design where the output resistance of the mirror is a major consideration. Then a different approach is necessary.

- ↑ In a diode-connected transistor the collector is short-circuited to the base, so the transistor collector-base junction has no time-varying voltage across it. As a result, the transistor behaves like the base-emitter diode, which at low frequencies has a small-signal circuit that is simply the resistor rE = VT / IE, with IE the DC Q-point emitter current. See diode small-signal circuit.

अग्रिम पठन

- Linden T. Harrison (2005). Current Sources and Voltage References: A Design Reference for Electronics Engineers. Elsevier-Newnes. ISBN 0-7506-7752-X.

- Sundaram Natarajan (2005). Microelectronics: Analysis and Design. Tata McGraw-Hill. p. 319. ISBN 0-07-059096-6.

- Current mirrors and active loads: Mu-Huo Cheng