वाया (इलेक्ट्रॉनिक्स)

This article includes a list of general references, but it lacks sufficient corresponding inline citations. (December 2017) (Learn how and when to remove this template message) |

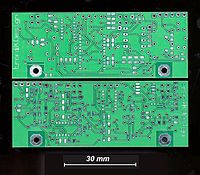

एक वाया (लैटिन, 'पथ' या 'वे') दो या दो से अधिक धातु परतों के बीच एक वैद्युत संबंधन होता है, जो सामान्य पर मुद्रित परिपथ बोर्डों में उपयोग किया जाता है। मूल रूप से वाया एक छोटा प्रवेधित किया हुआ छेद है जो दो या दो से अधिक आसन्न परतों से होकर गुजरता है, छेद को धातु (अक्सर तांबा) से विद्युत् लेपित किया जाता है जो ऊष्मारोधी परतों के माध्यम से वैद्युत संबंधन बनाता है।

वाया पीसीबी निर्माण के लिए महत्वपूर्ण होते हैं।[1] ऐसा इसलिए है क्योंकि वायास को कुछ सहनशीलता के साथ प्रवेधित किया जाता है और उनके निर्दिष्ट स्थानों से निर्मित किया जा सकता है, इसलिए निर्माण से पहले प्रवेधित स्थिति में त्रुटियों के लिए कुछ छूट दी जानी चाहिए अन्यथा गैर-अनुरूप बोर्डों (कुछ संदर्भ मानक के अनुसार) या यहां तक कि ख़राब बोर्डों के कारण विनिर्माण उत्पादन में कमी आ सकती है। इसके अतिरिक्त, नियमित छेद के माध्यम से वाया संरचनाएँ कमजोर मानी जाती हैं क्योंकि वे लंबी और संकीर्ण होती हैं, निर्माता को यह सुनिश्चित करना चाहिए कि वाया पूरे बैरल में ठीक से विद्युत् लेपित गया है क्योकि इसके परिणामस्वरूप कई प्रसंस्करण चरण उत्पन्न होते हैं।

मुद्रित परिपथ बोर्डों में

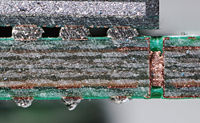

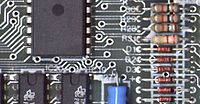

मुद्रित परिपथ बोर्ड (पीसीबी) प्रारूप में, वाया में दो पैड होते हैं जो बोर्ड की विभिन्न तांबे की परतों पर समान स्थितियों में होते हैं, और जिन्हें बोर्ड के माध्यम से एक छेद के माध्यम से विद्युतीय रूप से जोड़ा जाता है।[citation needed] छेद को विद्युत लेपन द्वारा यह प्रवाहकीय बनाया जाता है, तथा एक ट्यूब या कीलक के साथ पंक्तिबद्ध किया जाता है।[citation needed] उच्च-घनत्व मल्टीलेयर पीसीबी में माइक्रोवेव हो सकते हैं: ब्लाइंड विया केवल बोर्ड के एक तरफ उजागर होते हैं, जबकि दबे हुए विया किसी भी सतह पर उजागर हुए बिना आंतरिक परतों को जोड़ते हैं। थर्मल वयास बिजली उपकरणों से गर्मी को दूर ले जाता है और सामान्य पर लगभग एक दर्जन के सरणियों में उपयोग किया जाता है।[2][3]

ए वाया में शामिल हैं:

- बैरल - प्रवेधित किए गए छेद को भरने वाली प्रवाहकीय ट्यूब

- पैड - बैरल के प्रत्येक सिरे को घटक, विमान या ट्रेस से जोड़ता है

- एंटीपैड - बैरल और धातु की परत के बीच निकासी छेद जिससे यह जुड़ा नहीं है

ए वाया, जिसे कभी-कभी पीटीवी या प्लेटेड-थ्रू-थ्रू भी कहा जाता है, को प्लेटेड थ्रू होल (पीटीएच) के साथ भ्रमित नहीं किया जाना चाहिए। विया का उपयोग पीसीबी पर तांबे की परतों के बीच एक इंटरसंयोजन के रूप में किया जाता है, जबकि पीटीएच को सामान्य पर वियास से बड़ा बनाया जाता है और घटक लीड की स्वीकृति के लिए एक प्लेटेड छेद के रूप में उपयोग किया जाता है - जैसे कि गैर-एसएमटी प्रतिरोधक, कैपेसिटर और डीआईपी पैकेज आईसी। पीटीएच का उपयोग यांत्रिक संयोजन के लिए छेद के रूप में भी किया जा सकता है जबकि वियास का नहीं। पीटीएच का एक अन्य उपयोग कैस्टेलेटेड छेद के रूप में जाना जाता है जहां पीटीएच को बोर्ड के किनारे पर संरेखित किया जाता है ताकि जब बोर्ड को पैनल से बाहर निकाला जाए तो यह आधा कट जाए - मुख्य उपयोग एक पीसीबी को सोल्डर करने की अनुमति देने के लिए है एक स्टैक में दूसरा - इस प्रकार फास्टनर और कनेक्टर दोनों के रूप में कार्य करता है।[4]

तीन प्रमुख प्रकार के vias को सही चित्र में दिखाया गया है। पीसीबी बनाने के मूल चरण हैं: सब्सट्रेट सामग्री बनाना और इसे परतों में ढेर करना; वियास चढ़ाने की थ्रू-ड्रिलिंग; और फोटोलिथोग्राफी और नक़्क़ाशी का उपयोग करके कॉपर ट्रेस पैटर्निंग। इस मानक प्रक्रिया के साथ, कॉन्फ़िगरेशन के माध्यम से संभवता थ्रू-होल तक सीमित है।[lower-alpha 1] गहराई-नियंत्रित ड्रिलिंग तकनीक जैसे कि लेजर का उपयोग प्रकारों के माध्यम से अधिक विविधता की अनुमति दे सकता है। (लेजर प्रवेधित का उपयोग यांत्रिक प्रवेधित की तुलना में छोटे और अधिक सटीक रूप से स्थित छेदों के लिए भी किया जा सकता है।) पीसीबी का निर्माण आम तौर पर एक तथाकथित कोर, एक बुनियादी दो तरफा पीसीबी से शुरू होता है। पहले दो से आगे की परतें इस बुनियादी बिल्डिंग ब्लॉक से खड़ी की गई हैं। यदि कोर के नीचे से लगातार दो और परतें लगाई जाती हैं, तो आपके पास 1-2 थ्रू, 1-3 थ्रू और एक थ्रू छेद हो सकता है। प्रत्येक प्रकार का वाया प्रत्येक स्टैकिंग चरण में ड्रिलिंग द्वारा बनाया जाता है। यदि एक परत कोर के ऊपर रखी गई है और दूसरी नीचे से रखी गई है, तो कॉन्फ़िगरेशन के माध्यम से 1-3, 2-3 और छेद के माध्यम से संभव है। उपयोगकर्ता को पीसीबी निर्माता की स्टैकिंग की अनुमत विधियों और संभावित वाया के बारे में जानकारी एकत्र करनी होगी। सस्ते बोर्डों के लिए, केवल छेद के माध्यम से बनाया जाता है और एंटीपैड (या क्लीयरेंस) को उन परतों पर रखा जाता है जिनका वाया से संपर्क नहीं होना चाहिए।

आईपीसी 4761

आईपीसी 4761 निम्नलिखित प्रकारों को परिभाषित करता है:

- टाइप I: टेंटेड वाया

- प्रकार II: तंबूयुक्त और ढका हुआ

- टाइप III-ए: प्लग किया गया, एक तरफ गैर-प्रवाहकीय सामग्री से सील किया गया

- टाइप III-बी: प्लग किया गया, दोनों तरफ गैर-प्रवाहकीय सामग्री से सील किया गया

- टाइप IV-a: प्लग किया गया और कवर किया गया, गैर-प्रवाहकीय सामग्री से सील किया गया और एक तरफ गीले सोल्डर मास्क से कवर किया गया

- टाइप IV-बी: प्लग किया गया और कवर किया गया, गैर-प्रवाहकीय सामग्री से सील किया गया और दोनों तरफ गीले सोल्डर मास्क से कवर किया गया

- प्रकार V: के माध्यम से भरा हुआ, गैर-प्रवाहकीय पेस्ट से भरा हुआ

- टाइप VI-ए: भरा हुआ और ढका हुआ, एक तरफ सूखी फिल्म या गीले सोल्डर मास्क से ढका हुआ

- टाइप VI-बी: भरा हुआ और ढका हुआ, दोनों तरफ सूखी फिल्म या गीले सोल्डर मास्क से ढका हुआ

- प्रकार VII: भरा हुआ और ढका हुआ, गैर-प्रवाहकीय पेस्ट से भरा हुआ और दोनों तरफ से ढका हुआ

असफल व्यवहार

यदि अच्छी तरह से बनाया गया है, तो पीसीबी वाया मुख्य रूप से कॉपर विद्युत् लेपन और पीसीबी के बीच समतल दिशा (जेड) के बीच अंतर विस्तार और संकुचन के कारण विफल हो जाएगा। यह अंतर विस्तार और संकुचन तांबे की परत में चक्रीय फटीग को प्रेरित करेगा, जिसके परिणामस्वरूप अंततः दरार फैल जाएगी और एक विद्युत विवृत परिपथ होगा। विभिन्न प्रारूप, सामग्री और पर्यावरणीय पैरामीटर इस गिरावट की दर को प्रभावित करेंगे।[5][6]मजबूती के माध्यम से सुनिश्चित करने के लिए, आईपीसी (इलेक्ट्रॉनिक्स) ने एक राउंड-रॉबिन अभ्यास प्रायोजित किया जिसने विफलता का समय कैलकुलेटर विकसित किया।[7]

एकीकृत परिपथ में वयास

एकीकृत परिपथ (आईसी) प्रारूप में, एक विद्युत रोधी के माध्यम से ऑक्साइड परत में एक छोटी सी विवृति होती है जो विभिन्न परतों के बीच एक प्रवाहकीय संयोजन की अनुमति देती है। एक एकीकृत परिपथ पर एक थ्रू जो पूरी तरह से सिलिकॉन वेफर या डाई से होकर गुजरता है उसे थ्रू-चिप थ्रू या थ्रू-सिलिकॉन थ्रू (टीएसवी) कहा जाता है। ग्लास बनाम सिलिकॉन पैकेजिंग की कम विद्युत हानि के कारण सेमीकंडक्टर पैकेजिंग के लिए कॉर्निंग ग्लास द्वारा थ्रू-ग्लास वायास (टीजीवी) का अध्ययन किया गया है।[8] सामान्यत: एक वाया जो धातु की सबसे निचली परत को प्रसार या पॉली से जोड़ता है, वह "संपर्क" सम्बन्धहै।

गैलरी

सीएडी में विद्युत् लेपित दोहरी परत। Vias makes EDA placement possible.

Bottom layer – Red

Top layer – Blue

यह भी देखें

- होल तकनीक के माध्यम से (टीएचटी)

- पृष्ठ आरोप प्रौद्योगिकी (एसएमटी)

- सिलिकॉन वाया के माध्यम से(टीएसवी)

- वाया के माध्यम से

- पारभरण

टिप्पणियाँ

- ↑ Through-holes per core. It is possible, though more expensive, to create blind or buried vias by using additional cores and lamination steps. It is also possible to backdrill and remove the plating from one side through to the desired layer, which leaves the physical hole as a through-hole, but creates the electrical equivalent of a blind via. If a PCB needs enough layers to justify blind and buried vias, it is probably also using small enough traces packed tightly enough to require (laser-drilled) microvias.

संदर्भ

- ↑ "PCB Vias: An In-Depth Guide". ePiccolo Engineering.

- ↑ "PCB design: A close look at facts and myths about thermal vias".

- ↑ Gautam, Deepak; Wager, Dave; Musavi, Fariborz; Edington, Murray; Eberle, Wilson; Dunford, Willa G. (17 March 2013). थर्मल विअस के साथ पावर कन्वर्टर्स में थर्मल प्रबंधन की समीक्षा. 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC). Long Beach, California, U.S.A: IEEE. doi:10.1109/APEC.2013.6520276.

- ↑ "Castellated Holes / Edge Plating PCB / Castellations". Hi-Tech Corp. 2011. Archived from the original on 2016-05-26. Retrieved 2013-01-02.

- ↑ C. Hillman, Understanding plated through via failures, Global SMT & Packaging – November 2013, pp 26-28, https://www.dfrsolutions.com/hubfs/Resources/services/Understanding_Plated_Through_Via_Failures.pdf?t=1514473946162

- ↑ C. Hillman, Reliable Plated Through Via Design and Fabrication, http://resources.dfrsolutions.com/White-Papers/Reliability/Reliable-Plated-Through-Via-Design-and-Fabrication1.pdf

- ↑ "Plated Through Hole (PTH) Fatigue calculator". DfR Solutions. Retrieved 2017-12-17.

- ↑ "Progress and Application of Through Glass Via (TGV) Technology" (PDF). corning.com. Retrieved 2019-08-08.

अग्रिम पठन

- "Tips for PCB Vias Design" (PDF) (Technical note). Quick-teck. 2014. EN-00417. Retrieved 2017-12-18.

- "Via Tenting - Overview of the variations". WE Online. Würth Elektronik GmbH & Co. KG. 2014. Printed Circuit Boards > Layout > Design Tip > Tenting. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Via Plugging - Overview of the variations". WE Online. Würth Elektronik GmbH & Co. KG. 2014. Printed Circuit Boards > Layout > Design Tip > Plugging. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Via Filling - Overview of the variations". WE Online. Würth Elektronik GmbH & Co. KG. 2013. Printed Circuit Boards > Layout > Design Tip > Filling. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Microvia Filling". WE Online. Würth Elektronik GmbH & Co. KG. 2015. Printed Circuit Boards > Layout > Design Tip > Microvia Filling. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- Dingler, Klaus; Musewski, Markus (2009-03-18). "Pluggen / Plugging". FED-Wiki (in Deutsch). Berlin, Germany: Fachverband Elektronik-Design e.V. (FED). Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Via Optimization Techniques for High-Speed Channel Designs" (PDF) (Application note). 1.0. Altera Corporation. May 2008. AN-529-1.0. Archived (PDF) from the original on 2017-12-18. Retrieved 2017-12-18.

- Chu, Jun (2017-04-11). "Controlled Depth Drilling, or Back Drilling". Online Documentation for Altium Products. Altium. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- Loughhead, Phil (2017-05-30). "Removing Unused Pads and Adding Teardrops". Online Documentation for Altium Products. Altium. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- Brooks, Douglas G.; Adam, Johannes (2017-02-09). PCB Trace and Via Temperatures: The Complete Analysis (2nd ed.). CreateSpace Independent Publishing Platform. ISBN 978-1541213524.

बाहरी संबंध

- Online Via Calculator (Ampacity, Capacitance, Impedance, Power Dissipation Calculation).