प्रोग्रामेबल रोम: Difference between revisions

No edit summary |

No edit summary |

||

| Line 17: | Line 17: | ||

एक विशिष्ट प्रोम "1" के रूप में पढ़ने वाले सभी बिट्स के साथ आता है। प्रोग्रामिंग के दौरान एक फ्यूज बिट को जलाने से फ्यूज़ को "ब्लो" (उड़ाकर) करके बिट को "0" के रूप में पढ़ा जाता है, जो एक अपरिवर्तनीय प्रक्रिया है। यदि नया डेटा "1"s को "0"s से बदल दिया जाए तो कुछ उपकरणों को "रीप्रोग्राम" किया जा सकता है। कुछ CPU निर्देश सेट (e.g 6502) ने '00' के ऑपरेशन कोड के साथ एक ब्रेक (BRK) निर्देश को परिभाषित करके इसका लाभ उठाया। ऐसे मामलों में जहां एक गलत निर्देश था, इसे बीआरके (BRK) के लिए "रीप्रोग्राम" किया जा सकता है जिससे सीपीयू एक पैच पर नियंत्रण स्थानांतरित कर सकता है। यह सही निर्देश को निष्पादित करेगा और बीआरके( BRK) के बाद निर्देश पर वापस आ जाएगा। | एक विशिष्ट प्रोम "1" के रूप में पढ़ने वाले सभी बिट्स के साथ आता है। प्रोग्रामिंग के दौरान एक फ्यूज बिट को जलाने से फ्यूज़ को "ब्लो" (उड़ाकर) करके बिट को "0" के रूप में पढ़ा जाता है, जो एक अपरिवर्तनीय प्रक्रिया है। यदि नया डेटा "1"s को "0"s से बदल दिया जाए तो कुछ उपकरणों को "रीप्रोग्राम" किया जा सकता है। कुछ CPU निर्देश सेट (e.g 6502) ने '00' के ऑपरेशन कोड के साथ एक ब्रेक (BRK) निर्देश को परिभाषित करके इसका लाभ उठाया। ऐसे मामलों में जहां एक गलत निर्देश था, इसे बीआरके (BRK) के लिए "रीप्रोग्राम" किया जा सकता है जिससे सीपीयू एक पैच पर नियंत्रण स्थानांतरित कर सकता है। यह सही निर्देश को निष्पादित करेगा और बीआरके( BRK) के बाद निर्देश पर वापस आ जाएगा। | ||

बिट सेल को एक उच्च-वोल्टेज पल्स को लागू करके प्रोग्राम किया जाता है जो गेट और सब्सट्रेट के बीच ऑक्साइड को तोड़ने के लिए गेट और पतले ऑक्साइड ट्रांजिस्टर | बिट सेल को एक उच्च-वोल्टेज पल्स को लागू करके प्रोग्राम किया जाता है जो गेट और सब्सट्रेट के बीच ऑक्साइड को तोड़ने के लिए गेट और पतले ऑक्साइड ट्रांजिस्टर {2 एनएम (ANM) मोटी ऑक्साइड के लिए लगभग 6 वी, या 30 एमवी/सेमी} के सब्सट्रेट के पार सामान्य ऑपरेशन के दौरान सामने नहीं आता है । ट्रांजिस्टर के गेट पर सकारात्मक वोल्टेज गेट के नीचे सब्सट्रेट में एक उलटा चैनल बनाता है, जिससे ऑक्साइड के माध्यम से एक टनलिंग (सुरंग की तरह) करंट प्रवाह होता है। करंट ऑक्साइड में अतिरिक्त जाल पैदा करता है, ऑक्साइड के माध्यम से करंट को बढ़ाता है और अंततः ऑक्साइड को पिघला देता है और गेट से सब्सट्रेट तक एक प्रवाहकीय चैनल बनाता है।प्रवाहकीय चैनल बनाने के लिए आवश्यक करंट लगभग 100 µA/100 nm2 है और ब्रेकडाउन लगभग 100 µ या उससे कम में होता है।<ref>{{cite web |url=http://www.sidense.com/images/stories/designcon_8_a_eval_embedded_nvm_65nm_and_beyond.pdf |title=Evaluating Embedded Non-Volatile Memory for 65nm and Beyond |author=Wlodek Kurjanowicz |year=2008 |access-date=2009-09-04 |url-status=dead |archive-url=https://web.archive.org/web/20160304025935/http://www.sidense.com/images/stories/designcon_8_a_eval_embedded_nvm_65nm_and_beyond.pdf |archive-date=2016-03-04 }}</ref> | ||

Revision as of 17:30, 1 September 2022

| कंप्यूटर मेमोरी और डेटा स्टोरेज प्रकार |

|---|

| वाष्पशील |

| गैर-वाष्पशील |

प्रोग्रामेबल रीड-ओनली मेमोरी डिजिटल मेमोरी का एक रूप है, जहां डिवाइस के निर्माण के बाद सामग्री को एक बार बदला जा सकता है। डेटा तब स्थायी होता है और इसे बदला नहीं जा सकता जब तक यह एक प्रकार की रीड-ओनली मेमोरी (ROM) है। आमतौर पर निम्न स्तर के कार्यक्रम(प्रोग्राम) जैसे कि फर्मवेयर या माइक्रोकोड में स्थायी डेटा को संगृहीत (स्टोर) करने के लिए डिजिटल इलेक्ट्रॉनिक उपकरणों में PROM का उपयोग किया जाता है । एक मानक ROM तथा PROM में महत्वपूर्ण अंतर यह है कि, डेटा को निर्माण के दौरान एक ROM में लिखा जाता है, जबकि एक PROM के साथ निर्माण के बाद डेटा को उनमें प्रोग्राम किया जाता है। इस प्रकार, ROM का उपयोग केवल बड़े उत्पादन के लिए किया जाता है जो अच्छी तरह से सत्यापित डेटा के साथ चलता है तथा PROMs का उपयोग वहां किया जाता है जहाँ आवश्यक मात्रा फ़ैक्टरी-प्रोग्राम किये गए ROM को किफायती नहीं बनाती है, या एक सिस्टम( प्रणाली ) के विकास के दौरान जिसे अंततः बड़े पैमाने पर उत्पादित संस्करण में ROM में परिवर्तित किया जा सकता है।

PROMS को प्रौद्योगिकी के आधार पर को खाली बनाया जाता है और वेफर पर अंतिम परीक्षण या सिस्टम में प्रोग्राम किया जा सकता है। खाली (ब्लैंक) प्रोम (PROM) चिप्स (chips) को प्रोम प्रोग्रामर (PROM programmer) नामक डिवाइस में प्लग करके प्रोग्राम किया जाता है। कंपनियां खाली प्रोम्स ( PROMs ) की आपूर्ति स्टाक में रख सकती हैं, और बड़ी मात्रा में प्रतिबद्धता से बचने के लिए अंतिम समय में उन्हें प्रोग्राम कर सकती हैं। इस प्रकार की मेमोरी (Memories) का उपयोग प्रायः माइक्रोकंट्रोलर, वीडियो गेम कंसोल, मोबाइल फोन, रेडियो-फ्रीक्वेंसी आइडेंटिफिकेशन (आरएफआईडी) टैग, इम्प्लांटेबल मेडिकल डिवाइस, हाई-डेफिनिशन मल्टीमीडिया इंटरफेस (एचडीएमआई/HDMI) और कई अन्य उपभोक्ता और ऑटोमोटिव इलेक्ट्रॉनिक्स उत्पादों में किया जाता है।

इतिहास

PROM का आविष्कार 1956 में वेन त्सिंग चाउ द्वारा किया गया था, जो न्यूयॉर्क के गार्डन सिटी में अमेरिकन बॉश अरमा कॉरपोरेशन के अरमा डिवीजन के लिए काम कर रहे थे।[1][2] आविष्कार की कल्पना संयुक्त राज्य वायु सेना के अनुरोध पर की गई थी, जो एटलस ई/एफ आईसीबीएम(Atlas E/F ICBM's) के एयरबोर्न डिजिटल कंप्यूटर में लक्ष्यीकरण स्थिरांक को संग्रहीत करने के अधिक लचीले और सुरक्षित तरीके के साथ आया था। पेटेंट और संबंधित तकनीक को कई वर्षों तक गोपनीयता आदेश के तहत आयोजित किया गया था, जबकि एटलस ई/एफ(Atlas E/F) संयुक्त राज्य अमेरिका आईसीबीएम(ICBM) बल की मुख्य परिचालन मिसाइल थी। एक प्रोम प्रोग्रामिंग की प्रक्रिया का जिक्र करते हुए बर्न शब्द, मूल पेटेंट में भी है, क्योंकि मूल कार्यान्वयन में से एक सर्किट असंतुलन उत्पन्न करने के लिए एक वर्तमान अधिभार के साथ डायोड के आंतरिक व्हिस्कर को सचमुच जला देना था। पहली प्रोम प्रोग्रामिंग मशीनें भी चाउ के निर्देशन में ARMA इंजीनियरों द्वारा विकसित की गईं जो ARMA के गार्डन सिटी लैब और एयर फोर्स (वायु सेना) स्ट्रेटेजिक एयर कमांड (SAC) मुख्यालय में स्थित थीं।

OTP (वन टाइम प्रोग्रामेबल) मेमोरी, एक विशेष प्रकार की गैर-वाष्पशील मेमोरी (नॉन-वोलेटाइल,NVM) है, जो डेटा को केवल एक बार मेमोरी में लिखने की अनुमति देती है। एक बार मेमोरी को प्रोग्राम करने के बाद यह शक्ति के नुकसान (यानी, गैर-वाष्पशील) पर अपना मूल्य बरकरार रखता है। ओटीपी(OTP)मेमोरी का उपयोग उन अनुप्रयोगों में किया जाता है जहां डेटा के विश्वसनीय और दोहराने योग्य पढ़ने की आवश्यकता होती है। उदाहरणों में एनालॉग (अनुरूप), सेंसर या डिस्प्ले सर्किटरी के लिए बूट कोड, एन्क्रिप्शन (encryption/कूटलेखन)कुंजी और कॉन्फ़िगरेशन (विन्यास), पैरामीटर(मापदंड) शामिल हैं। ओटीपी(OTP) एनवीएम (NVM)की यह विशेषता है कि अन्य प्रकार के एनवीएम जैसे एफ्यूज़ ( eFuse ) या ईईपीआरएम (EEPROM) की तुलना में कम शक्ति की पेशकश करके छोटे क्षेत्र के पदचिह्न स्मृति की संरचना करना। इस तरह के ओटीपी मेमोरी माइक्रोप्रोसेसर्स से उत्पादों में एप्लिकेशन को खोजता है और ड्राइवरों को पावर मैनेजमेंट आईसीएस (पीएमआईसी) तक प्रदर्शित करता है।

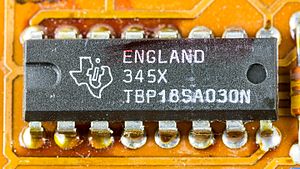

वाणिज्यिक रूप से उपलब्ध अर्धचालक (semiconductor) एंटीफ्यूज़-आधारित ओटीपी मेमोरी सरणियाँ कम से कम 1969 से मौजूद है तथा प्रारंभिक एंटीफ्यूज़ बिट कोशिकाएं प्रवाहकीय लाइनों को पार करने के बीच एक संधारित्र को उड़ाने पर निर्भर करती हैं। टेक्सास इंस्ट्रूमेंट्स ने 1979 में एक एमओएस (MOS) गेट ऑक्साइड ब्रेकडाउन एंटीफ्यूज़ विकसित किया। देखें US पेटेंट 4184207 - उच्च घनत्व फ्लोटिंग गेट विद्युत रूप से प्रोग्राम करने योग्य ROM और = 4151021 और idkey = कोई नहीं US पेटेंट 4151021 Archived 2018-04-27 at the Wayback Machine 1982 में एक डुअल-गेट-ऑक्साइड टू-ट्रांजिस्टर (2T) MOS एंटीफ्यूज पेश किया गया था चिप प्लानिंग पोर्टल प्रारंभिक ऑक्साइड ब्रेकडाउन टेक्नोलॉजीज (प्रौद्योगिकियों ) ने विभिन्न प्रकार के स्केलिंग, प्रोग्रामिंग, आकार और विनिर्माण समस्याओं का प्रदर्शन किया, जो इन प्रौद्योगिकियों के आधार पर मेमोरी उपकरणों (डिवाइसेस) के वॉल्यूम उत्पादन को रोकते है।

वन-टाइम प्रोग्रामेबल मेमोरी डिवाइस का दूसरा रूप उसी सेमीकंडक्टर (अर्धचालक) चिप का उपयोग पराबैंगनी-इरेज़ेबल प्रोग्रामेबल रीड-ओनली मेमोरी (UV-EPROM) के रूप में करता है ,लेकिन तैयार उपकरण को मिटाने के लिए आवश्यक पारदर्शी क्वार्ट्ज विंडो वाले महंगे सिरेमिक पैकेज के बजाय एक अपारदर्शी पैकेज में डाल दिया जाता है। इन उपकरणों को यूवी ईपीरोम (EPROM) भागों के समान तरीकों के साथ प्रोग्राम किया जाता है, जो कि कम खर्चीले होते हैं। एंबेडेड कंट्रोलर फील्ड-एरेजेबल और वन-टाइम स्टाइल दोनों में उपलब्ध हो सकते हैं , जिससे फ़ैक्टरी-प्रोग्राम किए गए मास्क ROM चिप्स के खर्च और लीड समय के बिना वॉल्यूम उत्पादन में लागत बचत की अनुमति मिलती है। केन अर्नोल्ड, एम्बेडेड कंट्रोलर हार्डवेयर डिज़ाइन, न्यूनेस, 2004, आईएसबीएन 1-878707-52-3, पेज 102

हालांकि एंटीफ्यूज़-आधारित प्रोम (PROM) दशकों से उपलब्ध है लेकिन यह 2001 तक मानक सीएमओ (CMOS) में उपलब्ध नहीं था, जब किलोपास टेक्नोलॉजी इंक ने एक मानक सीएमओएस प्रक्रिया का उपयोग करके 1 टी, 2 टी, और 3.5 टी एंटीफ्यूज़ बिट सेल प्रौद्योगिकियों का पेटेंट कराया ,जिससे PROM को लॉजिक CMOS चिप्स में एकीकृत किया जा सके। पहली प्रक्रिया नोड एंटीफ्यूज़ को मानक CMOs में लागू किया जा सकता है जो 0.18 um है। चूंकि गेट ऑक्साइड ब्रेकडाउन जंक्शन ब्रेकडाउन से कम है, इसलिए एंटीफ्यूज़ प्रोग्रामिंग तत्व बनाने के लिए विशेष प्रसार चरणों की आवश्यकता नहीं थी। 2005 में, सिडेंस द्वारा एक स्प्लिट चैनल एंटीफ्यूज डिवाइस [6] पेश किया गया था। (देखें US पेटेंट 7402855) यह स्प्लिट चैनल बिट सेल मोटे (IO) और पतले (गेट) ऑक्साइड उपकरणों को एक सामान्य पॉलीसिलिकॉन गेट के साथ एक ट्रांजिस्टर (1T) में जोड़ती है।

एक विशिष्ट प्रोम "1" के रूप में पढ़ने वाले सभी बिट्स के साथ आता है। प्रोग्रामिंग के दौरान एक फ्यूज बिट को जलाने से फ्यूज़ को "ब्लो" (उड़ाकर) करके बिट को "0" के रूप में पढ़ा जाता है, जो एक अपरिवर्तनीय प्रक्रिया है। यदि नया डेटा "1"s को "0"s से बदल दिया जाए तो कुछ उपकरणों को "रीप्रोग्राम" किया जा सकता है। कुछ CPU निर्देश सेट (e.g 6502) ने '00' के ऑपरेशन कोड के साथ एक ब्रेक (BRK) निर्देश को परिभाषित करके इसका लाभ उठाया। ऐसे मामलों में जहां एक गलत निर्देश था, इसे बीआरके (BRK) के लिए "रीप्रोग्राम" किया जा सकता है जिससे सीपीयू एक पैच पर नियंत्रण स्थानांतरित कर सकता है। यह सही निर्देश को निष्पादित करेगा और बीआरके( BRK) के बाद निर्देश पर वापस आ जाएगा।

बिट सेल को एक उच्च-वोल्टेज पल्स को लागू करके प्रोग्राम किया जाता है जो गेट और सब्सट्रेट के बीच ऑक्साइड को तोड़ने के लिए गेट और पतले ऑक्साइड ट्रांजिस्टर {2 एनएम (ANM) मोटी ऑक्साइड के लिए लगभग 6 वी, या 30 एमवी/सेमी} के सब्सट्रेट के पार सामान्य ऑपरेशन के दौरान सामने नहीं आता है । ट्रांजिस्टर के गेट पर सकारात्मक वोल्टेज गेट के नीचे सब्सट्रेट में एक उलटा चैनल बनाता है, जिससे ऑक्साइड के माध्यम से एक टनलिंग (सुरंग की तरह) करंट प्रवाह होता है। करंट ऑक्साइड में अतिरिक्त जाल पैदा करता है, ऑक्साइड के माध्यम से करंट को बढ़ाता है और अंततः ऑक्साइड को पिघला देता है और गेट से सब्सट्रेट तक एक प्रवाहकीय चैनल बनाता है।प्रवाहकीय चैनल बनाने के लिए आवश्यक करंट लगभग 100 µA/100 nm2 है और ब्रेकडाउन लगभग 100 µ या उससे कम में होता है।[3]

टिप्पणियाँ

- ↑ Han-Way Huang (5 December 2008). Embedded System Design with C805. Cengage Learning. p. 22. ISBN 978-1-111-81079-5. Archived from the original on 27 April 2018.

- ↑ Marie-Aude Aufaure; Esteban Zimányi (17 January 2013). Business Intelligence: Second European Summer School, eBISS 2012, Brussels, Belgium, July 15-21, 2012, Tutorial Lectures. Springer. p. 136. ISBN 978-3-642-36318-4. Archived from the original on 27 April 2018.

- ↑ Wlodek Kurjanowicz (2008). "Evaluating Embedded Non-Volatile Memory for 65nm and Beyond" (PDF). Archived from the original (PDF) on 2016-03-04. Retrieved 2009-09-04.

संदर्भ

- 1977 Intel Memory Design Handbook - archive.org

- Intel PROM datasheets - intel-vintage.info

- View the US "Switch Matrix" Patent #3028659 at US Patent Office or Google

- View Kilopass Technology Patent US "High density semiconductor memory cell and memory array using a single transistor and having variable gate oxide breakdown" Patent #6940751 at US Patent Office or Google

- View Sidense US "Split Channel Antifuse Array Architecture" Patent #7402855 at US Patent Office or Google

- View the US "Method of Manufacturing Semiconductor Integrated Circuits" Patent #3634929 at US Patent Office or Google

- CHOI et al. (2008). "New Non-Volatile Memory Structures for FPGA Architectures"

- For the Advantages and Disadvantages table, see Ramamoorthy, G: "Dataquest Insight: Nonvolatile Memory IP Market, Worldwide, 2008-2013", page 10. Gartner, 2009

यह भी देखें

- Eprom

- Eeprom

बाहरी संबंध

- Looking inside a 1970s PROM chip that stores data in microscopic fuse - shows die of a 256x4 MMI 5300 PROM