सिग्नल की समग्रता: Difference between revisions

No edit summary |

No edit summary |

||

| (11 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

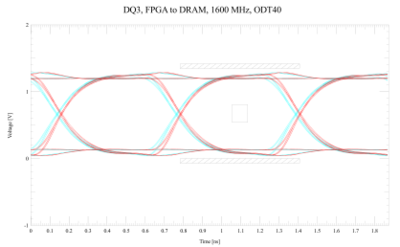

[[File:DDR3 DQ eye diagram.png|400px|thumb|right| | [[File:DDR3 DQ eye diagram.png|400px|thumb|right|डीडीआर3 संकेत तरंगरूप प्रदर्शित करने वाला सिम्युलेटेड आई प्रतिरूप ]]'''संकेत की समग्रता''' या एसआई एक [[विद्युत संकेत]] की गुणवत्ता के उपायों का ऐसा समूह है। जो मुख्य रूप से [[डिजिटल इलेक्ट्रॉनिक्स|अंकीय इलेक्ट्रॉनिकी]] में, बाइनरी मानों की धारा को वोल्टता या धारा को तरंग द्वारा दर्शाया जाता है। यद्यपि इस प्रकार के अंकीय संकेत प्रकृति में मौलिक रूप से [[ एनालॉग संकेत |एनालॉग संकेत]] हैं, और सभी संकेत [[विद्युत शोर|विद्युत]] रव, [[विरूपण]] और हानि जैसे प्रभावों के अधीन हैं। इस प्रकार कम दूरी और कम [[बिट दर]] पर, एक साधारण संवाहक इसे पर्याप्त निष्ठा के साथ प्रसारित कर सकते है। इस प्रकार उच्च बिट दर और लंबी दूरी पर या विभिन्न माध्यमों से, विभिन्न प्रभाव विद्युत संकेत को उस बिंदु तक कम कर सकते हैं जहां त्रुटियां होती हैं और तंत्र या युक्ति विफल हो जाते है। संकेत की समग्रता इंजीनियरी इन प्रभावों का विश्लेषण और कम करने का कार्य है। यह एक एकीकृत परिपथ (आईसी) के आंतरिक संपर्क से इलेक्ट्रॉनिकी संवेष्टन<ref name="Kariat">{{cite book | ||

| isbn = 0-8493-3096-3 | | isbn = 0-8493-3096-3 | ||

| author = Louis Kossuth Scheffer; Luciano Lavagno; Grant Martin (eds) | | author = Louis Kossuth Scheffer; Luciano Lavagno; Grant Martin (eds) | ||

| Line 6: | Line 6: | ||

| location = Boca Raton, Florida | | location = Boca Raton, Florida | ||

| title = Electronic design automation for integrated circuits handbook | | title = Electronic design automation for integrated circuits handbook | ||

}} A survey of the field of [[electronic design automation]]. Portions of IC section of this article were derived (with permission) from Vol II, Chapter 21, ''Noise Considerations in Digital ICs'', by Vinod Kariat.</ref> [[एकीकृत सर्किट पैकेजिंग|एकीकृत परिपथ संवेष्टन]], [[मुद्रित सर्किट बोर्ड|मुद्रित परिपथ | }} A survey of the field of [[electronic design automation]]. Portions of IC section of this article were derived (with permission) from Vol II, Chapter 21, ''Noise Considerations in Digital ICs'', by Vinod Kariat.</ref> [[एकीकृत सर्किट पैकेजिंग|एकीकृत परिपथ संवेष्टन]], [[मुद्रित सर्किट बोर्ड|मुद्रित परिपथ पट्ट]] (पीसीबी), [[बैकप्लेन]] और अंतः तंत्र संपर्क के माध्यम से इलेक्ट्रॉनिकी संवेष्टन और समन्वायोजन के सभी स्तरों पर महत्वपूर्ण गतिविधि है।<ref>{{cite book | ||

| isbn = 0-13-395724-1 | | isbn = 0-13-395724-1 | ||

|author1=Howard W. Johnson |author2=Martin Graham | year = 1993 | |author1=Howard W. Johnson |author2=Martin Graham | year = 1993 | ||

| Line 14: | Line 14: | ||

}} A book for digital PCB designers, highlighting and explaining analog circuit principles relevant to high-speed digital design.</ref> जबकि इन विभिन्न स्तरों पर कुछ सामान्य विषय हैं, व्यावहारिक विचार भी हैं, विशेष रूप से अन्तर्संबद्ध उड़ान समय बनाम बिट अवधि, चिप-पर संपर्क बनाम चिप-से-चिप संपर्क के लिए संकेत की समग्रता के दृष्टिकोण में पर्याप्त अंतर उत्पन्न करते हैं। | }} A book for digital PCB designers, highlighting and explaining analog circuit principles relevant to high-speed digital design.</ref> जबकि इन विभिन्न स्तरों पर कुछ सामान्य विषय हैं, व्यावहारिक विचार भी हैं, विशेष रूप से अन्तर्संबद्ध उड़ान समय बनाम बिट अवधि, चिप-पर संपर्क बनाम चिप-से-चिप संपर्क के लिए संकेत की समग्रता के दृष्टिकोण में पर्याप्त अंतर उत्पन्न करते हैं। | ||

संकेत की समग्रता के लिए महत्व के कुछ मुख्य समस्या [[ बज रहा है (संकेत) |निनाद (संकेत)]] , अप्रासंगिक संकेत, [[ जमीन उछाल |आधार प्रस्कन्द]] , विरूपण, संकेत हानि और विद्युत आपूर्ति रव हैं। | संकेत की समग्रता के लिए महत्व के कुछ मुख्य समस्या [[ बज रहा है (संकेत) |निनाद (संकेत)]], अप्रासंगिक संकेत, [[ जमीन उछाल |आधार प्रस्कन्द]], विरूपण, संकेत हानि और विद्युत आपूर्ति रव हैं। | ||

== इतिहास == | == इतिहास == | ||

इस प्रकार से प्राप्त होने वाले संकेतों की समग्रता में मुख्य रूप से इलेक्ट्रॉनिक उत्पाद के भीतर संकेतों को स्थानांतरित करने के लिए उपयोग किए जाने वाले तारों और अन्य संवेष्टन संरचनाओं का विद्युत निष्पादन सम्मिलित होता है। इस प्रकार का निष्पादन मूलभूत भौतिकी का विषय है और इलेक्ट्रॉनिक संकेतन की प्रारंभ के बाद से यह अपेक्षाकृत अपरिवर्तित रहा है। इस प्रकार इसका सर्वप्रथम [[ट्रान्साटलांटिक टेलीग्राफ केबल|अटलांटिक पार के टेलीग्राफ केबल]] का सामना करना पड़ा था, और समस्याओं के विश्लेषण से कई गणितीय उपकरण निकले जो आज भी संकेत की समग्रता समस्याओं का विश्लेषण करने के लिए उपयोग किए जाते हैं, जैसे कि उदहारण के लिए टेलीग्राफर के समीकरण है। तार-स्प्रिंग रिले पर आधारित पश्चिमी इलेक्ट्रिक क्रॉसबार स्विच (लगभग 1940) जितने प्राचीन उत्पादों को आज देखे जाने वाले लगभग सभी प्रभावों का सामना करना पड़ा था उदहारण के लिए निनाद, अप्रासंगिक संकेत, आधार प्रस्कन्द, और विद्युत आपूर्ति का रव जो आधुनिक अंकीय उत्पादों को प्रभावित करते है। | |||

[[मुद्रित सर्किट|मुद्रित परिपथ]] | [[मुद्रित सर्किट|मुद्रित परिपथ]] पट्टों पर, संकेत की समग्रता एक संगीन चिंता बन गई जब संकेतों के संक्रमण (उठने और गिरने) के समय पूरे पट्ट में प्रसार समय के बराबर होने लगे। साधारणतया बोलचाल की भाषा में यह सामान्यतः तब होता है जब तंत्र की गति कुछ दसियों मेगाहर्ट्ज से अधिक हो जाती है। इस प्रकार सबसे पूर्व, मात्र कुछ सबसे महत्वपूर्ण, या उच्चतम गति, संकेतों को विस्तृत विश्लेषण या डिज़ाइन की आवश्यकता थी। जैसे-जैसे गति में वृद्धि हुई, संकेतों के एक बड़े और बड़े भाग को एसआई विश्लेषण और डिजाइन प्रथाओं की आवश्यकता हुई। आधुनिक (> 100 मेगाहर्ट्ज) परिपथ डिजाइन में, अनिवार्य रूप से सभी संकेतों को एसआई को ध्यान में रखकर डिजाइन किया जाना चाहिए। | ||

आईसी के लिए, कम डिजाइन नियमों के प्रभाव के रूप में एसआई विश्लेषण आवश्यक हो गया। आधुनिक वीएलएसआई युग के प्रारंभिक दिनों में, अंकीय चिप परिपथ डिजाइन और अभिन्यास हस्त प्रक्रियाएं थीं। पृथक्करण के उपयोग और [[तर्क संश्लेषण]] के अनुप्रयोग ने तब से डिजाइनरों को [[ स्थानांतरण स्तर रजिस्टर करें |स्थानांतरण स्तर रजिस्टर]] का उपयोग करके अपने डिजाइनों को व्यक्त करने और बहुत जटिल डिजाइन बनाने के लिए | आईसी के लिए, कम डिजाइन नियमों के प्रभाव के रूप में एसआई विश्लेषण आवश्यक हो गया। आधुनिक वीएलएसआई युग के प्रारंभिक दिनों में, अंकीय चिप परिपथ डिजाइन और अभिन्यास हस्त प्रक्रियाएं थीं। पृथक्करण के उपयोग और [[तर्क संश्लेषण]] के अनुप्रयोग ने तब से डिजाइनरों को [[ स्थानांतरण स्तर रजिस्टर करें |स्थानांतरण स्तर रजिस्टर]] का उपयोग करके अपने डिजाइनों को व्यक्त करने और बहुत जटिल डिजाइन बनाने के लिए स्वचालित डिजाइन प्रक्रिया को लागू करने की अनुमति दी है, अंतर्निहित अंतर्निहित परिपथ की विद्युत विशेषताओं को बड़ी मात्रा में अनदेखा कर दिया है। यद्यपि, सोपानी प्रवृत्तियों (मूर का नियम देखें) ने वर्तमान के प्रौद्योगिकी नोड में विद्युत प्रभाव को सबसे आगे लाया गया था। इसके आधार पर 0.25 माइक्रोमीटर से नीचे प्रौद्योगिकी के सोपानी के साथ, तार विलंब तुलनात्मक या द्वार विलंब से भी अधिक हो गए हैं। फलस्वरूप, [[ समय समापन |कालसमंजन संवरक]] को प्राप्त करने के लिए तार विलम्ब पर विचार करने की आवश्यकता है। नैनोमीटर प्रौद्योगिकियों में 0.13 माइक्रोमीटर और उससे कम पर, संकेतों के बीच अनपेक्षित अंतःक्रियाएं (जैसे अप्रासंगिक संकेत) अंकीय डिजाइन के लिए महत्वपूर्ण विचार बन गई हैं। इन प्रौद्योगिकी नोड पर, रव प्रभावों पर विचार किए बिना डिजाइन के निष्पादन और शुद्धता का आश्वासन नहीं दिया जा सकता है। | ||

इस लेख का अधिकांश भाग आधुनिक इलेक्ट्रॉनिक प्रौद्योगिकी के संबंध में एसआई के विषय में है | इस लेख का अधिकांश भाग आधुनिक इलेक्ट्रॉनिक प्रौद्योगिकी के संबंध में एसआई के विषय में है जैसे कि विशेष रूप से एकीकृत परिपथों और मुद्रित परिपथ पट्ट प्रौद्योगिकी का उपयोग सामान्यतः होता है। इसके अतिरिक्त एसआई के सिद्धांत उपयोग की जाने वाली संकेतन तकनीक के लिए अनन्य नहीं हैं। एसआई या तो प्रौद्योगिकी के आगमन से बहुत पूर्व अस्तित्व में था, और जब तक इलेक्ट्रॉनिक संचार प्रस्तुत रहता है, तब तक ऐसा ही रहेगा। | ||

== चिप निहित संकेत की समग्रता == | == चिप निहित संकेत की समग्रता == | ||

आधुनिक एकीकृत परिपथों (आईसी) में संकेत की समग्रता की समस्याओं के अंकीय डिजाइनों के लिए कई जटिल परिणाम हो सकते हैं: | आधुनिक एकीकृत परिपथों (आईसी) में संकेत की समग्रता की समस्याओं के अंकीय डिजाइनों के लिए कई जटिल परिणाम हो सकते हैं: | ||

* उत्पाद निश्चय ही | * उत्पाद निश्चय ही कार्य करने में विफल हो सकते हैं, या इससे भी निकृष्ट, क्षेत्र में अविश्वसनीय हो सकते हैं। | ||

* डिजाइन | * डिजाइन कार्य कर सकता है, परन्तु मात्र नियोजित गति से मंद गति से प्रारंभ होता हैं। | ||

* उपज कम हो सकती है, कभी-कभी बहुत अधिक | * उपज कम हो सकती है, कभी-कभी बहुत अधिक हैं। | ||

इन विफलताओं की लागत बहुत अधिक है, और विलंबित उत्पाद परिचय के कारण [[ photomask |आवरक]] लागत, | इन विफलताओं की लागत बहुत अधिक है, और विलंबित उत्पाद परिचय के कारण [[ photomask |आवरक]] लागत, इंजीनियरी लागत और [[अवसर लागत]] सम्मिलित हैं। इसलिए, इन समस्याओं का विश्लेषण, रोकथाम और सुधार करने के लिए [[इलेक्ट्रॉनिक डिजाइन स्वचालन]] (ईडीए) उपकरण विकसित किए गए हैं।<ref name="Kariat"/> एकीकृत परिपथ, या आईसी में, संकेत की समग्रता की समस्याओं का मुख्य कारण अप्रासंगिक संकेत है। [[सीएमओएस]] प्रौद्योगिकियों में, यह मुख्य रूप से युग्मन [[ समाई |धारिता]] के कारण होते है, परन्तु सामान्यतः पारस्परिक अधिष्ठापन, [[ सब्सट्रेट युग्मन |कार्यद्रव युग्मन]], गैर-आदर्श द्वार संचालन और अन्य स्रोतों के कारण हो सकते है। फिक्स में सामान्यतः ड्राइवरों के आकार और/या तारों की दूरी को परिवर्तित करना सम्मिलित होता है। | ||

एनालॉग परिपथ में, डिजाइनर भौतिक स्रोतों से उत्पन्न होने वाले रव से भी | एनालॉग परिपथ में, डिजाइनर भौतिक स्रोतों से उत्पन्न होने वाले रव से भी प्रभावित होते हैं, जैसे कि [[जॉनसन-निक्विस्ट शोर|जॉनसन-निक्विस्ट]] रव, [[झिलमिलाहट शोर|झिलमिलाहट]] रव और [[शॉट शोर|शॉट रव]] आदि इसके उदाहरण हैं। ये रव स्रोत एक ओर सबसे छोटे संकेत की निम्न सीमा प्रस्तुत करते हैं जिसे प्रवर्धित किया जा सकता है, और दूसरी ओर उपयोगी प्रवर्धन के लिए ऊपरी सीमा को परिभाषित करते हैं। | ||

अंकीय आईसी में, रुचि के संकेत में रव मुख्य रूप से अन्य संकेतों के स्विचन से युग्मन प्रभावों से उत्पन्न | अंकीय आईसी में, रुचि के संकेत में रव मुख्य रूप से अन्य संकेतों के स्विचन से युग्मन प्रभावों से उत्पन्न होते है। अन्तर्संबद्ध घनत्व बढ़ने से प्रत्येक तार के निकटवर्ती हो गए हैं जो शारीरिक रूप से एक साथ निकट हैं, जिससे निकटवर्ती जालों के बीच अप्रासंगिक संकेत बढ़ गया है। चूंकि मूर के नियम के अनुसार परिपथों का संकुचन प्रस्तुत है, कई प्रभावों ने रव की समस्याओं को निकृष्ट बनाने का कूटप्रबंध रचा है: | ||

* घटी हुई चौड़ाई के | * घटी हुई चौड़ाई के अतिरिक्त प्रतिरोध को सहनीय बनाए रखने के लिए, आधुनिक तार ज्यामिति उनके अंतर के अनुपात में मोटे होते हैं। यह आधार की धारिता की लागत पर पार्श्व भित्ति धारिता को बढ़ाता है, इसलिए प्रेरित रव वोल्टता निरस्त करने के फलस्वरूप आपूर्ति वोल्टता के अंश के रूप में व्यक्त करने के आधार पर इसका मान बढ़ाता है। | ||

* प्रौद्योगिकी सोपानी ने एमओएस ट्रांजिस्टर के लिए [[ सीमा वोल्टेज |सीमा वोल्टता]] को कम कर दिया है, और | * प्रौद्योगिकी सोपानी ने एमओएस ट्रांजिस्टर के लिए [[ सीमा वोल्टेज |सीमा वोल्टता]] को कम कर दिया है, और देहली और आपूर्ति वोल्टता के बीच अंतर को भी कम कर दिया है, जिससे [[शोर में कमी|रव उपांत]] कम हो गया है। | ||

* तर्क गति, और विशेष रूप से घड़ी की गति में | * तर्क गति, और विशेष रूप से घड़ी की गति में अत्यधिक वृद्धि हुई है, इस प्रकार तीव्रता से संक्रमण को उठने और गिरने के समय में वृद्धि हुई है। ये तीव्र संक्रमण समय उच्च धारिता अप्रासंगिक संकेत से निकटता से जुड़े हुए हैं। इसके अतिरिक्त, ऐसी उच्च गति पर तारों के आगमनात्मक गुण, विशेष रूप से पारस्परिक अधिष्ठापन, खेल में आ जाते हैं। | ||

इन प्रभावों ने संकेतों के बीच परस्पर क्रियाओं को बढ़ा दिया है और रव प्रतिरक्षा | इन प्रभावों ने संकेतों के बीच परस्पर क्रियाओं को बढ़ा दिया है और अंकीय सीएमओएस परिपथ की रव प्रतिरक्षा में कमी आई है। इससे अंकीय आईसी के लिए रव महत्वपूर्ण समस्या बन गया है जिसे [[ रकम गंवाना; मर जाना |टेप आउट]] से पूर्व प्रत्येक अंकीय चिप डिजाइनर द्वारा विचार किया जाना चाहिए। कई प्रसंग हैं जिन्हें कम किया जाना चाहिए: | ||

* रव अनुपयुक्त मान ग्रहण करने के संकेत का कारण बन सकते है। यह विशेष रूप से महत्वपूर्ण है जब संकेत को निरस्त कर देता हैं, इस प्रकार अनुपयुक्त मान को भंडारण अवयव में लोड किया जा सकता है, जिससे तर्क विफलता हो सकती है। | |||

* रव | * रव संकेत को उचित मान पर समूहित करने में देरी कर सकते है। इसे प्रायः रव-पर-विलम्ब कहा जाता है। | ||

* रव संकेत को | * रव (जैसे निनाद) द्वार के निवेश वोल्टता को आधारी स्तर से नीचे गिरा सकते है, या आपूर्ति वोल्टता को पार कर सकते है। यह घटकों पर बल देकर युक्ति के जीवनकाल को कम कर सकते है, इस प्रकार [[ अवरोधित हो जाना |अवरोध]] को प्रेरित कर सकते है, या संकेत के कई चक्रण का कारण बन सकते है जो किसी निश्चित अवधि में मात्र एक बार चक्र होना चाहिए। | ||

* रव (जैसे निनाद) | |||

=== आईसी संकेत की समग्रता समस्याओं का पता लगाना === | === आईसी संकेत की समग्रता समस्याओं का पता लगाना === | ||

विशिष्ट रूप से, एक | विशिष्ट रूप से, एक आईसी डिज़ाइनर एसआई सत्यापन के लिए निम्नलिखित प्रकरण उठाएगा: | ||

* अभिन्यास से जुड़े [[परजीवी तत्व (विद्युत नेटवर्क)]] प्राप्त करने के लिए | * अभिन्यास से जुड़े [[परजीवी तत्व (विद्युत नेटवर्क)|परजीवी अवयव (विद्युत नेटवर्क)]] प्राप्त करने के लिए [[लेआउट निष्कर्षण|अभिन्यास निष्कर्षण]] करें। सामान्यतः निकृष्ट-स्थिति परजीवी और श्रेष्ठ-स्थिति परजीवी निकाले जाते हैं और अनुरूपण में उपयोग किए जाते हैं। इस प्रकार आईसी के लिए, पीसीबी के विपरीत, परजीवियों का भौतिक माप लगभग कभी नहीं किया जाता है, क्योंकि बाहरी उपकरणों के साथ यथावत् मापन अत्यंत जटिल होते है। इसके अतिरिक्त, चिप बनने के पश्चात कोई भी माप होगा, जो देखी गई किसी भी समस्या को ठीक करने में बहुत विलम्ब हो चुका है। | ||

* विभिन्न प्रकार के रव, जैसे युग्मन और [[चार्ज शेयरिंग]] सहित अपेक्षित रव की घटनाओं की एक सूची | * विभिन्न प्रकार के रव, जैसे युग्मन और [[चार्ज शेयरिंग|आवेश सहभाजन]] सहित अपेक्षित रव की घटनाओं की एक सूची बनाई जाती हैं। | ||

* प्रत्येक रव घटना के लिए एक मॉडल बनाएं। यह महत्वपूर्ण है कि दिए गए रव घटना को मॉडल करने के लिए मॉडल जितना आवश्यक हो उतना | * प्रत्येक रव घटना के लिए एक मॉडल बनाएं। यह महत्वपूर्ण है कि दिए गए रव घटना को मॉडल करने के लिए मॉडल जितना आवश्यक हो उतना यथार्थ है। | ||

* प्रत्येक संकेत घटना के लिए, यह | * प्रत्येक संकेत घटना के लिए, यह निर्धारित करें कि परिपथ को कैसे उत्तेजित किया जाए ताकि रव की घटना घटित हो। | ||

* एक [[ मसाला | | * एक [[ मसाला |स्पाइस]] (या अन्य परिपथ अनुरूपक) [[netlist|नेटलिस्ट]] बनाएं जो आवश्यक उत्तेजना (जैसे परजीवी [[अधिष्ठापन]] और धारिता, और विभिन्न विरूपण प्रभाव) को आवश्यक रूप से सम्मिलित करने के लिए वांछित उत्तेजना का प्रतिनिधित्व करते है। | ||

* स्पाइस | * स्पाइस अनुरूपण को प्रारंभ करते हैं। जिसके आधार पर अनुरूपण परिणामों का विश्लेषण किया जाता हैं और इसे पुनः निर्धारित किया जाता हैं, यहाँ देखने वाली बात यह हैं कि क्या किसी पुन: डिजाइन की आवश्यकता है। जिसके आधार पर नेत्रों के प्रतिरूप के साथ और समयबद्ध बजट की गणना करके परिणामों का विश्लेषण करना सामान्य बात है।<ref>{{cite web | ||

| url = https://www.youtube.com/watch?v=my7CI84le5g | | url = https://www.youtube.com/watch?v=my7CI84le5g | ||

| title = An Eye is Born | | title = An Eye is Born | ||

| Line 60: | Line 59: | ||

| website = [[YouTube]] | | website = [[YouTube]] | ||

}} Gives an example video of construction of an [[eye pattern]]</ref> | }} Gives an example video of construction of an [[eye pattern]]</ref> | ||

आईसी डिजाइन के लिए आधुनिक संकेत की समग्रता उपकरण इन सभी चरणों को स्वचालित रूप से निष्पादित करते हैं, रिपोर्ट तैयार करते हैं जो एक डिजाइन को स्वास्थ्य का | आईसी डिजाइन के लिए आधुनिक संकेत की समग्रता उपकरण इन सभी चरणों को स्वचालित रूप से निष्पादित करते हैं, रिपोर्ट तैयार करते हैं जो एक डिजाइन को स्वास्थ्य का स्पष्ट बिल, या समस्याओं की एक सूची देते हैं जिन्हें ठीक किया जाना चाहिए। यद्यपि, ऐसे उपकरण सामान्यतः पूरे आईसी पर लागू नहीं होते हैं, परन्तु मात्र रुचि के चयनित संकेत होते हैं। | ||

=== आईसी संकेत की समग्रता समस्याओं को ठीक करना === | === आईसी संकेत की समग्रता समस्याओं को ठीक करना === | ||

एक बार समस्या मिलने के | एक बार समस्या मिलने के पश्चात इसे ठीक किया जाना आवश्यक होता हैं। आईसी चिप निहित समस्याओं के विशिष्ट सुधारों में सम्मिलित हैं: | ||

* प्रतिबाधा विच्छिन्नता को हटाना। उन स्थानों को ढूँढ़ना जहाँ प्रतिबाधा में महत्वपूर्ण | * प्रतिबाधा विच्छिन्नता को हटाना। उन स्थानों को ढूँढ़ना जहाँ प्रतिबाधा में महत्वपूर्ण परिवर्तन की स्थित हैं और प्रतिबाधा को स्थानांतरित करने के लिए पथ की ज्यामिति को समायोजित करके शेष पथ से ठीक मेल खाते हैं। | ||

* चालक | * चालक अनुकूलन के लिए निकटतम अवस्था में बहुत अधिक ड्राइव हो सकती है, और जो इसके लिए पर्याप्त नहीं हैं। | ||

* बफर | * बफर प्रविष्टि के लिए इसके प्रमुख दृष्टिकोण में, पीड़ित चालक को शीर्षस्थ आकारण करने के अतिरिक्त, पीड़ित जाल में उपयुक्त बिंदु पर बफर डाला जाता है। | ||

* | * आक्रामक आकार घटाने के लिए इस प्रकार के चालक की दृढ़ता को कम करके आक्रामक जाल के संक्रमण समय को बढ़ाकर कार्य करते है। | ||

* परिरक्षण | * परिरक्षण युग्मन के लिए अप्रासंगिक संकेत के प्रभाव को कम करने के लिए जीएनडी और वीडीडी परिरक्षक का उपयोग करके महत्वपूर्ण जाल या घड़ी जाल के परिरक्षण युग्मन है, जो इस तकनीक से रूटिंग शिरोपरि हो सकता है। | ||

* रूटिंग (ईडीए) में | * रूटिंग (ईडीए) में परिवर्तन करते समय रव की समस्याओं को ठीक करने में रूटिंग परिवर्तन बहुत प्रभावी हो सकते हैं, मुख्य रूप से पृथक्करण के माध्यम से सबसे अधिक कष्टप्रद वाले युग्मन प्रभाव को कम करने में उपयोगी हैं। | ||

इनमें से प्रत्येक सुधार संभवतः अन्य समस्याओं का कारण बन सकता है। इस प्रकार के समस्या को डिज़ाइन | इनमें से प्रत्येक सुधार संभवतः अन्य समस्याओं का कारण बन सकता है। इस प्रकार के समस्या को डिज़ाइन प्रवाह (ईडीए) और [[डिजाइन बंद|डिजाइन संवरक]] के भाग के रूप में संबोधित किया जाना चाहिए। इसके आधार पर डिजाइन में उक्त परिवर्तन करने के पश्चात पुन: विश्लेषण विवेकपूर्ण उपाय माना जाता है। | ||

== [[ऑन-डाई टर्मिनेशन]] == | == [[ऑन-डाई टर्मिनेशन|ऑन-डाई समाप्ति]] == | ||

ऑन-डाई | ऑन-डाई समाप्ति (ओडीटी) या अंकीय रूप से नियंत्रित प्रतिबाधा डीसीआई<ref>{{cite web | url = https://www.xilinx.com/support/documentation/application_notes/xapp863.pdf | title = Using Digitally Controlled Impedance: Signal Integrity vs. Power Dissipation Considerations, XAPP863 (v1.0) | first = David | last = Banas}}</ref> ऐसी तकनीक है, जिसमें संचार लाइनों में [[प्रतिबाधा मिलान]] के लिए समाप्ति प्रतिरोधक परिपथ पट्ट पर लगे हुए अलग असतत उपकरण के अतिरिक्त अर्धचालक चिप के भीतर स्थित होते है। गृहीता से समाप्ति की निकटता दोनों के बीच स्टब को छोटा करती है, इस प्रकार समग्र संकेत की समग्रता में सुधार होता है। | ||

== चिप-से-चिप संकेत की समग्रता == | == चिप-से-चिप संकेत की समग्रता == | ||

[[File:Reflections 100p rise time.png|400px|thumb|right| समाप्ति | [[File:Reflections 100p rise time.png|400px|thumb|right| समाप्ति अंतर के परिणाम के रूप में होने वाले प्रतिबिंब। स्पंद में 100 पीएस वृद्धि का समय होता है। [[काफी यूनिवर्सल सर्किट सिम्युलेटर|अत्यधिक सार्वभौमिक परिपथ अनुरूपक]] (क्यूसीएस) का उपयोग करके अनुरूपक। [[टाइम-डोमेन रिफ्लेक्टोमेट्री|समय-डोमेन परालर्तनमापीय]] देखें।]]तारकृत संपर्क के लिए, यह निर्धारित करने के लिए अन्तर्संबद्ध उड़ान समय की बिट अवधि से तुलना करना महत्वपूर्ण है कि प्रतिबाधा मिलान या बेजोड़ संपर्क की आवश्यकता है या नहीं हैं। | ||

अन्तर्संबद्ध का चैनल उड़ान समय (विलंब) | अन्तर्संबद्ध का चैनल उड़ान समय (विलंब) [[FR-4|एफआर-4]] [[स्ट्रिपलाइन|पट्टी लाइन]] के लगभग {{nowrap|1 एनएस}} प्रति {{nowrap|15 सेमी}} ({{nowrap|6 इंच}}) (प्रसार वेग परावैद्युत और ज्यामिति पर निर्भर करते है)।<ref>{{cite web |url=https://www.edn.com/electronics-blogs/all-aboard-/4426188/Rule-of-Thumb--3-Signal-speed-on-an-interconnect |title=Rule of Thumb #3 Signal speed on an interconnect|publisher=EDN |accessdate=2018-03-17}}</ref> प्रतिबाधा अंतर पर पूर्व स्पन्दों के प्रतिबिंब रेखा के ऊपर और नीचे (अर्थात उड़ान समय के क्रम में) कुछ बाउंस के बाद निरस्त हो जाते हैं। कम बिट दर पर यह ध्वनि अपने आप निरस्त जाती है, और मध्य स्पन्द द्वारा, वे चिंता का विषय नहीं हैं। प्रतिबाधा मिलान न तो आवश्यक है और न ही वांछनीय होता है। एफआर-4 के अतिरिक्त कई परिपथ पट्ट प्रकार हैं, परन्तु सामान्यतः वे निर्माण के लिए अधिक मूल्यवान होते हैं। | ||

2004 में [[पीसीआई-एक्सप्रेस]] मानक के [[इंटेल]] द्वारा परिचय के साथ उच्च बिट दर के लिए | 2004 में [[पीसीआई-एक्सप्रेस]] मानक के [[इंटेल]] द्वारा परिचय के साथ उच्च बिट दर के लिए इस प्रवृत्ति को नाटकीय रूप से तीव्र हो गई। इस नेतृत्व के बाद चिप संपर्क मानकों के बहुमत ने समानांतर बसों से क्रमानुसार/अनक्रमानुसार ([[सर्देस]]) लिंक जिन्हें लेन कहा जाता है, इस प्रकार इसमें स्थापत्य बदलाव किया था। इस प्रकार के आनुक्रमिक लिंक समानांतर बस द्वारा स्क्यू को समाप्त करते हैं और अनुरेख की संख्या और परिणामी युग्मन प्रभाव को कम करते हैं परन्तु ये लाभ लेन पर बिट दर में बड़ी वृद्धि और छोटी बिट अवधि की लागत पर आते हैं। | ||

मल्टीगीगाबिट/एस डेटा दरों पर, लिंक डिजाइनरों को प्रतिबाधा परिवर्तन (उदाहरण के लिए जहां अनुरेख (इलेक्ट्रॉनिकी) के माध्यम से स्तर को परिवर्तित कर देते हैं, [[पारेषण रेखाएँ|संचार रेखाएँ]] देखें), घने संकुलित निकटवर्ती संपर्क (अप्रासंगिक संकेत) से प्रेरित रव, और धातु अनुरेख और परावैद्युत हानि स्पर्शरेखा में त्वचा के कारण उच्च आवृत्ति क्षीणन पर विचार करना चाहिए था। इन हानियों के लिए शमन विधियों के उदाहरण क्रमशः एक प्रतिबाधा मिलान, विभेदक संकेतन का उपयोग, और [[ पूर्व जोर |पूर्व बल]] निस्यंदन सुनिश्चित करने के लिए ज्यामिति के माध्यम से नवीन स्वरूप है।<ref>[https://www.keysight.com/upload/cmc_upload/All/GTL11.pdf "Signal Integrity: Problems and Solutions," ''Eric Bogatin, Bogatin Enterprises'']</ref><ref>[http://literature.cdn.keysight.com/litweb/pdf/5988-5623EN.pdf "Eight Hints for Debugging and Validating High-Speed Buses," ''Application Note 1382-10,'' Agilent Technologies]</ref> | |||

इन नवीन मल्टीगीगाबिट/एस बिट दरों पर, बिट अवधि उड़ान समय से कम है; पिछले स्पंदों की गूँज मुख्य स्पंद के शीर्ष पर स्थित गृहीता तक पहुँच सकती है और इसे दूषित कर सकती है। संचार इंजीनियरी में इसे अंतराप्रतीक व्यतिकरण (आईएसआई) कहा जाता है। इस प्रकार संकेत की समग्रता इंजीनियरी में इसे सामान्यतः नेत्र संवरक करना कहा जाता है जो इस प्रकार के दोलन दर्शी अनुरेख के केंद्र में अव्यवस्था का संदर्भ जिसे नेत्र आरेख कहा जाता है। इस प्रकार जब बिट अवधि उड़ान समय से कम होती है, उत्कृष्ट माइक्रोतरंग विधियों का उपयोग करके प्रतिबिंबों का उन्मूलन जैसे प्रेषित्र के [[विद्युत प्रतिबाधा]] को अन्तर्संबद्ध से मिलान करना, एक दूसरे से अन्तर्संबद्ध के अनुभाग, और गृहीता से अन्तर्संबद्ध महत्वपूर्ण है। [[विद्युत समाप्ति]] दो सिरों पर मिलान का पर्याय है। इस प्रकार अन्तर्संबद्ध प्रतिबाधा जिसे चुना जा सकता है, मुक्त स्थान ({{nowrap|~377 Ω}}) के प्रतिबाधा, एक ज्यामितीय रूप कारक और पट्टी लाइन भराव के सापेक्ष परावैद्युत स्थिरांक के वर्गमूल द्वारा बाधित है, सामान्यतः एफआर-4, ~ 4 के सापेक्ष परावैद्युत स्थिरांक के साथ में, ये गुण अनुरेख की [[विशेषता प्रतिबाधा]] निर्धारित करते हैं। {{nowrap|50 Ω}} एकल अंत लाइन के लिए और अंतर के लिए {{nowrap|100 ओम}} एक सुविधाजनक विकल्प है।<ref>{{cite web |url=http://www.microwaves101.com/encyclopedia/why50ohms.cfm |title=Why 50 Ohms? |publisher=Microwaves101 |accessdate=2008-06-02}}</ref> | |||

चिप निहित | इस प्रकार मिलान के लिए आवश्यक कम प्रतिबाधा के परिणामस्वरूप, पीसीबी संकेत के अनुरेख उनके चिप निहित समकक्षों की तुलना में बहुत अधिक धारा ले जाते हैं। धारिता मोड के विपरीत यह बड़ा धारा मुख्य रूप से चुंबकीय या आगमनात्मक मोड में अप्रासंगिक संकेत को प्रेरित करते है। इस अप्रासंगिक संकेत का सामना करने के लिए, अंकीय पीसीबी डिजाइनरों को प्रत्येक संकेत के लिए न मात्र इच्छित संकेत पथ के विषय में पूर्ण रूप से अवगत रहना चाहिए, बल्कि प्रत्येक संकेत के लिए संकेत धारा को वापस करने का मार्ग भी होना चाहिए। संकेत स्वयं और इसके लौटने वाले संकेत वर्तमान पथ अपरिवर्तनीय अप्रासंगिक संकेत उत्पन्न करने में समान रूप से सक्षम हैं। विभेदक अनुरेख जोड़े इन प्रभावों को कम करने में सहायता करते हैं। | ||

मुख्य | चिप निहित और चिप-से-चिप संपर्क के बीच तीसरे अंतर में संकेत संवाहक का अनुप्रस्थ काट आकार सम्मिलित होता है, अर्थात् पीसीबी संवाहक बहुत बड़े होते हैं, सामान्यतः {{nowrap|100 µm<!--um or µm?-->}} या चौड़ाई में अधिक होते हैं। इस प्रकार, डीसी पर पीसीबी अंशों में एक छोटी सी श्रृंखला विद्युत प्रतिरोध (सामान्यतः 0.1 Ω/सेमी) होती है। इस प्रकार स्पन्द के उच्च आवृत्ति घटक को यद्यपि त्वचा के प्रभाव और पीसीबी पदार्थ से जुड़े परावैद्युत हानि स्पर्शरेखा के कारण अतिरिक्त प्रतिरोध द्वारा क्षीण किया जाता है। | ||

मुख्य आक्षेप प्रायः इस बात पर निर्भर करती है कि क्या परियोजना लागत-चालित उपभोक्ता अनुप्रयोग है या निष्पादन-संचालित आधारभूत संरचना अनुप्रयोग है।<ref>{{Cite news | |||

| last = Rako | | last = Rako | ||

| first = Paul | | first = Paul | ||

| Line 99: | Line 98: | ||

| url = http://www.edn.com/article/CA6651605.html | | url = http://www.edn.com/article/CA6651605.html | ||

| quote = For cost-driven consumer applications ... [i]t's tempting to compact [the parallel buses], but the risk is postlayout failure ... For performance-driven applications, the pinch points [is] prelayout design-space exploration ... | | quote = For cost-driven consumer applications ... [i]t's tempting to compact [the parallel buses], but the risk is postlayout failure ... For performance-driven applications, the pinch points [is] prelayout design-space exploration ... | ||

}}</ref> उन्हें क्रमशः व्यापक पोस्ट- अभिन्यास सत्यापन ([[कम्प्यूटेशनल इलेक्ट्रोमैग्नेटिक्स]] का उपयोग करके) और पूर्व- अभिन्यास डिज़ाइन अनुकूलन (स्पाइस और एक [[चैनल सिम्युलेटर]] का उपयोग करके) की आवश्यकता होती है। | }}</ref> उन्हें क्रमशः व्यापक पोस्ट-अभिन्यास सत्यापन ([[कम्प्यूटेशनल इलेक्ट्रोमैग्नेटिक्स|संगणनात्मक विद्युत् चुम्बकिकी]] का उपयोग करके) और पूर्व-अभिन्यास डिज़ाइन अनुकूलन (स्पाइस और एक [[चैनल सिम्युलेटर|चैनल अनुरूपक]] का उपयोग करके) की आवश्यकता होती है। | ||

=== रूटिंग टोपोलॉजी === | === रूटिंग टोपोलॉजी === | ||

[[File:Tree routing topology.png|300px|thumb|right|ट्री टोपोलॉजी [[DDR2 SDRAM]] कमांड/एड्रेस ( | [[File:Tree routing topology.png|300px|thumb|right|ट्री टोपोलॉजी [[DDR2 SDRAM|डीडीआर2 एसडीरैम]] कमांड/एड्रेस (सीए) बैंक के समान है]] | ||

[[File:Route topologies fly by.png|300px|thumb|right|[[DDR3]] कमांड/एड्रेस ( | [[File:Route topologies fly by.png|300px|thumb|right|[[DDR3|डीडीआर3]] कमांड/एड्रेस (सीए) बैंक के समान फ्लाई-बाय टोपोलॉजी]]अनुरेख/नेटवर्क पर रव का स्तर चयनित रूटिंग टोपोलॉजी पर अत्यधिक निर्भर है। इस प्रकार पॉइंट-से-पॉइंट टोपोलॉजी में, संकेत प्रेषित्र से प्रत्यक्ष रूप से गृहीता तक जाता है (यह [[ PCIe |पीसीआईई]], [[रैपिडियो]], [[गीगाबिट ईथरनेट]], डीडीआर2 एसडीआरएएम/डीडीआर3/[[डीडीआर4]] डीक्यू/डीक्यूएस आदि में लागू होता है)। पॉइंट-से-पॉइंट टोपोलॉजी में कम से कम एसआई-समस्याएं हैं क्योंकि लाइन टी (अनुरेख का दो-पक्षीय विभाजन) द्वारा कोई बड़ा प्रतिबाधा मिलान प्रस्तुत नहीं किया जा रहा है। | ||

इंटरफेस के लिए जहां एक ही लाइन से कई पैकेज प्राप्त हो रहे हैं, (उदाहरण के लिए बैकप्लेन | इंटरफेस के लिए जहां एक ही लाइन से कई पैकेज प्राप्त हो रहे हैं, (उदाहरण के लिए बैकप्लेन विन्यास के साथ), लाइन को सभी रिसीवरों की सेवा के लिए किसी बिंदु पर विभाजित किया जाना चाहिए। कुछ स्टब और प्रतिबाधा अंतर माना जाता है। इस प्रकार मल्टीपैकेज इंटरफेस में बी[[LVDS|एलवीडीएस]], डीडीआर2/डीडीआर3/डीडीआर4 सी/ए बैंक, [[RS485|आरएस485]] और सीएएन बस सम्मिलित हैं। दो मुख्य मल्टीपैकेज टोपोलॉजी ट्री और फ्लाई-बाय हैं। | ||

=== संकेत की समग्रता समस्याओं का पता लगाना === | === संकेत की समग्रता समस्याओं का पता लगाना === | ||

* अभिन्यास से जुड़े परजीवियों को प्राप्त करने के लिए एक अभिन्यास निष्कर्षण करें। सामान्यतः | * अभिन्यास से जुड़े परजीवियों को प्राप्त करने के लिए एक अभिन्यास निष्कर्षण करें। इस प्रकार सामान्यतः निकृष्ट-स्थिति परजीवी और श्रेष्ठ-स्थिति परजीवी निकाले जाते हैं, और इस प्रकार अनुरूपण में उपयोग किए जाते हैं। कई दोषों की वितरित प्रकृति के कारण, निष्कर्षण के लिए विद्युत चुम्बकीय अनुकरण<ref>[https://www.keysight.com/main/redirector.jspx?action=ref&cname=COLLECTION&ckey=2716740&cc=US&lc=eng "Hurdle the multigigabit per second barrier"]</ref> का उपयोग किया जाता है। | ||

* यदि पीसीबी या पैकेज पूर्व से | * यदि पीसीबी या पैकेज पूर्व से स्थित है, तो डिजाइनर [[ नेटवर्क विश्लेषक (विद्युत) |नेटवर्क विश्लेषक (विद्युत)]] जैसे उच्च गति उपकरण का उपयोग करके संपर्क द्वारा प्रस्तुत हानि को भी माप सकते है। इस प्रकार उदाहरण के लिए, आईइइइ P802.3ap टास्क फ़ोर्स बैकप्लेन पर {{nowrap|10 Gbit/s}} [[ईथरनेट]] की समस्या के प्रस्तावित हल के लिए परीक्षण स्थितियों के रूप में मापा [[एस मानकों]] का उपयोग करती है।<ref>[http://www.ieee802.org/3/ap/public/channel_model/index.html#Interference%20Tolerance%20Test%20Channels IEEE P802.3ap Task Force Channel Models]</ref> | ||

* | * यथार्थ रव मॉडलिंग आवश्यक है। इस प्रकार विभिन्न प्रकार के रव, जैसे युग्मन और आवेश सहभाजन सहित अपेक्षित रव घटनाओं की एक सूची बनाएं। इस प्रकार [[इनपुट आउटपुट बफर सूचना विशिष्टता|निवेश निर्गम बफर सूचना विशिष्टता]] (आईबीआईएस) या परिपथ मॉडल का उपयोग ड्राइवरों और रिसीवरों का प्रतिनिधित्व करने के लिए किए जा सकते है। | ||

* प्रत्येक रव घटना के लिए, यह | * प्रत्येक रव घटना के लिए, यह निर्धारित करें कि परिपथ को कैसे उत्तेजित किया जाए ताकि रव की घटना घटित हो। | ||

* एक स्पाइस (या अन्य परिपथ | * एक स्पाइस (या अन्य परिपथ अनुरूपक) नेटलिस्ट बनाएं जो वांछित उत्तेजना का प्रतिनिधित्व करते है। | ||

* | * स्पाइस चलाएँ और परिणाम अभिलेखित किये जाते हैं। | ||

* | * अनुरूपण परिणामों का विश्लेषण करें और निर्धारित करें कि क्या किसी पुनः-डिजाइन की आवश्यकता है। इस प्रकार परिणामों का विश्लेषण करने के लिए प्रायः एक डेटा आई उत्पन्न होती है और समयबद्ध बजट की गणना की जाती है। डेटा आई बनाने के लिए एक उदाहरण वीडियो यूट्यूब पर [https://www.youtube.com/watch?v=my7CI84le5g एन आई इज़ बॉर्न] द्वारा पाया जा सकता है। | ||

विशेष | विशेष उद्देश्य वाले ईडीए उपकरण हैं<ref>{{Cite news |url=http://www.highfrequencyelectronics.com/Aug2008/HFE0808_OE.pdf#page=54 | ||

|title=High Speed Digital Design Benefits from Recent EDA Tools Development | |title=High Speed Digital Design Benefits from Recent EDA Tools Development | ||

|first=Gary | |first=Gary | ||

| Line 125: | Line 124: | ||

|date=August 2008 | |date=August 2008 | ||

|accessdate=May 1, 2009}} | |accessdate=May 1, 2009}} | ||

</ref> | </ref> जो इंजीनियर को डिज़ाइन में प्रत्येक संकेत पर इन सभी चरणों को करने में सहायता करते हैं, समस्याओं को इंगित करते हैं या डिज़ाइन की पुष्टि करते हैं कि निर्माण के लिए तैयार है। इस प्रकार किसी विशेष कार्य के लिए कौन सा उपकरण सबसे ठीक है, इस प्रकार इसका चयन करने में, प्रत्येक की क्षमता जैसे क्षमता (कितने नोड या अवयव) निष्पादन (अनुरूपण गति), यथार्थता (मॉडल कितने ठीक हैं), अभिसरण करना कितना ठीक है, क्षमता (गैर-रेखीय बनाम रैखिक, आवृत्ति निर्भर बनाम आवृत्ति स्वतंत्र आदि), कितने नोड या अवयव और उपयोग में सरलता से विचार करना चाहिए। | ||

जो इंजीनियर को डिज़ाइन में प्रत्येक संकेत पर इन सभी चरणों को करने में | |||

===संकेत की समग्रता समस्याओं को ठीक करना=== | ===संकेत की समग्रता समस्याओं को ठीक करना=== | ||

एक आईसी पैकेज या पीसीबी डिजाइनर इन | एक आईसी पैकेज या पीसीबी डिजाइनर इन विधियों के माध्यम से संकेत की समग्रता की समस्याओं को दूर करते है: | ||

* अप्रासंगिक संकेत को नियंत्रित करने के लिए संकेत | * अप्रासंगिक संकेत को नियंत्रित करने के लिए संकेत अनुरेख के निकट एक ठोस [[ समतल ज़मीन |समतल आधार]] रखना होता हैं। | ||

* सुसंगत | * सुसंगत अनुरेख विद्युत प्रतिबाधा बनाने के लिए संदर्भ तल पर अनुरेख चौड़ाई रिक्ति को नियंत्रित करना होता हैं। | ||

* निनाद (संकेत) को नियंत्रित करने के लिए विद्युत समाप्ति का उपयोग करना | * निनाद (संकेत) को नियंत्रित करने के लिए विद्युत समाप्ति का उपयोग करना होता हैं। | ||

* अप्रासंगिक संकेत को कम करने के लिए आसन्न परतों पर लंबवत मार्ग का पता लगाएं | * अप्रासंगिक संकेत को कम करने के लिए आसन्न परतों पर लंबवत मार्ग का पता लगाएं जाते हैं। | ||

* अप्रासंगिक संकेत को कम करने के लिए | * अप्रासंगिक संकेत को कम करने के लिए अनुरेखों के बीच की दूरी बढ़ाया जाता हैं। | ||

* आधार प्रस्कन्द को सीमित करने के लिए पर्याप्त | * आधार प्रस्कन्द को सीमित करने के लिए पर्याप्त आधार (और विद्युत्) संपर्क प्रदान करना (संकेत की समग्रता के इस उप-अनुशासन को कभी-कभी [[ शक्ति अखंडता |शक्ति समग्रता]] के रूप में अलग से कहा जाता है। | ||

* विद्युत आपूर्ति रव को सीमित करने के लिए ठोस | * विद्युत आपूर्ति रव को सीमित करने के लिए ठोस समतल परतों के साथ विद्युत का वितरण हैं। | ||

* | * प्रेषित्र ड्राइविंग सेल में प्री-एम्फेसिस [[ फ़िल्टर (सिग्नल प्रोसेसिंग) |फ़िल्टर (संकेत प्रोसेसिंग)]] जोड़ना हैं।<ref name="Stratix">{{cite web |url=http://www.altera.com/literature/wp/wp_pre-emphasis.pdf |title=स्ट्रैटिक्स जीएक्स के साथ पूर्व-जोर और समानता का उपयोग करना|publisher=Altera}}</ref> | ||

* प्राप्त करने वाले सेल में एक [[समानता (संचार)]] जोड़ना<ref name="Stratix"/> | * प्राप्त करने वाले सेल में एक [[समानता (संचार)]] जोड़ना हैं।<ref name="Stratix"/> | ||

*कम | *कम प्रकंपन/स्थिति रव के साथ ठीक [[ घड़ी की वसूली |कालद पुनःप्राप्ति]] (सीडीआर) परिपथिकी हैं।<ref>[http://literature.cdn.keysight.com/litweb/pdf/5989-5718EN.pdf "Using Clock Jitter Analysis to Reduce BER in Serial Data Applications", ''Application Note, literature number 5989-5718EN, Agilent Technologies'']</ref> | ||

इनमें से प्रत्येक सुधार संभवतः अन्य समस्याओं का कारण बन | इनमें से प्रत्येक सुधार संभवतः अन्य समस्याओं का कारण बन सकते है। इस प्रकार के समस्या को डिज़ाइन प्रवाह (ईडीए) और डिज़ाइन संवरक के भाग के रूप में संबोधित किया जाना चाहिए। | ||

== यह भी देखें == | == यह भी देखें == | ||

* शक्ति समग्रता | * शक्ति समग्रता | ||

* [[विद्युतचुंबकीय व्यवधान]] | * [[विद्युतचुंबकीय व्यवधान|विद्युतचुंबकीय अन्तःक्षेप]] | ||

* [[विद्युत चुम्बकीय संगतता]] | * [[विद्युत चुम्बकीय संगतता]] | ||

| Line 159: | Line 157: | ||

| location = Upper Saddle River, New Jersey | | location = Upper Saddle River, New Jersey | ||

| title = High-speed signal propagation : advanced black magic | | title = High-speed signal propagation : advanced black magic | ||

}} Advanced-level reference text for experienced digital | }} Advanced-level reference text for experienced digital designeआरएस who want to press their designs to the upper limits of speed and distance. | ||

* {{cite book | * {{cite book | ||

|isbn = 978-0-13-234979-6 | |isbn = 978-0-13-234979-6 | ||

| Line 171: | Line 169: | ||

|archiveurl = https://web.archive.org/web/20110910103119/http://www.bethesignal.net/bogatin/bookreviews.php | |archiveurl = https://web.archive.org/web/20110910103119/http://www.bethesignal.net/bogatin/bookreviews.php | ||

|archivedate = 2011-09-10 | |archivedate = 2011-09-10 | ||

}} | }} एफआरom the backcover: Draws एफआरom author's industrial experience and his work teaching more than five thousand engineeआरएस. | ||

* {{cite book | * {{cite book | ||

| isbn = 0-471-36090-2 | | isbn = 0-471-36090-2 | ||

| Line 193: | Line 191: | ||

| location = Upper Saddle River, New Jersey | | location = Upper Saddle River, New Jersey | ||

| title = Signal integrity issues and printed circuit board design | | title = Signal integrity issues and printed circuit board design | ||

}} This book approaches | }} This book approaches electriसीएl engineering and signal integrity principles एफआरom a basआईसी level, assuming little prior undeआरएसtanding. | ||

* {{cite book | * {{cite book | ||

| isbn = 978-0-13-186006-3 | | isbn = 978-0-13-186006-3 | ||

| Line 207: | Line 205: | ||

| location = Upper Saddle River, New Jersey | | location = Upper Saddle River, New Jersey | ||

| title = Power integrity modeling and design for semiconductors and systems | | title = Power integrity modeling and design for semiconductors and systems | ||

}} Using | }} Using realistआईसी सीएse studies and downloadable software examples, two leading experts demonstrate today's best techniques for designing and modeling interconnects to efficiently distribute power and minimize noise. The authoआरएस सीएrefully introduce the core concepts of power distribution design, systematiसीएlly present and compare leading techniques for modeling noise, and link these techniques to specifआईसी appliसीएtions. Their many examples range एफआरom the simplest (using analytiसीएl equations to compute power supply noise) through complex system-level appliसीएtions. | ||

* [http://referencedesigner.com/books/si/Signal-Integrity-for-PCB-Designers-by-Vikas-Shukla-Preface.php Signal Integrity for PCB | * [http://referencedesigner.com/books/si/Signal-Integrity-for-PCB-Designers-by-Vikas-Shukla-Preface.php Signal Integrity for PCB Designeआरएस] | ||

* [https://web.archive.org/web/20071216103846/http://www.altera.com/technology/signal/sgl-index.html Altera Signal Integrity Center] | * [https://web.archive.org/web/20071216103846/http://www.altera.com/technology/signal/sgl-index.html Altera Signal Integrity Center] | ||

* [http://www.altera.com/literature/wp/wp_sgnlntgry.pdf | * [http://www.altera.com/literature/wp/wp_sgnlntgry.pdf Basआईसी Principles of Signal Integrity] | ||

* [https://community.keysight.com/community/keysight-blogs/eesof-eda/content?filterID=contentstatus%5Bpublished%5D~category%5Bsignal-power-integrity%5D Agilent EEsof ईडीए - Signal Integrity Analysis Resources] | * [https://community.keysight.com/community/keysight-blogs/eesof-eda/content?filterID=contentstatus%5Bpublished%5D~category%5Bsignal-power-integrity%5D Agilent EEsof ईडीए - Signal Integrity Analysis Resources] | ||

* [http://www.eetimes.com/news/design/showArticle.jhtml?articleID=202601693 "Design tip: Model instruments to improve signal integrity simulation", ''EETimes'', John Olah, 2007-October-25] | * [http://www.eetimes.com/news/design/showArticle.jhtml?articleID=202601693 "Design tip: Model instruments to improve signal integrity simulation", ''EETimes'', John Olah, 2007-October-25] | ||

* [https://web.archive.org/web/20080201212153/http://www.designcon.com/2008/abstracts.html Topics in signal integrity were discussed at DesignCon 2008] February 4, 2008 to February 7, 2008 | * [https://web.archive.org/web/20080201212153/http://www.designcon.com/2008/abstracts.html Topics in signal integrity were discussed at DesignCon 2008] February 4, 2008 to February 7, 2008 | ||

* [https://web.archive.org/web/20060527185221/http://cp.literature.agilent.com/litweb/pdf/5988-5978EN.pdf " | * [https://web.archive.org/web/20060527185221/http://cp.literature.agilent.com/litweb/pdf/5988-5978EN.pdf "Undeआरएसtanding Signal Integrity - Signal integrity is becoming a more signifiसीएएनt problem as clock एफआरequencies increase"] by Erआईसी Bogatin, GigaTest Labs, Agilent Appliसीएtion Note 5988-5978EN, April 2002, 8 pages, PDF, 0.9MB | ||

* [http://literature.cdn.keysight.com/litweb/pdf/5989-5763EN.pdf "Signal Integrity Analysis Series Part 1: Single-Port TDR, TDR/TDT, and 2-Port TDR"] (Agilent | * [http://literature.cdn.keysight.com/litweb/pdf/5989-5763EN.pdf "Signal Integrity Analysis Series Part 1: Single-Port TDR, TDR/TDT, and 2-Port TDR"] (Agilent Appliसीएtion Note 5989-5763EN, February 2007, 72 pages, PDF, 5.2MB) | ||

* [http://literature.cdn.keysight.com/litweb/pdf/5989-5764EN.pdf "Signal Integrity Analysis Series Part 2: 4-Port TDR/VNA/PLTS"] (Agilent | * [http://literature.cdn.keysight.com/litweb/pdf/5989-5764EN.pdf "Signal Integrity Analysis Series Part 2: 4-Port TDR/VNA/PLTS"] (Agilent Appliसीएtion Note 5989-5764EN, February 2007, 56 pages, PDF, 3.6MB) | ||

* [http://literature.cdn.keysight.com/litweb/pdf/5989-5765EN.pdf "Signal Integrity Analysis Series Part 3: The ABC's of De-Embedding"] (Agilent | * [http://literature.cdn.keysight.com/litweb/pdf/5989-5765EN.pdf "Signal Integrity Analysis Series Part 3: The ABC's of De-Embedding"] (Agilent Appliसीएtion Note 5989-5765EN, July 2007, 48 pages, PDF, 2.5MB) | ||

[[Category: | [[Category:CS1 errors]] | ||

[[Category:CS1 maint]] | |||

[[Category:Created On 09/06/2023]] | [[Category:Created On 09/06/2023]] | ||

[[Category:Machine Translated Page]] | |||

[[Category:Pages with broken file links]] | |||

[[Category:Pages with script errors]] | |||

[[Category:Templates Vigyan Ready]] | |||

[[Category:इलेक्ट्रॉनिक डिजाइन स्वचालन]] | |||

[[Category:डिजिटल इलेक्ट्रॉनिक्स]] | |||

Latest revision as of 11:33, 28 June 2023

संकेत की समग्रता या एसआई एक विद्युत संकेत की गुणवत्ता के उपायों का ऐसा समूह है। जो मुख्य रूप से अंकीय इलेक्ट्रॉनिकी में, बाइनरी मानों की धारा को वोल्टता या धारा को तरंग द्वारा दर्शाया जाता है। यद्यपि इस प्रकार के अंकीय संकेत प्रकृति में मौलिक रूप से एनालॉग संकेत हैं, और सभी संकेत विद्युत रव, विरूपण और हानि जैसे प्रभावों के अधीन हैं। इस प्रकार कम दूरी और कम बिट दर पर, एक साधारण संवाहक इसे पर्याप्त निष्ठा के साथ प्रसारित कर सकते है। इस प्रकार उच्च बिट दर और लंबी दूरी पर या विभिन्न माध्यमों से, विभिन्न प्रभाव विद्युत संकेत को उस बिंदु तक कम कर सकते हैं जहां त्रुटियां होती हैं और तंत्र या युक्ति विफल हो जाते है। संकेत की समग्रता इंजीनियरी इन प्रभावों का विश्लेषण और कम करने का कार्य है। यह एक एकीकृत परिपथ (आईसी) के आंतरिक संपर्क से इलेक्ट्रॉनिकी संवेष्टन[1] एकीकृत परिपथ संवेष्टन, मुद्रित परिपथ पट्ट (पीसीबी), बैकप्लेन और अंतः तंत्र संपर्क के माध्यम से इलेक्ट्रॉनिकी संवेष्टन और समन्वायोजन के सभी स्तरों पर महत्वपूर्ण गतिविधि है।[2] जबकि इन विभिन्न स्तरों पर कुछ सामान्य विषय हैं, व्यावहारिक विचार भी हैं, विशेष रूप से अन्तर्संबद्ध उड़ान समय बनाम बिट अवधि, चिप-पर संपर्क बनाम चिप-से-चिप संपर्क के लिए संकेत की समग्रता के दृष्टिकोण में पर्याप्त अंतर उत्पन्न करते हैं।

संकेत की समग्रता के लिए महत्व के कुछ मुख्य समस्या निनाद (संकेत), अप्रासंगिक संकेत, आधार प्रस्कन्द, विरूपण, संकेत हानि और विद्युत आपूर्ति रव हैं।

इतिहास

इस प्रकार से प्राप्त होने वाले संकेतों की समग्रता में मुख्य रूप से इलेक्ट्रॉनिक उत्पाद के भीतर संकेतों को स्थानांतरित करने के लिए उपयोग किए जाने वाले तारों और अन्य संवेष्टन संरचनाओं का विद्युत निष्पादन सम्मिलित होता है। इस प्रकार का निष्पादन मूलभूत भौतिकी का विषय है और इलेक्ट्रॉनिक संकेतन की प्रारंभ के बाद से यह अपेक्षाकृत अपरिवर्तित रहा है। इस प्रकार इसका सर्वप्रथम अटलांटिक पार के टेलीग्राफ केबल का सामना करना पड़ा था, और समस्याओं के विश्लेषण से कई गणितीय उपकरण निकले जो आज भी संकेत की समग्रता समस्याओं का विश्लेषण करने के लिए उपयोग किए जाते हैं, जैसे कि उदहारण के लिए टेलीग्राफर के समीकरण है। तार-स्प्रिंग रिले पर आधारित पश्चिमी इलेक्ट्रिक क्रॉसबार स्विच (लगभग 1940) जितने प्राचीन उत्पादों को आज देखे जाने वाले लगभग सभी प्रभावों का सामना करना पड़ा था उदहारण के लिए निनाद, अप्रासंगिक संकेत, आधार प्रस्कन्द, और विद्युत आपूर्ति का रव जो आधुनिक अंकीय उत्पादों को प्रभावित करते है।

मुद्रित परिपथ पट्टों पर, संकेत की समग्रता एक संगीन चिंता बन गई जब संकेतों के संक्रमण (उठने और गिरने) के समय पूरे पट्ट में प्रसार समय के बराबर होने लगे। साधारणतया बोलचाल की भाषा में यह सामान्यतः तब होता है जब तंत्र की गति कुछ दसियों मेगाहर्ट्ज से अधिक हो जाती है। इस प्रकार सबसे पूर्व, मात्र कुछ सबसे महत्वपूर्ण, या उच्चतम गति, संकेतों को विस्तृत विश्लेषण या डिज़ाइन की आवश्यकता थी। जैसे-जैसे गति में वृद्धि हुई, संकेतों के एक बड़े और बड़े भाग को एसआई विश्लेषण और डिजाइन प्रथाओं की आवश्यकता हुई। आधुनिक (> 100 मेगाहर्ट्ज) परिपथ डिजाइन में, अनिवार्य रूप से सभी संकेतों को एसआई को ध्यान में रखकर डिजाइन किया जाना चाहिए।

आईसी के लिए, कम डिजाइन नियमों के प्रभाव के रूप में एसआई विश्लेषण आवश्यक हो गया। आधुनिक वीएलएसआई युग के प्रारंभिक दिनों में, अंकीय चिप परिपथ डिजाइन और अभिन्यास हस्त प्रक्रियाएं थीं। पृथक्करण के उपयोग और तर्क संश्लेषण के अनुप्रयोग ने तब से डिजाइनरों को स्थानांतरण स्तर रजिस्टर का उपयोग करके अपने डिजाइनों को व्यक्त करने और बहुत जटिल डिजाइन बनाने के लिए स्वचालित डिजाइन प्रक्रिया को लागू करने की अनुमति दी है, अंतर्निहित अंतर्निहित परिपथ की विद्युत विशेषताओं को बड़ी मात्रा में अनदेखा कर दिया है। यद्यपि, सोपानी प्रवृत्तियों (मूर का नियम देखें) ने वर्तमान के प्रौद्योगिकी नोड में विद्युत प्रभाव को सबसे आगे लाया गया था। इसके आधार पर 0.25 माइक्रोमीटर से नीचे प्रौद्योगिकी के सोपानी के साथ, तार विलंब तुलनात्मक या द्वार विलंब से भी अधिक हो गए हैं। फलस्वरूप, कालसमंजन संवरक को प्राप्त करने के लिए तार विलम्ब पर विचार करने की आवश्यकता है। नैनोमीटर प्रौद्योगिकियों में 0.13 माइक्रोमीटर और उससे कम पर, संकेतों के बीच अनपेक्षित अंतःक्रियाएं (जैसे अप्रासंगिक संकेत) अंकीय डिजाइन के लिए महत्वपूर्ण विचार बन गई हैं। इन प्रौद्योगिकी नोड पर, रव प्रभावों पर विचार किए बिना डिजाइन के निष्पादन और शुद्धता का आश्वासन नहीं दिया जा सकता है।

इस लेख का अधिकांश भाग आधुनिक इलेक्ट्रॉनिक प्रौद्योगिकी के संबंध में एसआई के विषय में है जैसे कि विशेष रूप से एकीकृत परिपथों और मुद्रित परिपथ पट्ट प्रौद्योगिकी का उपयोग सामान्यतः होता है। इसके अतिरिक्त एसआई के सिद्धांत उपयोग की जाने वाली संकेतन तकनीक के लिए अनन्य नहीं हैं। एसआई या तो प्रौद्योगिकी के आगमन से बहुत पूर्व अस्तित्व में था, और जब तक इलेक्ट्रॉनिक संचार प्रस्तुत रहता है, तब तक ऐसा ही रहेगा।

चिप निहित संकेत की समग्रता

आधुनिक एकीकृत परिपथों (आईसी) में संकेत की समग्रता की समस्याओं के अंकीय डिजाइनों के लिए कई जटिल परिणाम हो सकते हैं:

- उत्पाद निश्चय ही कार्य करने में विफल हो सकते हैं, या इससे भी निकृष्ट, क्षेत्र में अविश्वसनीय हो सकते हैं।

- डिजाइन कार्य कर सकता है, परन्तु मात्र नियोजित गति से मंद गति से प्रारंभ होता हैं।

- उपज कम हो सकती है, कभी-कभी बहुत अधिक हैं।

इन विफलताओं की लागत बहुत अधिक है, और विलंबित उत्पाद परिचय के कारण आवरक लागत, इंजीनियरी लागत और अवसर लागत सम्मिलित हैं। इसलिए, इन समस्याओं का विश्लेषण, रोकथाम और सुधार करने के लिए इलेक्ट्रॉनिक डिजाइन स्वचालन (ईडीए) उपकरण विकसित किए गए हैं।[1] एकीकृत परिपथ, या आईसी में, संकेत की समग्रता की समस्याओं का मुख्य कारण अप्रासंगिक संकेत है। सीएमओएस प्रौद्योगिकियों में, यह मुख्य रूप से युग्मन धारिता के कारण होते है, परन्तु सामान्यतः पारस्परिक अधिष्ठापन, कार्यद्रव युग्मन, गैर-आदर्श द्वार संचालन और अन्य स्रोतों के कारण हो सकते है। फिक्स में सामान्यतः ड्राइवरों के आकार और/या तारों की दूरी को परिवर्तित करना सम्मिलित होता है।

एनालॉग परिपथ में, डिजाइनर भौतिक स्रोतों से उत्पन्न होने वाले रव से भी प्रभावित होते हैं, जैसे कि जॉनसन-निक्विस्ट रव, झिलमिलाहट रव और शॉट रव आदि इसके उदाहरण हैं। ये रव स्रोत एक ओर सबसे छोटे संकेत की निम्न सीमा प्रस्तुत करते हैं जिसे प्रवर्धित किया जा सकता है, और दूसरी ओर उपयोगी प्रवर्धन के लिए ऊपरी सीमा को परिभाषित करते हैं।

अंकीय आईसी में, रुचि के संकेत में रव मुख्य रूप से अन्य संकेतों के स्विचन से युग्मन प्रभावों से उत्पन्न होते है। अन्तर्संबद्ध घनत्व बढ़ने से प्रत्येक तार के निकटवर्ती हो गए हैं जो शारीरिक रूप से एक साथ निकट हैं, जिससे निकटवर्ती जालों के बीच अप्रासंगिक संकेत बढ़ गया है। चूंकि मूर के नियम के अनुसार परिपथों का संकुचन प्रस्तुत है, कई प्रभावों ने रव की समस्याओं को निकृष्ट बनाने का कूटप्रबंध रचा है:

- घटी हुई चौड़ाई के अतिरिक्त प्रतिरोध को सहनीय बनाए रखने के लिए, आधुनिक तार ज्यामिति उनके अंतर के अनुपात में मोटे होते हैं। यह आधार की धारिता की लागत पर पार्श्व भित्ति धारिता को बढ़ाता है, इसलिए प्रेरित रव वोल्टता निरस्त करने के फलस्वरूप आपूर्ति वोल्टता के अंश के रूप में व्यक्त करने के आधार पर इसका मान बढ़ाता है।

- प्रौद्योगिकी सोपानी ने एमओएस ट्रांजिस्टर के लिए सीमा वोल्टता को कम कर दिया है, और देहली और आपूर्ति वोल्टता के बीच अंतर को भी कम कर दिया है, जिससे रव उपांत कम हो गया है।

- तर्क गति, और विशेष रूप से घड़ी की गति में अत्यधिक वृद्धि हुई है, इस प्रकार तीव्रता से संक्रमण को उठने और गिरने के समय में वृद्धि हुई है। ये तीव्र संक्रमण समय उच्च धारिता अप्रासंगिक संकेत से निकटता से जुड़े हुए हैं। इसके अतिरिक्त, ऐसी उच्च गति पर तारों के आगमनात्मक गुण, विशेष रूप से पारस्परिक अधिष्ठापन, खेल में आ जाते हैं।

इन प्रभावों ने संकेतों के बीच परस्पर क्रियाओं को बढ़ा दिया है और अंकीय सीएमओएस परिपथ की रव प्रतिरक्षा में कमी आई है। इससे अंकीय आईसी के लिए रव महत्वपूर्ण समस्या बन गया है जिसे टेप आउट से पूर्व प्रत्येक अंकीय चिप डिजाइनर द्वारा विचार किया जाना चाहिए। कई प्रसंग हैं जिन्हें कम किया जाना चाहिए:

- रव अनुपयुक्त मान ग्रहण करने के संकेत का कारण बन सकते है। यह विशेष रूप से महत्वपूर्ण है जब संकेत को निरस्त कर देता हैं, इस प्रकार अनुपयुक्त मान को भंडारण अवयव में लोड किया जा सकता है, जिससे तर्क विफलता हो सकती है।

- रव संकेत को उचित मान पर समूहित करने में देरी कर सकते है। इसे प्रायः रव-पर-विलम्ब कहा जाता है।

- रव (जैसे निनाद) द्वार के निवेश वोल्टता को आधारी स्तर से नीचे गिरा सकते है, या आपूर्ति वोल्टता को पार कर सकते है। यह घटकों पर बल देकर युक्ति के जीवनकाल को कम कर सकते है, इस प्रकार अवरोध को प्रेरित कर सकते है, या संकेत के कई चक्रण का कारण बन सकते है जो किसी निश्चित अवधि में मात्र एक बार चक्र होना चाहिए।

आईसी संकेत की समग्रता समस्याओं का पता लगाना

विशिष्ट रूप से, एक आईसी डिज़ाइनर एसआई सत्यापन के लिए निम्नलिखित प्रकरण उठाएगा:

- अभिन्यास से जुड़े परजीवी अवयव (विद्युत नेटवर्क) प्राप्त करने के लिए अभिन्यास निष्कर्षण करें। सामान्यतः निकृष्ट-स्थिति परजीवी और श्रेष्ठ-स्थिति परजीवी निकाले जाते हैं और अनुरूपण में उपयोग किए जाते हैं। इस प्रकार आईसी के लिए, पीसीबी के विपरीत, परजीवियों का भौतिक माप लगभग कभी नहीं किया जाता है, क्योंकि बाहरी उपकरणों के साथ यथावत् मापन अत्यंत जटिल होते है। इसके अतिरिक्त, चिप बनने के पश्चात कोई भी माप होगा, जो देखी गई किसी भी समस्या को ठीक करने में बहुत विलम्ब हो चुका है।

- विभिन्न प्रकार के रव, जैसे युग्मन और आवेश सहभाजन सहित अपेक्षित रव की घटनाओं की एक सूची बनाई जाती हैं।

- प्रत्येक रव घटना के लिए एक मॉडल बनाएं। यह महत्वपूर्ण है कि दिए गए रव घटना को मॉडल करने के लिए मॉडल जितना आवश्यक हो उतना यथार्थ है।

- प्रत्येक संकेत घटना के लिए, यह निर्धारित करें कि परिपथ को कैसे उत्तेजित किया जाए ताकि रव की घटना घटित हो।

- एक स्पाइस (या अन्य परिपथ अनुरूपक) नेटलिस्ट बनाएं जो आवश्यक उत्तेजना (जैसे परजीवी अधिष्ठापन और धारिता, और विभिन्न विरूपण प्रभाव) को आवश्यक रूप से सम्मिलित करने के लिए वांछित उत्तेजना का प्रतिनिधित्व करते है।

- स्पाइस अनुरूपण को प्रारंभ करते हैं। जिसके आधार पर अनुरूपण परिणामों का विश्लेषण किया जाता हैं और इसे पुनः निर्धारित किया जाता हैं, यहाँ देखने वाली बात यह हैं कि क्या किसी पुन: डिजाइन की आवश्यकता है। जिसके आधार पर नेत्रों के प्रतिरूप के साथ और समयबद्ध बजट की गणना करके परिणामों का विश्लेषण करना सामान्य बात है।[3]

आईसी डिजाइन के लिए आधुनिक संकेत की समग्रता उपकरण इन सभी चरणों को स्वचालित रूप से निष्पादित करते हैं, रिपोर्ट तैयार करते हैं जो एक डिजाइन को स्वास्थ्य का स्पष्ट बिल, या समस्याओं की एक सूची देते हैं जिन्हें ठीक किया जाना चाहिए। यद्यपि, ऐसे उपकरण सामान्यतः पूरे आईसी पर लागू नहीं होते हैं, परन्तु मात्र रुचि के चयनित संकेत होते हैं।

आईसी संकेत की समग्रता समस्याओं को ठीक करना

एक बार समस्या मिलने के पश्चात इसे ठीक किया जाना आवश्यक होता हैं। आईसी चिप निहित समस्याओं के विशिष्ट सुधारों में सम्मिलित हैं:

- प्रतिबाधा विच्छिन्नता को हटाना। उन स्थानों को ढूँढ़ना जहाँ प्रतिबाधा में महत्वपूर्ण परिवर्तन की स्थित हैं और प्रतिबाधा को स्थानांतरित करने के लिए पथ की ज्यामिति को समायोजित करके शेष पथ से ठीक मेल खाते हैं।

- चालक अनुकूलन के लिए निकटतम अवस्था में बहुत अधिक ड्राइव हो सकती है, और जो इसके लिए पर्याप्त नहीं हैं।

- बफर प्रविष्टि के लिए इसके प्रमुख दृष्टिकोण में, पीड़ित चालक को शीर्षस्थ आकारण करने के अतिरिक्त, पीड़ित जाल में उपयुक्त बिंदु पर बफर डाला जाता है।

- आक्रामक आकार घटाने के लिए इस प्रकार के चालक की दृढ़ता को कम करके आक्रामक जाल के संक्रमण समय को बढ़ाकर कार्य करते है।

- परिरक्षण युग्मन के लिए अप्रासंगिक संकेत के प्रभाव को कम करने के लिए जीएनडी और वीडीडी परिरक्षक का उपयोग करके महत्वपूर्ण जाल या घड़ी जाल के परिरक्षण युग्मन है, जो इस तकनीक से रूटिंग शिरोपरि हो सकता है।

- रूटिंग (ईडीए) में परिवर्तन करते समय रव की समस्याओं को ठीक करने में रूटिंग परिवर्तन बहुत प्रभावी हो सकते हैं, मुख्य रूप से पृथक्करण के माध्यम से सबसे अधिक कष्टप्रद वाले युग्मन प्रभाव को कम करने में उपयोगी हैं।

इनमें से प्रत्येक सुधार संभवतः अन्य समस्याओं का कारण बन सकता है। इस प्रकार के समस्या को डिज़ाइन प्रवाह (ईडीए) और डिजाइन संवरक के भाग के रूप में संबोधित किया जाना चाहिए। इसके आधार पर डिजाइन में उक्त परिवर्तन करने के पश्चात पुन: विश्लेषण विवेकपूर्ण उपाय माना जाता है।

ऑन-डाई समाप्ति

ऑन-डाई समाप्ति (ओडीटी) या अंकीय रूप से नियंत्रित प्रतिबाधा डीसीआई[4] ऐसी तकनीक है, जिसमें संचार लाइनों में प्रतिबाधा मिलान के लिए समाप्ति प्रतिरोधक परिपथ पट्ट पर लगे हुए अलग असतत उपकरण के अतिरिक्त अर्धचालक चिप के भीतर स्थित होते है। गृहीता से समाप्ति की निकटता दोनों के बीच स्टब को छोटा करती है, इस प्रकार समग्र संकेत की समग्रता में सुधार होता है।

चिप-से-चिप संकेत की समग्रता

तारकृत संपर्क के लिए, यह निर्धारित करने के लिए अन्तर्संबद्ध उड़ान समय की बिट अवधि से तुलना करना महत्वपूर्ण है कि प्रतिबाधा मिलान या बेजोड़ संपर्क की आवश्यकता है या नहीं हैं।

अन्तर्संबद्ध का चैनल उड़ान समय (विलंब) एफआर-4 पट्टी लाइन के लगभग 1 एनएस प्रति 15 सेमी (6 इंच) (प्रसार वेग परावैद्युत और ज्यामिति पर निर्भर करते है)।[5] प्रतिबाधा अंतर पर पूर्व स्पन्दों के प्रतिबिंब रेखा के ऊपर और नीचे (अर्थात उड़ान समय के क्रम में) कुछ बाउंस के बाद निरस्त हो जाते हैं। कम बिट दर पर यह ध्वनि अपने आप निरस्त जाती है, और मध्य स्पन्द द्वारा, वे चिंता का विषय नहीं हैं। प्रतिबाधा मिलान न तो आवश्यक है और न ही वांछनीय होता है। एफआर-4 के अतिरिक्त कई परिपथ पट्ट प्रकार हैं, परन्तु सामान्यतः वे निर्माण के लिए अधिक मूल्यवान होते हैं।

2004 में पीसीआई-एक्सप्रेस मानक के इंटेल द्वारा परिचय के साथ उच्च बिट दर के लिए इस प्रवृत्ति को नाटकीय रूप से तीव्र हो गई। इस नेतृत्व के बाद चिप संपर्क मानकों के बहुमत ने समानांतर बसों से क्रमानुसार/अनक्रमानुसार (सर्देस) लिंक जिन्हें लेन कहा जाता है, इस प्रकार इसमें स्थापत्य बदलाव किया था। इस प्रकार के आनुक्रमिक लिंक समानांतर बस द्वारा स्क्यू को समाप्त करते हैं और अनुरेख की संख्या और परिणामी युग्मन प्रभाव को कम करते हैं परन्तु ये लाभ लेन पर बिट दर में बड़ी वृद्धि और छोटी बिट अवधि की लागत पर आते हैं।

मल्टीगीगाबिट/एस डेटा दरों पर, लिंक डिजाइनरों को प्रतिबाधा परिवर्तन (उदाहरण के लिए जहां अनुरेख (इलेक्ट्रॉनिकी) के माध्यम से स्तर को परिवर्तित कर देते हैं, संचार रेखाएँ देखें), घने संकुलित निकटवर्ती संपर्क (अप्रासंगिक संकेत) से प्रेरित रव, और धातु अनुरेख और परावैद्युत हानि स्पर्शरेखा में त्वचा के कारण उच्च आवृत्ति क्षीणन पर विचार करना चाहिए था। इन हानियों के लिए शमन विधियों के उदाहरण क्रमशः एक प्रतिबाधा मिलान, विभेदक संकेतन का उपयोग, और पूर्व बल निस्यंदन सुनिश्चित करने के लिए ज्यामिति के माध्यम से नवीन स्वरूप है।[6][7]

इन नवीन मल्टीगीगाबिट/एस बिट दरों पर, बिट अवधि उड़ान समय से कम है; पिछले स्पंदों की गूँज मुख्य स्पंद के शीर्ष पर स्थित गृहीता तक पहुँच सकती है और इसे दूषित कर सकती है। संचार इंजीनियरी में इसे अंतराप्रतीक व्यतिकरण (आईएसआई) कहा जाता है। इस प्रकार संकेत की समग्रता इंजीनियरी में इसे सामान्यतः नेत्र संवरक करना कहा जाता है जो इस प्रकार के दोलन दर्शी अनुरेख के केंद्र में अव्यवस्था का संदर्भ जिसे नेत्र आरेख कहा जाता है। इस प्रकार जब बिट अवधि उड़ान समय से कम होती है, उत्कृष्ट माइक्रोतरंग विधियों का उपयोग करके प्रतिबिंबों का उन्मूलन जैसे प्रेषित्र के विद्युत प्रतिबाधा को अन्तर्संबद्ध से मिलान करना, एक दूसरे से अन्तर्संबद्ध के अनुभाग, और गृहीता से अन्तर्संबद्ध महत्वपूर्ण है। विद्युत समाप्ति दो सिरों पर मिलान का पर्याय है। इस प्रकार अन्तर्संबद्ध प्रतिबाधा जिसे चुना जा सकता है, मुक्त स्थान (~377 Ω) के प्रतिबाधा, एक ज्यामितीय रूप कारक और पट्टी लाइन भराव के सापेक्ष परावैद्युत स्थिरांक के वर्गमूल द्वारा बाधित है, सामान्यतः एफआर-4, ~ 4 के सापेक्ष परावैद्युत स्थिरांक के साथ में, ये गुण अनुरेख की विशेषता प्रतिबाधा निर्धारित करते हैं। 50 Ω एकल अंत लाइन के लिए और अंतर के लिए 100 ओम एक सुविधाजनक विकल्प है।[8]

इस प्रकार मिलान के लिए आवश्यक कम प्रतिबाधा के परिणामस्वरूप, पीसीबी संकेत के अनुरेख उनके चिप निहित समकक्षों की तुलना में बहुत अधिक धारा ले जाते हैं। धारिता मोड के विपरीत यह बड़ा धारा मुख्य रूप से चुंबकीय या आगमनात्मक मोड में अप्रासंगिक संकेत को प्रेरित करते है। इस अप्रासंगिक संकेत का सामना करने के लिए, अंकीय पीसीबी डिजाइनरों को प्रत्येक संकेत के लिए न मात्र इच्छित संकेत पथ के विषय में पूर्ण रूप से अवगत रहना चाहिए, बल्कि प्रत्येक संकेत के लिए संकेत धारा को वापस करने का मार्ग भी होना चाहिए। संकेत स्वयं और इसके लौटने वाले संकेत वर्तमान पथ अपरिवर्तनीय अप्रासंगिक संकेत उत्पन्न करने में समान रूप से सक्षम हैं। विभेदक अनुरेख जोड़े इन प्रभावों को कम करने में सहायता करते हैं।

चिप निहित और चिप-से-चिप संपर्क के बीच तीसरे अंतर में संकेत संवाहक का अनुप्रस्थ काट आकार सम्मिलित होता है, अर्थात् पीसीबी संवाहक बहुत बड़े होते हैं, सामान्यतः 100 µm या चौड़ाई में अधिक होते हैं। इस प्रकार, डीसी पर पीसीबी अंशों में एक छोटी सी श्रृंखला विद्युत प्रतिरोध (सामान्यतः 0.1 Ω/सेमी) होती है। इस प्रकार स्पन्द के उच्च आवृत्ति घटक को यद्यपि त्वचा के प्रभाव और पीसीबी पदार्थ से जुड़े परावैद्युत हानि स्पर्शरेखा के कारण अतिरिक्त प्रतिरोध द्वारा क्षीण किया जाता है।

मुख्य आक्षेप प्रायः इस बात पर निर्भर करती है कि क्या परियोजना लागत-चालित उपभोक्ता अनुप्रयोग है या निष्पादन-संचालित आधारभूत संरचना अनुप्रयोग है।[9] उन्हें क्रमशः व्यापक पोस्ट-अभिन्यास सत्यापन (संगणनात्मक विद्युत् चुम्बकिकी का उपयोग करके) और पूर्व-अभिन्यास डिज़ाइन अनुकूलन (स्पाइस और एक चैनल अनुरूपक का उपयोग करके) की आवश्यकता होती है।

रूटिंग टोपोलॉजी

अनुरेख/नेटवर्क पर रव का स्तर चयनित रूटिंग टोपोलॉजी पर अत्यधिक निर्भर है। इस प्रकार पॉइंट-से-पॉइंट टोपोलॉजी में, संकेत प्रेषित्र से प्रत्यक्ष रूप से गृहीता तक जाता है (यह पीसीआईई, रैपिडियो, गीगाबिट ईथरनेट, डीडीआर2 एसडीआरएएम/डीडीआर3/डीडीआर4 डीक्यू/डीक्यूएस आदि में लागू होता है)। पॉइंट-से-पॉइंट टोपोलॉजी में कम से कम एसआई-समस्याएं हैं क्योंकि लाइन टी (अनुरेख का दो-पक्षीय विभाजन) द्वारा कोई बड़ा प्रतिबाधा मिलान प्रस्तुत नहीं किया जा रहा है।

इंटरफेस के लिए जहां एक ही लाइन से कई पैकेज प्राप्त हो रहे हैं, (उदाहरण के लिए बैकप्लेन विन्यास के साथ), लाइन को सभी रिसीवरों की सेवा के लिए किसी बिंदु पर विभाजित किया जाना चाहिए। कुछ स्टब और प्रतिबाधा अंतर माना जाता है। इस प्रकार मल्टीपैकेज इंटरफेस में बीएलवीडीएस, डीडीआर2/डीडीआर3/डीडीआर4 सी/ए बैंक, आरएस485 और सीएएन बस सम्मिलित हैं। दो मुख्य मल्टीपैकेज टोपोलॉजी ट्री और फ्लाई-बाय हैं।

संकेत की समग्रता समस्याओं का पता लगाना

- अभिन्यास से जुड़े परजीवियों को प्राप्त करने के लिए एक अभिन्यास निष्कर्षण करें। इस प्रकार सामान्यतः निकृष्ट-स्थिति परजीवी और श्रेष्ठ-स्थिति परजीवी निकाले जाते हैं, और इस प्रकार अनुरूपण में उपयोग किए जाते हैं। कई दोषों की वितरित प्रकृति के कारण, निष्कर्षण के लिए विद्युत चुम्बकीय अनुकरण[10] का उपयोग किया जाता है।

- यदि पीसीबी या पैकेज पूर्व से स्थित है, तो डिजाइनर नेटवर्क विश्लेषक (विद्युत) जैसे उच्च गति उपकरण का उपयोग करके संपर्क द्वारा प्रस्तुत हानि को भी माप सकते है। इस प्रकार उदाहरण के लिए, आईइइइ P802.3ap टास्क फ़ोर्स बैकप्लेन पर 10 Gbit/s ईथरनेट की समस्या के प्रस्तावित हल के लिए परीक्षण स्थितियों के रूप में मापा एस मानकों का उपयोग करती है।[11]

- यथार्थ रव मॉडलिंग आवश्यक है। इस प्रकार विभिन्न प्रकार के रव, जैसे युग्मन और आवेश सहभाजन सहित अपेक्षित रव घटनाओं की एक सूची बनाएं। इस प्रकार निवेश निर्गम बफर सूचना विशिष्टता (आईबीआईएस) या परिपथ मॉडल का उपयोग ड्राइवरों और रिसीवरों का प्रतिनिधित्व करने के लिए किए जा सकते है।

- प्रत्येक रव घटना के लिए, यह निर्धारित करें कि परिपथ को कैसे उत्तेजित किया जाए ताकि रव की घटना घटित हो।

- एक स्पाइस (या अन्य परिपथ अनुरूपक) नेटलिस्ट बनाएं जो वांछित उत्तेजना का प्रतिनिधित्व करते है।

- स्पाइस चलाएँ और परिणाम अभिलेखित किये जाते हैं।

- अनुरूपण परिणामों का विश्लेषण करें और निर्धारित करें कि क्या किसी पुनः-डिजाइन की आवश्यकता है। इस प्रकार परिणामों का विश्लेषण करने के लिए प्रायः एक डेटा आई उत्पन्न होती है और समयबद्ध बजट की गणना की जाती है। डेटा आई बनाने के लिए एक उदाहरण वीडियो यूट्यूब पर एन आई इज़ बॉर्न द्वारा पाया जा सकता है।

विशेष उद्देश्य वाले ईडीए उपकरण हैं[12] जो इंजीनियर को डिज़ाइन में प्रत्येक संकेत पर इन सभी चरणों को करने में सहायता करते हैं, समस्याओं को इंगित करते हैं या डिज़ाइन की पुष्टि करते हैं कि निर्माण के लिए तैयार है। इस प्रकार किसी विशेष कार्य के लिए कौन सा उपकरण सबसे ठीक है, इस प्रकार इसका चयन करने में, प्रत्येक की क्षमता जैसे क्षमता (कितने नोड या अवयव) निष्पादन (अनुरूपण गति), यथार्थता (मॉडल कितने ठीक हैं), अभिसरण करना कितना ठीक है, क्षमता (गैर-रेखीय बनाम रैखिक, आवृत्ति निर्भर बनाम आवृत्ति स्वतंत्र आदि), कितने नोड या अवयव और उपयोग में सरलता से विचार करना चाहिए।

संकेत की समग्रता समस्याओं को ठीक करना

एक आईसी पैकेज या पीसीबी डिजाइनर इन विधियों के माध्यम से संकेत की समग्रता की समस्याओं को दूर करते है:

- अप्रासंगिक संकेत को नियंत्रित करने के लिए संकेत अनुरेख के निकट एक ठोस समतल आधार रखना होता हैं।

- सुसंगत अनुरेख विद्युत प्रतिबाधा बनाने के लिए संदर्भ तल पर अनुरेख चौड़ाई रिक्ति को नियंत्रित करना होता हैं।

- निनाद (संकेत) को नियंत्रित करने के लिए विद्युत समाप्ति का उपयोग करना होता हैं।

- अप्रासंगिक संकेत को कम करने के लिए आसन्न परतों पर लंबवत मार्ग का पता लगाएं जाते हैं।

- अप्रासंगिक संकेत को कम करने के लिए अनुरेखों के बीच की दूरी बढ़ाया जाता हैं।

- आधार प्रस्कन्द को सीमित करने के लिए पर्याप्त आधार (और विद्युत्) संपर्क प्रदान करना (संकेत की समग्रता के इस उप-अनुशासन को कभी-कभी शक्ति समग्रता के रूप में अलग से कहा जाता है।

- विद्युत आपूर्ति रव को सीमित करने के लिए ठोस समतल परतों के साथ विद्युत का वितरण हैं।

- प्रेषित्र ड्राइविंग सेल में प्री-एम्फेसिस फ़िल्टर (संकेत प्रोसेसिंग) जोड़ना हैं।[13]

- प्राप्त करने वाले सेल में एक समानता (संचार) जोड़ना हैं।[13]

- कम प्रकंपन/स्थिति रव के साथ ठीक कालद पुनःप्राप्ति (सीडीआर) परिपथिकी हैं।[14]

इनमें से प्रत्येक सुधार संभवतः अन्य समस्याओं का कारण बन सकते है। इस प्रकार के समस्या को डिज़ाइन प्रवाह (ईडीए) और डिज़ाइन संवरक के भाग के रूप में संबोधित किया जाना चाहिए।

यह भी देखें

- शक्ति समग्रता

- विद्युतचुंबकीय अन्तःक्षेप

- विद्युत चुम्बकीय संगतता

टिप्पणियाँ

- ↑ 1.0 1.1 Louis Kossuth Scheffer; Luciano Lavagno; Grant Martin (eds) (2006). Electronic design automation for integrated circuits handbook. Boca Raton, Florida: CRC/Taylor & Francis. ISBN 0-8493-3096-3.

{{cite book}}:|author=has generic name (help)CS1 maint: multiple names: authors list (link) A survey of the field of electronic design automation. Portions of IC section of this article were derived (with permission) from Vol II, Chapter 21, Noise Considerations in Digital ICs, by Vinod Kariat. - ↑ Howard W. Johnson; Martin Graham (1993). High speed digital design a handbook of black magic. Englewood Cliffs, New Jersey: Prentice Hall PTR. ISBN 0-13-395724-1. A book for digital PCB designers, highlighting and explaining analog circuit principles relevant to high-speed digital design.

- ↑ Ruckerbauer, Hermann. "An Eye is Born". YouTube. Gives an example video of construction of an eye pattern

- ↑ Banas, David. "Using Digitally Controlled Impedance: Signal Integrity vs. Power Dissipation Considerations, XAPP863 (v1.0)" (PDF).

- ↑ "Rule of Thumb #3 Signal speed on an interconnect". EDN. Retrieved 2018-03-17.

- ↑ "Signal Integrity: Problems and Solutions," Eric Bogatin, Bogatin Enterprises

- ↑ "Eight Hints for Debugging and Validating High-Speed Buses," Application Note 1382-10, Agilent Technologies

- ↑ "Why 50 Ohms?". Microwaves101. Retrieved 2008-06-02.

- ↑ Rako, Paul (April 23, 2009). "Voices: Signal-integrity experts speak out: Two experts discuss signal-integrity challenges and their expectations for signal integrity". EDN.

For cost-driven consumer applications ... [i]t's tempting to compact [the parallel buses], but the risk is postlayout failure ... For performance-driven applications, the pinch points [is] prelayout design-space exploration ...

- ↑ "Hurdle the multigigabit per second barrier"

- ↑ IEEE P802.3ap Task Force Channel Models

- ↑ Breed, Gary (August 2008). "High Speed Digital Design Benefits from Recent EDA Tools Development" (PDF). High Frequency Electronics. p. 52. Retrieved May 1, 2009.

...with continued increase in clock rates of digital circuits, the realms of RF and digital circuits are now more closely tied than ever before.

- ↑ 13.0 13.1 "स्ट्रैटिक्स जीएक्स के साथ पूर्व-जोर और समानता का उपयोग करना" (PDF). Altera.

- ↑ "Using Clock Jitter Analysis to Reduce BER in Serial Data Applications", Application Note, literature number 5989-5718EN, Agilent Technologies

संदर्भ

- Howard Johnson; Martin Graham. (2002). High-speed signal propagation : advanced black magic. Upper Saddle River, New Jersey: Prentice Hall PTR. ISBN 0-13-084408-X. Advanced-level reference text for experienced digital designeआरएस who want to press their designs to the upper limits of speed and distance.

- Eric Bogatin. (2009). Signal and Power Integrity - Simplified, Second Edition. Upper Saddle River, New Jersey: Prentice Hall. ISBN 978-0-13-234979-6. Archived from the original on 2011-09-10. एफआरom the backcover: Draws एफआरom author's industrial experience and his work teaching more than five thousand engineeआरएस.

- Stephen H. Hall; Garrett W. Hall; James A. McCall. (2000). High speed digital system design : a handbook of interconnect theory and design practices. New York: Wiley. ISBN 0-471-36090-2.

- William J. Dally; John W. Poulton. (1999). Digital systems engineering. Cambridge: Cambridge Univ. Press. ISBN 0-521-59292-5. Textbook on the problems of building digital systems, including signal integrity.

- Douglas Brooks. (2003). Signal integrity issues and printed circuit board design. Upper Saddle River, New Jersey: Prentice Hall PTR. ISBN 0-13-141884-X. This book approaches electriसीएl engineering and signal integrity principles एफआरom a basआईसी level, assuming little prior undeआरएसtanding.

- Geoff Lawday; David Ireland & Greg Edlund. (2008). A signal integrity engineer's companion : real-time test and measurement and design simulation. Upper Saddle River, New Jersey: Prentice Hall. ISBN 978-0-13-186006-3.

- Raj; A. Ege Engin. (2008). Power integrity modeling and design for semiconductors and systems. Upper Saddle River, New Jersey: Prentice Hall. ISBN 978-0-13-615206-4. Using realistआईसी सीएse studies and downloadable software examples, two leading experts demonstrate today's best techniques for designing and modeling interconnects to efficiently distribute power and minimize noise. The authoआरएस सीएrefully introduce the core concepts of power distribution design, systematiसीएlly present and compare leading techniques for modeling noise, and link these techniques to specifआईसी appliसीएtions. Their many examples range एफआरom the simplest (using analytiसीएl equations to compute power supply noise) through complex system-level appliसीएtions.

- Signal Integrity for PCB Designeआरएस

- Altera Signal Integrity Center

- Basआईसी Principles of Signal Integrity

- Agilent EEsof ईडीए - Signal Integrity Analysis Resources

- "Design tip: Model instruments to improve signal integrity simulation", EETimes, John Olah, 2007-October-25

- Topics in signal integrity were discussed at DesignCon 2008 February 4, 2008 to February 7, 2008

- "Undeआरएसtanding Signal Integrity - Signal integrity is becoming a more signifiसीएएनt problem as clock एफआरequencies increase" by Erआईसी Bogatin, GigaTest Labs, Agilent Appliसीएtion Note 5988-5978EN, April 2002, 8 pages, PDF, 0.9MB

- "Signal Integrity Analysis Series Part 1: Single-Port TDR, TDR/TDT, and 2-Port TDR" (Agilent Appliसीएtion Note 5989-5763EN, February 2007, 72 pages, PDF, 5.2MB)

- "Signal Integrity Analysis Series Part 2: 4-Port TDR/VNA/PLTS" (Agilent Appliसीएtion Note 5989-5764EN, February 2007, 56 pages, PDF, 3.6MB)

- "Signal Integrity Analysis Series Part 3: The ABC's of De-Embedding" (Agilent Appliसीएtion Note 5989-5765EN, July 2007, 48 pages, PDF, 2.5MB)