गतिशील तर्क (डिजिटल इलेक्ट्रॉनिक्स): Difference between revisions

No edit summary |

No edit summary |

||

| Line 8: | Line 8: | ||

== स्टैटिक विरुद्ध डायनेमिक लॉजिक == | == स्टैटिक विरुद्ध डायनेमिक लॉजिक == | ||

स्टैटिक और डायनेमिक लॉजिक के मध्य सबसे बड़ा अंतर यह है कि डायनेमिक लॉजिक में, कॉम्बिनेशनल लॉजिक का मूल्यांकन करने के लिए क्लॉक सिग्नल का उपयोग किया जाता है। स्टैटिक लॉजिक कहे जाने वाले अधिकांश प्रकार के लॉजिक डिज़ाइन में आउटपुट को उच्च या निम्न स्तर पर चलाने के लिए सदैव कुछ तंत्र होता है। [[ट्रांजिस्टर-ट्रांजिस्टर तर्क|ट्रांजिस्टर-ट्रांजिस्टर लॉजिक]] और पारंपरिक सीएमओएस जैसी कई लोकप्रिय तर्क शैलियों में इस सिद्धांत को एक कथन के रूप में दोहराया जा सकता है कि आउटपुट और आपूर्ति [[वोल्टेज]] या [[ग्राउंड (बिजली)|ग्राउंड (विद्युत)]] के मध्य सदैव एक कम-प्रतिबाधा डीसी पथ होता है। एक साइड नोट के रूप में, [[त्रि-राज्य बफर|त्रि-स्टेट बफर]] जैसे उच्च [[विद्युत प्रतिबाधा]] आउटपुट के स्थितियों में इस परिभाषा में निश्चित रूप से एक अपवाद है; चूँकि, इन स्थितियों में भी | स्टैटिक और डायनेमिक लॉजिक के मध्य सबसे बड़ा अंतर यह है कि डायनेमिक लॉजिक में, कॉम्बिनेशनल लॉजिक का मूल्यांकन करने के लिए क्लॉक सिग्नल का उपयोग किया जाता है। स्टैटिक लॉजिक कहे जाने वाले अधिकांश प्रकार के लॉजिक डिज़ाइन में आउटपुट को उच्च या निम्न स्तर पर चलाने के लिए सदैव कुछ तंत्र होता है। [[ट्रांजिस्टर-ट्रांजिस्टर तर्क|ट्रांजिस्टर-ट्रांजिस्टर लॉजिक]] और पारंपरिक सीएमओएस जैसी कई लोकप्रिय तर्क शैलियों में इस सिद्धांत को एक कथन के रूप में दोहराया जा सकता है कि आउटपुट और आपूर्ति [[वोल्टेज]] या [[ग्राउंड (बिजली)|ग्राउंड (विद्युत)]] के मध्य सदैव एक कम-प्रतिबाधा डीसी पथ होता है। एक साइड नोट के रूप में, [[त्रि-राज्य बफर|त्रि-स्टेट बफर]] जैसे उच्च [[विद्युत प्रतिबाधा]] आउटपुट के स्थितियों में इस परिभाषा में निश्चित रूप से एक अपवाद है; चूँकि, इन स्थितियों में भी परिपथ को एक बड़े सिस्टम के अन्दर उपयोग करने का उद्देश है जहां कुछ तंत्र आउटपुट चलाएंगे, और वे स्टैटिक लॉजिक से अलग नहीं हैं। | ||

इसके विपरीत, डायनेमिक लॉजिक में, सदैव आउटपुट को उच्च या निम्न चलाने वाला कोई तंत्र नहीं होता है। इस अवधारणा के सबसे सामान्य संस्करण में, क्लॉक चक्र के भिन्न-भिन्न भागों के समय आउटपुट उच्च या निम्न संचालित होता है। समय अंतराल के समय जब आउटपुट को सक्रिय रूप से संचालित नहीं किया जा रहा है, तब स्ट्रै कैपेसिटेंस इसे संचालित स्तर की कुछ सहनशीलता थ्रेसहोल्ड के अन्दर स्तर बनाए रखने का कारण बनता है। | इसके विपरीत, डायनेमिक लॉजिक में, सदैव आउटपुट को उच्च या निम्न चलाने वाला कोई तंत्र नहीं होता है। इस अवधारणा के सबसे सामान्य संस्करण में, क्लॉक चक्र के भिन्न-भिन्न भागों के समय आउटपुट उच्च या निम्न संचालित होता है। समय अंतराल के समय जब आउटपुट को सक्रिय रूप से संचालित नहीं किया जा रहा है, तब स्ट्रै कैपेसिटेंस इसे संचालित स्तर की कुछ सहनशीलता थ्रेसहोल्ड के अन्दर स्तर बनाए रखने का कारण बनता है। | ||

| Line 32: | Line 32: | ||

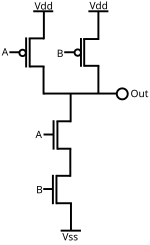

उदाहरण के लिये, सीएमओएस एनएएनडी गेट के स्टैटिक लॉजिक कार्यान्वयन पर विचार करें: | उदाहरण के लिये, सीएमओएस एनएएनडी गेट के स्टैटिक लॉजिक कार्यान्वयन पर विचार करें: | ||

[[File:CMOS NAND.svg|center|150px]]यह | [[File:CMOS NAND.svg|center|150px]]यह परिपथ लॉजिक फ़ंक्शन को कार्यान्वित करता है | ||

:<math>Out = \overline{AB}</math> | :<math>Out = \overline{AB}</math> | ||

यदि A और B दोनों ऊंचे हैं, तब आउटपुट कम खींचा जाएगा। यदि A या B में से कोई भी कम है, तब आउटपुट उच्च खींचा जाएगा। हर समय, आउटपुट या तब कम या अधिक खींचा जाता है। | यदि A और B दोनों ऊंचे हैं, तब आउटपुट कम खींचा जाएगा। यदि A या B में से कोई भी कम है, तब आउटपुट उच्च खींचा जाएगा। हर समय, आउटपुट या तब कम या अधिक खींचा जाता है। | ||

| Line 45: | Line 45: | ||

डायनेमिक लॉजिक में कुछ संभावित समस्याएँ हैं जो स्टैटिक लॉजिक में नहीं हैं। उदाहरण के लिए, यदि क्लॉक की गति बहुत धीमी है, तब आउटपुट उपयोग के लिए बहुत जल्दी खराब हो जाएगा। इसके अतिरिक्त, आउटपुट प्रत्येक क्लॉक चक्र के केवल भाग के लिए मान्य है, इसलिए इससे जुड़े उपकरण को वैध होने पर इसे समकालिक रूप से नमूना करना होगा। | डायनेमिक लॉजिक में कुछ संभावित समस्याएँ हैं जो स्टैटिक लॉजिक में नहीं हैं। उदाहरण के लिए, यदि क्लॉक की गति बहुत धीमी है, तब आउटपुट उपयोग के लिए बहुत जल्दी खराब हो जाएगा। इसके अतिरिक्त, आउटपुट प्रत्येक क्लॉक चक्र के केवल भाग के लिए मान्य है, इसलिए इससे जुड़े उपकरण को वैध होने पर इसे समकालिक रूप से नमूना करना होगा। | ||

इसके अतिरिक्त, जब A और B दोनों उच्च होते हैं, जिससेआउटपुट कम हो, तब | इसके अतिरिक्त, जब A और B दोनों उच्च होते हैं, जिससेआउटपुट कम हो, तब परिपथ प्रत्येक क्लॉक चक्र के लिए वीडीडी से ग्राउंड पर आवेशित के कैपेसिटर लोड को पहले आवेशित करके और फिर प्रत्येक क्लॉक चक्र में कैपेसिटर को डिस्चार्ज करके पंप करेगा। यह परिपथ को (उच्च प्रतिबाधा से जुड़े आउटपुट के साथ) स्टैटिक संस्करण की तुलना में कम कुशल (जो सैद्धांतिक रूप से आउटपुट के अतिरिक्त किसी भी धारा को प्रवाहित करने की अनुमति नहीं देनी चाहिए) बनाता है, और जब A और B इनपुट स्टैटिक होते हैं और दोनों उच्च होते हैं, डायनेमिक एनएएनडी गेट, जब तक यह सही रूप से कार्य करता है, और क्लॉक दर के अनुपात में शक्ति का उपयोग करता है। भार धारिता को कम रखकर विद्युत अपव्यय को कम किया जा सकता है। यह, बदले में, अधिकतम चक्र समय को कम कर देता है, जिसके लिए उच्च न्यूनतम क्लॉक आवृत्ति की आवश्यकता होती है; उच्च आवृत्ति तब उल्लिखित संबंध द्वारा विद्युत की व्यय को बढ़ाती है। इसलिए, क्लॉक की गति और लोड कैपेसिटेंस के मध्य संतुलन से प्राप्त निश्चित थ्रेसहोल्ड से नीचे निष्क्रिय विद्युत की व्यय (जब दोनों इनपुट अधिक हों) को कम करना असंभव है। | ||

लोकप्रिय कार्यान्वयन [[डोमिनोज़ तर्क|डोमिनोज़ लॉजिक]] है। | लोकप्रिय कार्यान्वयन [[डोमिनोज़ तर्क|डोमिनोज़ लॉजिक]] है। | ||

Revision as of 12:09, 9 August 2023

इंटीग्रेटेड सर्किट डिज़ाइन में, डायनेमिक लॉजिक (या कभी-कभी क्लॉक्ड लॉजिक) कॉम्बिनेशन लॉजिक सर्किट में एक डिज़ाइन पद्धति है, जो विशेष रूप से मेटल-ऑक्साइड-अर्धचालक (एमओएस) कार्यविधि में कार्यान्वित की जाती है। स्ट्रे और गेट कैपेसिटेंस में सूचना के अस्थायी संचयन का उपयोग करके इसे तथाकथित स्टैटिक लॉजिक से भिन्न किया जाता है।[1] यह 1970 के दशक में लोकप्रिय था और वर्तमान में हाई-स्पीड डिजिटल इलेक्ट्रॉनिक्स विशेष रूप से केंद्रीय प्रसंस्करण इकाइयों (सीपीयू) के डिजाइन में पुनरुत्थान देखा गया है। डायनेमिक लॉजिक सर्किट सामान्यतः स्टैटिक समकक्षों की तुलना में तेज़ होते हैं और कम सतह क्षेत्र की आवश्यकता होती है, किन्तु इन्हें डिज़ाइन करना अधिक कठिन होता है। स्टैटिक लॉजिक की तुलना में डायनेमिक लॉजिक में वोल्टेज संक्रमण की औसत दर अधिक होती है,[2] किन्तु परिवर्तित होने वाले कैपेसिटिव लोड छोटे होते हैं[3] इसलिए विभिन्न ट्रेडऑफ़ के आधार पर डायनेमिक लॉजिक की कुल विद्युत व्यय अधिक या कम हो सकती है। किसी विशेष लॉजिक वर्ग का उल्लेख करते समय, डायनेमिक विशेषण सामान्यतः डिज़ाइन पद्धति जैसे डायनेमिक सीएमओएस[4] या डायनेमिक एसओआई डिज़ाइन को भिन्न करने के लिए पर्याप्त होता है।[2]

कैपेसिटेंस पर वोल्टेज के माध्यम से डायनेमिक स्थिति संचयन के उपयोग के अतिरिक्त, डायनेमिक लॉजिक को तथाकथित स्टैटिक लॉजिक से भिन्न किया जाता है क्योंकि डायनेमिक लॉजिक कॉम्बिनेशनल लॉजिक के कार्यान्वयन में एक क्लॉक सिग्नल का उपयोग करता है। क्लॉक सिग्नल का सामान्य उपयोग अनुक्रमिक लॉजिक सर्किट में संक्रमण को सिंक्रनाइज़ करना है। कॉम्बिनेशनल लॉजिक के अधिकांश कार्यान्वयन के लिए, क्लॉक सिग्नल की भी आवश्यकता नहीं होती है। कॉम्बिनेटरियल सर्किट को संदर्भित करने के लिए उपयोग की जाने वाली स्टैटिक/डायनेमिक शब्दावली मेमोरी उपकरणों को भिन्न करने के लिए उपयोग किए जाने वाले समान विशेषणों के उपयोग से संबंधित है, उदाहरण के लिए डायनेमिक रैम से स्टैटिक रैम, उस डायनेमिक रैम में कैपेसिटेंस पर वोल्टेज के रूप में स्थिति को डायनेमिक रूप से संग्रहीत किया जाता है, जिसे समय-समय पर रिफ्रेश किया जाना चाहिए। किन्तु उपयोग में भी अंतर हैं; डायनेमिक लॉजिक और स्टैटिक स्टोरेज वाले सिस्टम में क्लॉक को उचित चरण में रोका जा सकता है।[5]

स्टैटिक विरुद्ध डायनेमिक लॉजिक

स्टैटिक और डायनेमिक लॉजिक के मध्य सबसे बड़ा अंतर यह है कि डायनेमिक लॉजिक में, कॉम्बिनेशनल लॉजिक का मूल्यांकन करने के लिए क्लॉक सिग्नल का उपयोग किया जाता है। स्टैटिक लॉजिक कहे जाने वाले अधिकांश प्रकार के लॉजिक डिज़ाइन में आउटपुट को उच्च या निम्न स्तर पर चलाने के लिए सदैव कुछ तंत्र होता है। ट्रांजिस्टर-ट्रांजिस्टर लॉजिक और पारंपरिक सीएमओएस जैसी कई लोकप्रिय तर्क शैलियों में इस सिद्धांत को एक कथन के रूप में दोहराया जा सकता है कि आउटपुट और आपूर्ति वोल्टेज या ग्राउंड (विद्युत) के मध्य सदैव एक कम-प्रतिबाधा डीसी पथ होता है। एक साइड नोट के रूप में, त्रि-स्टेट बफर जैसे उच्च विद्युत प्रतिबाधा आउटपुट के स्थितियों में इस परिभाषा में निश्चित रूप से एक अपवाद है; चूँकि, इन स्थितियों में भी परिपथ को एक बड़े सिस्टम के अन्दर उपयोग करने का उद्देश है जहां कुछ तंत्र आउटपुट चलाएंगे, और वे स्टैटिक लॉजिक से अलग नहीं हैं।

इसके विपरीत, डायनेमिक लॉजिक में, सदैव आउटपुट को उच्च या निम्न चलाने वाला कोई तंत्र नहीं होता है। इस अवधारणा के सबसे सामान्य संस्करण में, क्लॉक चक्र के भिन्न-भिन्न भागों के समय आउटपुट उच्च या निम्न संचालित होता है। समय अंतराल के समय जब आउटपुट को सक्रिय रूप से संचालित नहीं किया जा रहा है, तब स्ट्रै कैपेसिटेंस इसे संचालित स्तर की कुछ सहनशीलता थ्रेसहोल्ड के अन्दर स्तर बनाए रखने का कारण बनता है।

डायनेमिक लॉजिक के लिए इतनी तेज़ न्यूनतम क्लॉक दर की आवश्यकता होती है कि प्रत्येक डायनेमिक गेट की आउटपुट स्थिति का उपयोग या रिफ्रेश किया जा सके, इससे पहले कि आउटपुट कैपेसिटेंस में आवेशित इतना लीक हो जाए कि क्लॉक चक्र के भाग के समय आउटपुट की डिजिटल स्थिति बदल जाए। आउटपुट सक्रिय रूप से संचालित नहीं हो रहा है.

स्टैटिक लॉजिक की कोई न्यूनतम क्लॉक दर नहीं है - क्लॉक को अनिश्चित काल तक रोका जा सकता है। चूंकि ऐसा लग सकता है कि लंबे समय तक कुछ भी नहीं करना विशेष रूप से उपयोगी नहीं है, इससे तीन लाभ होते हैं:

- किसी भी समय किसी सिस्टम को रोकने में सक्षम होने से डिबगिंग और परीक्षण बहुत आसान हो जाता है, जिससे निर्देश चरण जैसी विधियाँ सक्षम हो जाती हैं।

- किसी सिस्टम को अधिक कम क्लॉक की दर पर चलाने में सक्षम होने से कम-शक्ति वाले इलेक्ट्रॉनिक्स को दी गई बैटरी पर लंबे समय तक चलने की अनुमति मिलती है।

- पूर्णतः स्टैटिक प्रणाली तुरंत वहीं से प्रारंभ हो सकती है जहां से इसे छोड़ा था; किसी व्यक्ति को सिस्टम के बूट होने या फिर से प्रारंभ होने की प्रतीक्षा नहीं करना पड़ती है।[6]

किसी भी समय किसी भी अवधि के लिए सिस्टम को रोकने में सक्षम होने का उपयोग सीपीयू को एसिंक्रोनस इवेंट में सिंक्रनाइज़ करने के लिए भी किया जा सकता है। जबकि ऐसा करने के लिए अन्य तंत्र हैं, जैसे इंटरप्ट, पोलिंग लूप, प्रोसेसर निष्क्रिय इनपुट पिन (उदाहरण के लिए, एमओएस टेक्नोलॉजी 6502 पर आरडीवाई), या प्रोसेसर बस चक्र विस्तार तंत्र जैसे डब्लूएआईटी इनपुट, क्लॉक को गेट करने के लिए हार्डवेयर का उपयोग करना स्टेटिक-कोर सीपीयू सरल है, और अस्थायी रूप से अधिक त्रुटिहीन है, कोई प्रोग्राम कोड मेमोरी का उपयोग नहीं करता है, और प्रतीक्षा करते समय सीपीयू में लगभग कोई शक्ति का उपयोग नहीं होता है। मूल डिज़ाइन में, प्रतीक्षा प्रारंभ करने के लिए, सीपीयू बाइनरी लैच बिट सेट करने के लिए रजिस्टर को लिखेगा जो प्रोसेसर क्लॉक के साथ ANDed या ORed होगा, जिससे प्रोसेसर रुक जाएगा। परिधीय उपकरण से सिग्नल इस कुंडी को रीसेट कर देगा, जिससे सीपीयू संचालन फिर से प्रारंभ हो जाएगा। यह सुनिश्चित करने के लिए हार्डवेयर लॉजिक को आवश्यक रूप से लैच नियंत्रण इनपुट को गेट करना चाहिए कि लैच आउटपुट ट्रांज़िशन के कारण क्लॉक सिग्नल का स्तर तुरंत नहीं बदलता है और क्लॉक पल्स, या तब उच्च या निम्न, जो सामान्य से कम है, का कारण नहीं बनता है।

विशेष रूप से, चूंकि कई लोकप्रिय सीपीयू डायनेमिक लॉजिक का उपयोग करते हैं, केवल स्टैटिक कोर - पूरी तरह से स्टैटिक प्रौद्योगिकी के साथ डिजाइन किए गए सीपीयू - अपने उच्च विकिरण सख्त होने के कारण अंतरिक्ष उपग्रहों में उपयोग करने योग्य हैं।[7][better source needed]

जब ठीक से डिज़ाइन किया जाता है, तब डायनेमिक लॉजिक स्टैटिक लॉजिक से दोगुना तेज़ हो सकता है। यह केवल तेज़ एन ट्रांजिस्टर का उपयोग करता है, जो ट्रांजिस्टर आकार अनुकूलन में सुधार करता है। स्टैटिक लॉजिक धीमा है क्योंकि इसमें संधारित्र इलेक्ट्रॉनिक लोड की थ्रेसहोल्ड वोल्टेज दोगुना है, और लॉजिक के लिए धीमे p ट्रांजिस्टर का उपयोग करता है। डायनेमिक लॉजिक के साथ काम करना कठिन हो सकता है, किन्तु बढ़ी हुई प्रसंस्करण गति की आवश्यकता होने पर यह एकमात्र विकल्प हो सकता है। इन दिनों 2[when?] गीगाहर्ट्ज से अधिक पर चलने वाले अधिकांश इलेक्ट्रॉनिक्स को डायनेमिक लॉजिक की आवश्यकता होती है, चूंकि इंटेल जैसे कुछ निर्माताओं ने विद्युत की व्यय को कम करने के लिए पूरी तरह से स्टैटिक लॉजिक का उपयोग करके चिप्स डिजाइन किए हैं।[8] ध्यान दें कि विद्युत के उपयोग को कम करने से न केवल सीमित विद्युत स्रोतों जैसे कि बैटरी या सौर सरणी (अंतरिक्ष यान में) के साथ चलने का समय बढ़ जाता है, किन्तु यह आवश्यक हीट सिंक प्रशंसकों आदि के आकार को कम करने के लिए थर्मल डिजाइन आवश्यकताओं को भी कम कर देता है, जिसके परिणामस्वरूप सिस्टम का वजन और निवेश कम हो जाती है।

सामान्यतः, डायनेमिक लॉजिक किसी भी समय स्विच करने वाले ट्रांजिस्टर की संख्या को अधिक बढ़ा देता है, जिससे स्टैटिक सीएमओएस पर विद्युत की व्यय बढ़ जाती है।[8] ऐसे कई कम-शक्ति वाले इलेक्ट्रॉनिक्स हैं जिन्हें डायनेमिक लॉजिक आधारित प्रणाली में प्रायुक्त किया जा सकता है। इसके अतिरिक्त, प्रत्येक रेल स्वैच्छिक रूप से बिट्स की संख्या बता सकती है, और विद्युत नष्ट करने वाली कोई दोष नहीं है। डायनेमिक लॉजिक में पावर-सेविंग क्लॉक गेटिंग और एसिंक्रोनस कार्यविधि बहुत अधिक स्वाभाविक हैं।

स्टैटिक लॉजिक उदाहरण

उदाहरण के लिये, सीएमओएस एनएएनडी गेट के स्टैटिक लॉजिक कार्यान्वयन पर विचार करें:

यह परिपथ लॉजिक फ़ंक्शन को कार्यान्वित करता है

यदि A और B दोनों ऊंचे हैं, तब आउटपुट कम खींचा जाएगा। यदि A या B में से कोई भी कम है, तब आउटपुट उच्च खींचा जाएगा। हर समय, आउटपुट या तब कम या अधिक खींचा जाता है।

डायनेमिक लॉजिक उदाहरण

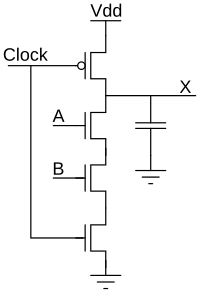

अब उसी लॉजिक फ़ंक्शन के डायनेमिक लॉजिक कार्यान्वयन पर विचार करें:

डायनेमिक लॉजिक सर्किट को दो चरणों की आवश्यकता होती है। पहला चरण, जब क्लॉक कम होती है, तब सेटअप चरण या प्रीचार्ज चरण कहा जाता है, और दूसरा चरण, जब क्लॉक अधिक होता है, तब मूल्यांकन चरण कहा जाता है। सेटअप चरण में, आउटपुट को बिना किसी नियम (इनपुट A और B के मानों पर कोई अंतर नहीं पड़ता) के उच्च संचालित किया जाता है। संधारित्र, जो इस गेट की भार धारिता का प्रतिनिधित्व करता है, आवेशित हो जाता है। चूँकि नीचे का ट्रांजिस्टर बंद है, इसलिए इस चरण के समय आउटपुट को कम गति पर चलाना असंभव है।

मूल्यांकन चरण के समय, क्लॉक ऊँची होती है। यदि A और B भी ऊंचे हैं, तब आउटपुट कम खींचा जाएगा। अन्यथा, आउटपुट उच्च (लोड कैपेसिटेंस के कारण) रहता है।

डायनेमिक लॉजिक में कुछ संभावित समस्याएँ हैं जो स्टैटिक लॉजिक में नहीं हैं। उदाहरण के लिए, यदि क्लॉक की गति बहुत धीमी है, तब आउटपुट उपयोग के लिए बहुत जल्दी खराब हो जाएगा। इसके अतिरिक्त, आउटपुट प्रत्येक क्लॉक चक्र के केवल भाग के लिए मान्य है, इसलिए इससे जुड़े उपकरण को वैध होने पर इसे समकालिक रूप से नमूना करना होगा।

इसके अतिरिक्त, जब A और B दोनों उच्च होते हैं, जिससेआउटपुट कम हो, तब परिपथ प्रत्येक क्लॉक चक्र के लिए वीडीडी से ग्राउंड पर आवेशित के कैपेसिटर लोड को पहले आवेशित करके और फिर प्रत्येक क्लॉक चक्र में कैपेसिटर को डिस्चार्ज करके पंप करेगा। यह परिपथ को (उच्च प्रतिबाधा से जुड़े आउटपुट के साथ) स्टैटिक संस्करण की तुलना में कम कुशल (जो सैद्धांतिक रूप से आउटपुट के अतिरिक्त किसी भी धारा को प्रवाहित करने की अनुमति नहीं देनी चाहिए) बनाता है, और जब A और B इनपुट स्टैटिक होते हैं और दोनों उच्च होते हैं, डायनेमिक एनएएनडी गेट, जब तक यह सही रूप से कार्य करता है, और क्लॉक दर के अनुपात में शक्ति का उपयोग करता है। भार धारिता को कम रखकर विद्युत अपव्यय को कम किया जा सकता है। यह, बदले में, अधिकतम चक्र समय को कम कर देता है, जिसके लिए उच्च न्यूनतम क्लॉक आवृत्ति की आवश्यकता होती है; उच्च आवृत्ति तब उल्लिखित संबंध द्वारा विद्युत की व्यय को बढ़ाती है। इसलिए, क्लॉक की गति और लोड कैपेसिटेंस के मध्य संतुलन से प्राप्त निश्चित थ्रेसहोल्ड से नीचे निष्क्रिय विद्युत की व्यय (जब दोनों इनपुट अधिक हों) को कम करना असंभव है।

लोकप्रिय कार्यान्वयन डोमिनोज़ लॉजिक है।

यह भी देखें

- डोमिनोज़ लॉजिक

- अनुक्रमिक लॉजिक

संदर्भ

- ↑ Lars Wanhammar (1999). डीएसपी एकीकृत सर्किट. Academic Press. p. 37. ISBN 978-0-12-734530-7.

- ↑ 2.0 2.1 Andrew Marshall; Sreedhar Natarajan (2002). SOI design: analog, memory and digital techniques. Springer. p. 125. ISBN 978-0-7923-7640-8.

- ↑ A. Albert Raj, T. Latha (21 October 2008). वीएलएसआई डिज़ाइन. PHI Learning Pvt. Ltd. p. 167. ISBN 978-81-203-3431-1.

- ↑ जैकबएनजी2007 >Bruce Jacob; Spencer Ng; David Wang (2007). मेमोरी सिस्टम: कैश, DRAM, डिस्क. Morgan Kaufmann. p. 270. ISBN 978-0-12-379751-3.

- ↑ David Harris (2001). तिरछा-सहिष्णु सर्किट डिजाइन. Morgan Kaufmann. p. 38. ISBN 978-1-55860-636-4.

- ↑ Richard Murray. "PocketBook II hardware".

- ↑ Gülzow, Peter. "कोई जोखिम नहीं, कोई मज़ा नहीं!". AMSAT-DL. Translated by Moe, Don. Archived from the original on 13 April 2013. Retrieved 15 September 2021.

- ↑ 8.0 8.1 "The Dark Knight: Intel's Core i7".

General references

- Sung-Mo Kang; Yusuf Leblebici (2003). CMOS digital integrated circuits: analysis and design (3rd ed.). McGraw-Hill. ISBN 978-0-07-246053-7. Chapter 9, "Dynamic logic circuits" (chapter 7 in the 2nd edition)

- R. Jacob Baker (2010). CMOS: Circuit Design, Layout, and Simulation (3rd ed.). Wiley-IEEE. ISBN 978-0-470-88132-3. Chapter 14, "Dynamic logic gates"

- Andrew Marshall; Sreedhar Natarajan (2002). SOI design: analog, memory and digital techniques. Springer. ISBN 978-0-7923-7640-8. Chapter 7, "Dynamic SOI Design"

बाहरी संबंध

- Introduction to CMOS VLSI Design – Lecture 9: Circuit Families – David Harris' lecture notes on the subject.