त्रि-आयामी एकीकृत परिपथ

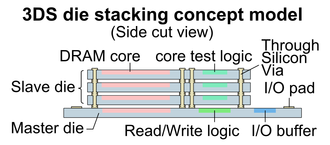

त्रि-आयामी एकीकृत परिपथ (3डी आईसी) एमओएसएफईटी (धातु-ऑक्साइड अर्धचालक) इंटीग्रेटेड परिपथ (आईसी) है, जो 16 या अधिक आईसी को एकत्र करके और उदाहरण के लिए, थ्रू-सिलिकॉन वियास (टीएसवी) का उपयोग करके उन्हें लंबवत रूप से जोड़कर बनाया जाता है। या क्यू-क्यू कनेक्शन, जिससे वे पारंपरिक दो आयामी प्रक्रियाओं की तुलना में कम शक्ति और छोटे पदचिह्न पर प्रदर्शन संशोधन प्राप्त करने के लिए एकल उपकरण के रूप में व्यवहार करें। 3डी आईसी कई 3डी एकीकरण योजनाओं में से एक है, जो माइक्रोइलेक्ट्रॉनिक और नैनो इलेक्ट्रॉनिक्स में विद्युत प्रदर्शन लाभ प्राप्त करने के लिए जेड-दिशा का लाभ उठाती है।

3डी एकीकृत परिपथ को वैश्विक (एकीकृत परिपथ पैकेजिंग), मध्यवर्ती (बन्ध पैड) और स्थानीय (ट्रांजिस्टर) स्तर पर उनके इंटरकनेक्ट पदानुक्रम के स्तर द्वारा वर्गीकृत किया जा सकता है।[1] सामान्य तौर पर, 3डी एकीकरण एक व्यापक शब्द है, जिसमें 3डी वेफर-स्तर पैकेजिंग (3डीडब्ल्यूएलपी), 2.5D और 3डी इंटरपोजर आधारित एकीकरण; 3डी स्टैक्ड आईसी (3डी-एसआईसी); 3डी विषम एकीकरण; और 3डी प्रणाली एकीकरण,[2][3] साथ ही वास्तविक मोनोलिथिक 3डी आईसी जैसी विधियाँ सम्मिलित हैं।

जिस्सो टेक्नोलॉजी रोडमैप कमेटी (जेआईसी) और अर्धचालक के लिए अंतर्राष्ट्रीय प्रौद्योगिकी रोडमैप (आईटीआरएस) जैसे अंतर्राष्ट्रीय संगठनों ने 3डी एकीकरण के मानकों और रोडमैप की स्थापना को आगे बढ़ाने के लिए विभिन्न 3डी एकीकरण विधियों को वर्गीकृत करने के लिए कार्य किया है।[4] 2010 के दशक तक, नैन्ड फ्लैश मेमोरी और मोबाइल उपकरणों में 3डी आईसी का व्यापक रूप से उपयोग किया जाता था।

प्रकार

3डी आईसी के विपरीत 3डी पैकेजिंग

3डी पैकेजिंग 3डी एकीकरण योजनाओं को संदर्भित करता है, जो वर्टिकल स्टैकिंग प्राप्त करने के लिए पारंपरिक इंटरकनेक्शन विधियों जैसे तार बन्धिंग और फ्लिप चिप पर विश्वास करते हैं। 3डी पैकेजिंग को पैकेज (3डी एसआईपी) और 3डी वेफर स्तर पैकेज (3डी डब्ल्यूएलपी) में 3डी प्रणाली में विभाजित किया जा सकता है। 3डी एसआईपी जो कुछ समय से मुख्यधारा के निर्माण में हैं और अच्छी तरह से स्थापित मूलभूत ढांचा है, जिसमें स्टैक्ड मेमोरी डाइस सम्मिलित हैं, जो तार बन्ध और पैकेज पर पैकेज (पीओपी) कॉन्फ़िगरेशन के साथ तार बन्ध या फ्लिप चिप विधि से जुड़े हुए हैं। पीओपी का उपयोग अलग-अलग प्रौद्योगिकियों को लंबवत रूप से एकीकृत करने के लिए किया जाता है। 3डी डब्ल्यूएलपी इंटरकनेक्ट बनाने के लिए पुनर्वितरण परत (आरडीएल) और वेफर बम्पिंग प्रक्रियाओं जैसी वेफर स्तर की प्रक्रियाओं का उपयोग करता है।

2.5D इंटरपोज़र 3डी डब्ल्यूएलपी है, जो सिलिकॉन वाया (टीएसवी) और आरडीएल के माध्यम से सिलिकॉन, ग्लास, या ऑर्गेनिक इंटरपोज़र पर साइड-बाय-साइड डाइस को जोड़ता है। सभी प्रकार की 3डी पैकेजिंग में, पैकेज में चिप ऑफ-चिप सिग्नलिंग का उपयोग करके संचार करते हैं, जैसे कि वे सामान्य परिपथ बोर्ड पर अलग-अलग पैकेज में लगाए गए हों।

3डी आईसी को 3डी स्टैक्ड आईसी (3डी एसआईसी) में विभाजित किया जा सकता है, जो टीएसवी इंटरकनेक्ट का उपयोग करके आईसी चिप को स्टैक करने और मोनोलिथिक 3डी आईसी को संदर्भित करता है, जो सेट के रूप में ऑन-चिप वायरिंग पदानुक्रम के स्थानीय स्तर पर 3डी इंटरकनेक्ट का एहसास करने के लिए फैब प्रक्रियाओं का उपयोग करता है। आईटीआरएस द्वारा आगे, इसका परिणाम उपकरण परतों के बीच सीधे लंबवत इंटरकनेक्ट में होता है। सैमसंग इलेक्ट्रॉनिक्स के 3डी वीनैन्ड उपकरणों में अखंड दृष्टिकोण का पहला उदाहरण देखा जाता है।[5]

2010 तक, मोबाइल उपकरणों में नैन्ड फ्लैश मेमोरी के लिए 3डी आईसी पैकेज का व्यापक रूप से उपयोग किया जाता था।[6]

3डी एसआईसी

डिजिटल इलेक्ट्रॉनिक्स व्यापार को हाल ही में प्रचलित सेंट्रल प्रोसेसिंग यूनिट घटकों को पूरा करने के लिए उच्च घनत्व अर्धचालक मेमोरी चिप की आवश्यकता होती है, और इस समस्या के समाधान के रूप में कई डाई स्टैकिंग विधि का सुझाव दिया गया है। जेईडीईसी ने सर्वर मेमोरी फोरम, 1-2 नवंबर, 2011, सांता क्लारा, सीए में आगामी डायनेमिक रैंडम-एक्सेस मेमोरी विधि में 3डी एसआईसी डाई स्टैकिंग योजना को प्रकट किया। अगस्त 2014 में, सैमसंग इलेक्ट्रॉनिक्स ने 64 का उत्पादन प्रारंभ किया गया था। 3डी टीएसवी पैकेज विधि का उपयोग कर उभरती हुई डीडीआर4 (डबल-डेटा दर 4) मेमोरी पर आधारित सर्वर के लिए GB एसडीआरएएम मॉड्यूल,[7] 3डी स्टैक्ड डीरैम के लिए नए प्रस्तावित मानकों में वाइड इनपुट/आउटपुट, वाइड इनपुट/आउटपुट 2, हाइब्रिड मेमोरी क्यूब, उच्च बैंडविड्थ मेमोरी सम्मिलित हैं।

अखंड 3डी आईसी

ट्रू मोनोलिथिक 3डी आईसी को वेफर (इलेक्ट्रॉनिक्स) पर परतों में बनाया जाता है, जो बाद में 3डी आईसी में वेफर डाइसिंग होता है। केवल सब्सट्रेट है, इसलिए संरेखण, थिनिंग, बन्धिंग या थ्रू-सिलिकॉन वियास की कोई आवश्यकता नहीं है। सामान्य तौर पर, अखंड 3डी आईसी अभी भी विकासशील विधि है और अधिकांश लोगों द्वारा इसे उत्पादन से कई वर्ष दूर माना जाता है।

ट्रांजिस्टर निर्माण को दो चरणों में विभाजित करके प्रक्रिया तापमान सीमाओं को संबोधित किया जा सकता है। उच्च तापमान चरण जो परत ट्रांसफर से पहले किया जाता है, उसके बाद ion-cut का उपयोग करके परत ट्रांसफर की जाती है, जिसे परत ट्रांसफर के रूप में भी जाना जाता है। इंसुलेटर पर सिलिकॉन का उत्पादन करने के लिए उपयोग किया गया है। पिछले दो दशकों से इन्सुलेटर पर सिलिकॉन (एसओआई) वेफर्स, कम तापमान (<400℃) बन्ध और क्लीव विधियों का उपयोग करके वस्तुतः दोष-मुक्त सिलिकॉन की कई पतली (10s–100s नैनोमीटर स्केल) परतें बनाई जा सकती हैं, और सक्रिय ट्रांजिस्टर परिपथरी के शीर्ष पर रखी जा सकती हैं। ईच और निक्षेपण प्रक्रियाओं का उपयोग करके ट्रांजिस्टर को अंतिम रूप देकर पालन करें। स्टैनफोर्ड विश्वविद्यालय में डीएआरपीए द्वारा प्रायोजित अनुदान के अनुसार इस अखंड 3डी आईसी विधि पर शोध किया गया है।

एमसीईए-लेटी ने मोनोलिथिक 3डी आईसी दृष्टिकोण भी विकसित किया, जिसे अनुक्रमिक 3डी आईसी कहा जाता है। 2014 में, फ्रांसीसी अनुसंधान संस्थान ने अपना CoolCube™ प्रस्तुत किया, निम्न-तापमान प्रक्रिया प्रवाह जो 3डीवीएलएसआई को सही मार्ग प्रदान करता है।[8]

स्टैनफोर्ड विश्वविद्यालय में, शोधकर्ताओं ने कार्बन नैनोट्यूब (सीएनटी) संरचनाओं के विपरीत सिलिकॉन का उपयोग करके वेफर-स्केल कम तापमान सीएनटी हस्तांतरण प्रक्रियाओं का उपयोग करके मोनोलिथिक 3डी आईसी डिजाइन किए जो 120 ℃ पर किए जा सकते हैं।[9]

3डी एसआईसी के लिए निर्माण प्रौद्योगिकियाँ

3डी आईसी डिज़ाइन के लिए कई विधियाँ हैं, जिनमें पुन: क्रिस्टलीकरण और वेफर बन्धिंग विधियाँ सम्मिलित हैं। वेफर बन्धिंग के दो प्रमुख प्रकार, क्यू-क्यू कनेक्शन (टीएसवी में उपयोग किए जाने वाले स्टैक्ड आईसी के बीच कॉपर-टू-कॉपर कनेक्शन)[10][11] और थ्रू-सिलिकॉन वाया (टीएसवी) हैं। 2014 तक, उच्च बैंडविड्थ मेमोरी (एचबीएम) और हाइब्रिड मेमोरी क्यूब जैसे कई मेमोरी उत्पाद लॉन्च किए गए हैं, जो टीएसवी के साथ 3डी आईसी स्टैकिंग को प्रयुक्त करते हैं। कई प्रमुख स्टैकिंग दृष्टिकोणों को प्रयुक्त किया जा रहा है और उनका पता लगाया जा रहा है। इनमें डाई-टू-डाई, डाई-टू-वेफर और वेफर-टू-वेफर सम्मिलित हैं।

- डाई-टू-डाई

- इलेक्ट्रॉनिक घटक मल्टीपल डाई पर बनाए जाते हैं, जो फिर संरेखित और बंधे होते हैं। बंधन से पहले या बाद में थिनिंग और टीएसवी का निर्माण किया जा सकता है। डाई-टू-डाई का लाभ यह है, कि प्रत्येक घटक डाई का पहले परीक्षण किया जा सकता है, जिससे व्यर्थ डाई पूरे एकत्र को व्यर्थ न करे।[12] इसके अतिरिक्त, 3डी आईसी में प्रत्येक डाई को पहले से ही बिन किया जा सकता है, जिससे उन्हें मिश्रित किया जा सके और विद्युत् के उपभोग और प्रदर्शन को अनुकूलित करने के लिए मिलान किया जा सके (उदाहरण के लिए मोबाइल अनुप्रयोग के लिए कम पावर प्रोसेस कॉर्नर से कई डाइस का मिलान करना)।

- डाई-टू-वेफर

- इलेक्ट्रॉनिक घटक दो अर्धचालक वेफर्स पर बनाए जाते हैं। वेफर काटा जाता है; सिंगुलेटेड डाई (इंटीग्रेटेड परिपथ) को दूसरे वेफर के डाई साइट्स पर संरेखित और बंधित किया जाता है। जैसा कि वेफर-ऑन-वेफर विधि में, थिनिंग और टीएसवी निर्माण बन्धिंग से पहले या बाद में किया जाता है। डाइसिंग से पहले एकत्र में अतिरिक्त डाई जोड़ी जा सकती है।[13]

- वेफर-टू-वेफर

- इलेक्ट्रॉनिक घटक दो या अधिक वेफर (इलेक्ट्रॉनिक्स) पर बनाए जाते हैं, जिन्हें फिर 3डी आईसी में संरेखित, बंधित और वेफर डाइसिंग किया जाता है। बंधन से पहले या बाद में प्रत्येक वेफर को पतला किया जा सकता है। वर्टिकल विद्युत् का संपर्क या तो बन्धिंग से पहले वेफर्स में बनाए जाते हैं या फिर बन्धिंग के बाद स्टैक में बनाए जाते हैं। ये थ्रू-सिलिकॉन वाया (टीएसवी) सक्रिय परतों और सक्रिय परत और बाहरी बन्ध पैड के बीच सिलिकॉन सब्सट्रेट (s) से होकर निकलते हैं। वेफ़र-टू-वेफ़र बन्धिंग प्रतिफल को कम कर सकती है, क्योंकि यदि किसी 3डी आईसी में N चिप में से कोई 1 व्यर्थ है, तो संपूर्ण 3डी आईसी व्यर्थ हो जाएगी। इसके अतिरिक्त, वेफर्स का आकार समान होना चाहिए, लेकिन कई विदेशी सामग्री (जैसे III-Vs) सीएमओएस लॉजिक या डायनेमिक रैंडम-एक्सेस मेमोरी (सामान्यतः 300 मिमी) की तुलना में बहुत छोटे वेफर्स पर निर्मित होती हैं, जो विषम एकीकरण को जटिल बनाती हैं।

लाभ

जबकि पारंपरिक सीएमओएस स्केलिंग प्रक्रिया सिग्नल प्रसार की गति में संशोधन करती है, वर्तमान निर्माण और चिप-डिज़ाइन विधियों से स्केलिंग अधिक कठिन और मूल्यवान होती जा रही है, आंशिक रूप से विद्युत्-घनत्व की कमी के कारण, और आंशिक रूप से क्योंकि ट्रांजिस्टर करते समय इंटरकनेक्ट तीव्र नहीं होते हैं।[14] 3डी आईसी 2डी डाइस को एकत्र करके और उन्हें तीसरे आयाम में जोड़कर स्केलिंग चुनौती को संबोधित करते हैं। यह प्लेनर लेआउट की तुलना में स्तरित चिप के बीच संचार को गति देने का वचन देता है।[15] 3डी आईसी कई महत्वपूर्ण लाभों का वचन देता है, जिनमें निम्न सम्मिलित हैं:

- पदचिह्न

- अधिक कार्यक्षमता छोटी से स्थान में फिट होती है। यह मूर के नियम का विस्तार करता है और नई पीढ़ी के छोटे लेकिन शक्तिशाली उपकरणों को सक्षम बनाता है।

- व्यय

- 3डी स्टैकिंग के साथ बड़ी चिप को कई छोटे डाइस में विभाजित करने से उपज में संशोधन हो सकता है और निर्माण व्यय को कम किया जा सकता है, यदि अलग-अलग डाइस का अलग-अलग परीक्षण किया जाता है।[16][17]

विषम एकीकरण

- परिपथ परतों को विभिन्न प्रक्रियाओं के साथ या विभिन्न प्रकार के वेफर्स पर भी बनाया जा सकता है। इसका अर्थ यह है कि घटकों को एक ही वेफर पर एक साथ बनाए जाने की तुलना में बहुत अधिक डिग्री तक अनुकूलित किया जा सकता है। इसके अतिरिक्त, असंगत निर्माण वाले घटकों को 3डी आईसी में जोड़ा जा सकता है।[18][3]

छोटा इंटरकनेक्ट

- औसत तार की लंबाई कम हो जाती है। शोधकर्ताओं द्वारा बताए गए सामान्य आंकड़े 10-15% के क्रम में हैं, लेकिन यह कमी अधिकतर लंबे इंटरकनेक्ट पर प्रयुक्त होती है, जो अधिक मात्रा में परिपथ विलंब को प्रभावित कर सकती है। यह देखते हुए कि 3डी तारों में परंपरागत इन-डाई तारों की तुलना में बहुत अधिक क्षमता है, परिपथ विलंब में संशोधन हो सकता है या नहीं भी हो सकता है।

- विद्युत्

- चिप पर सिग्नल रखने से इसकी विद्युत् उपभोग 10-100 गुना कम हो सकती है।[19] कम पैरासिटिक कपसिटंस उत्पन्न करके छोटे तार भी विद्युत् की उपभोग को कम करते हैं।[20] विद्युत् के बजट को कम करने से गर्मी का उत्पादन कम होता है, बैटरी का जीवनकाल बढ़ता है, और संचालन की व्यय कम होती है।

- डिजाइन

- लंबवत आयाम कनेक्टिविटी के उच्च क्रम को जोड़ता है और नई डिजाइन संभावनाएं प्रदान करता है।[3]

परिपथ सुरक्षा

- 3डी एकीकरण अस्पष्टता के माध्यम से सुरक्षा प्राप्त कर सकता है; स्टैक्ड संरचना परिपथ को रिवर्स इंजीनियरिंग करने के प्रयासों को जटिल बनाती है। संवेदनशील परिपथ को परतों के बीच इस तरह से विभाजित किया जा सकता है कि प्रत्येक परत के कार्य को अस्पष्ट किया जा सके।[21] इसके अतिरिक्त, 3डी एकीकरण समर्पित, प्रणाली मॉनिटर जैसी सुविधाओं को अलग-अलग परतों में एकीकृत करने की अनुमति देता है।[3] यहां उद्देश्य रनटाइम पर देखभाल रखने के लिए किसी भी कमोडिटी घटकों/चिप के लिए किसी प्रकार के हार्डवेयर फ़ायरवॉल (कंप्यूटिंग) को कार्यान्वित करना है, जो रन-टाइम हमलों के साथ-साथ दुर्भावनापूर्ण हार्डवेयर संशोधनों के विरुद्ध पूरे इलेक्ट्रॉनिक प्रणाली की रक्षा करने की मांग करता है।

- बैंडविड्थ (सिग्नल प्रोसेसिंग)

- 3डी एकीकरण परतों के बीच बड़ी संख्या में लंबवत वाया की अनुमति देता है। यह विभिन्न परतों में कार्यात्मक ब्लॉकों के बीच विस्तृत बैंडविड्थ बस (कंप्यूटिंग) के निर्माण की अनुमति देता है। विशिष्ट उदाहरण प्रोसेसर + मेमोरी 3डी स्टैक होगा, जिसमें प्रोसेसर के शीर्ष पर कैशे मेमोरी खड़ी होती है। यह व्यवस्था कैश और प्रोसेसर के बीच विशिष्ट 128 या 256 बिट्स की तुलना में बस को अधिक व्यापक बनाती है।[22] बदले में चौड़ी बसें मेमोरी वॉल की समस्या को कम करती हैं।[23]

चुनौतियां

क्योंकि यह विधि नई है, इसमें नई चुनौतियाँ हैं, जिनमें सम्मिलित हैं:

- व्यय

- स्केलिंग के साथ तुलना करने पर व्यय लाभ है, लेकिन इसे मुख्यधारा के उपभोक्ता अनुप्रयोगों में 3डी आईसी के व्यावसायीकरण के लिए चुनौती के रूप में भी पहचाना गया है। चूंकि इससे निपटने के लिए कार्य किया जा रहा है। चूंकि 3डी विधि नई और अत्यधिक जटिल है, लेकिन पूरी प्रक्रिया को बनाने वाली गतिविधियों में विभाजित होने पर निर्माण प्रक्रिया की व्यय आश्चर्यजनक रूप से सीधी है। आधार पर होने वाली गतिविधियों के संयोजन का विश्लेषण करके, व्यय चालकों की पहचान की जा सकती है। व्यय चालकों की पहचान हो जाने के बाद, यह निर्धारित करने के लिए कम जटिल प्रयास हो जाता है कि अधिकांश व्यय कहां से आती है और इससे भी महत्वपूर्ण बात यह है कि व्यय को कम करने की क्षमता कहां है।[24]

- उपज

- प्रत्येक अतिरिक्त निर्माण कदम दोषों के लिए संकट जोड़ता है। 3डी आईसी के व्यावसायिक रूप से व्यवहार्य होने के लिए, दोषों की मरम्मत की जा सकती है या सहन किया जा सकता है, या दोष घनत्व में संशोधन किया जा सकता है।[25][26]

गर्मी

- स्टैक के अन्दर जमा होने वाली गर्मी को दूर किया जाना चाहिए। यह अपरिहार्य उद्देश्य है, क्योंकि विद्युत निकटता थर्मल निकटता से संबंधित है। विशिष्ट थर्मल हॉटस्पॉट्स को अधिक सावधानी से प्रबंधित किया जाना चाहिए।

- डिजाइन जटिलता

- 3डी एकीकरण का पूरा लाभ लेने के लिए परिष्कृत डिजाइन विधियों और नए कंप्यूटर एडेड डिजाइन उपकरणों की आवश्यकता होती है।[27]

टीएसवी-प्रस्तुत ओवरहेड

- टीएसवी गेट्स और इम्पैक्ट फ़्लोरप्लान की तुलना में बड़े हैं। 45 एनएम प्रौद्योगिकी नोड पर, 10μm x 10μm टीएसवी के क्षेत्र पदचिह्न की तुलना लगभग 50 गेटों से की जा सकती है।[28] इसके अतिरिक्त, विनिर्माण क्षमता लैंडिंग पैड और कीप-आउट ज़ोन की मांग करती है, जो टीएसवी क्षेत्र के पदचिह्न को और बढ़ाते हैं। प्रौद्योगिकी विकल्पों के आधार पर, टीएसवी लेआउट संसाधनों के कुछ सबसेट को ब्लॉक कर देते हैं।[28] धातुकरण से पहले पहले टीएसवी का निर्माण किया जाता है, इस प्रकार उपकरण परत को अधिकृत कर लिया जाता है और प्लेसमेंट बाधाओं में परिणाम होता है। वाया-लास्ट टीएसवी धातुकरण के बाद निर्मित होते हैं और चिप से निकलते हैं। इस प्रकार, वे उपकरण और धातु दोनों परतों को अधिकृत कर लेते हैं, जिसके परिणामस्वरूप प्लेसमेंट और रूटिंग बाधाएं होती हैं। जबकि टीएसवी के उपयोग से सामान्यतः तार की लम्बाई कम होने की आशा की जाती है, यह टीएसवी की संख्या और उनकी विशेषताओं पर निर्भर करता है।[28] इसके अतिरिक्त, इंटर-डाई पार्टिशनिंग की ग्रैन्युलैरिटी वायरलेंथ को प्रभावित करती है। यह सामान्यतः मध्यम (20-100 मॉड्यूल वाले ब्लॉक) और मोटे (ब्लॉक-स्तरीय विभाजन) ग्रैन्युलैरिटी के लिए घटता है, लेकिन ठीक (गेट-स्तर विभाजन) ग्रैन्युलैरिटी के लिए बढ़ जाता है।[28]

परीक्षण

- उच्च समग्र उपज प्राप्त करने और व्यय कम करने के लिए स्वतंत्र डाइस का अलग परीक्षण आवश्यक है।[26][29] चूंकि, 3डी आईसी में आसन्न सक्रिय परतों के बीच कड़े एकीकरण के लिए एक ही परिपथ मॉड्यूल के विभिन्न वर्गों के बीच महत्वपूर्ण मात्रा में इंटरकनेक्ट की आवश्यकता होती है जो अलग-अलग डाइ में विभाजित किए गए थे। आवश्यक टीएसवी द्वारा प्रस्तुत किए गए बड़े पैमाने पर ओवरहेड के अतिरिक्त, ऐसे मॉड्यूल के खंड, उदाहरण के लिए, गुणक, पारंपरिक विधियों द्वारा स्वतंत्र रूप से परीक्षण नहीं किया जा सकता है। यह विशेष रूप से 3डी में निर्धारित समय-महत्वपूर्ण पथों पर प्रयुक्त होता है।

- मानकों का अभाव

- टीएसवी-आधारित 3डी आईसी डिज़ाइन, निर्माण और पैकेजिंग के लिए कुछ मानक हैं, चूंकि इस उद्देश्य का समाधान किया जा रहा है।[30][31] इसके अतिरिक्त, कई एकीकरण विकल्प ढूंढे जा रहे हैं जैसे कि टू-लास्ट, टू-फर्स्ट, वाया-मिडिल,[32] इंटरपोजर[33] या प्रत्यक्ष बन्धिंग, इत्यादि।

- विषम एकीकरण आपूर्ति श्रृंखला

- विषम रूप से एकीकृत प्रणालियों में, विभिन्न भागों के आपूर्तिकर्ताओं में से एक भाग की देरी से पूरे उत्पाद की डिलीवरी में देरी होती है, और इसलिए प्रत्येक 3डी आईसी भाग आपूर्तिकर्ताओं के लिए राजस्व में देरी होती है।

- स्पष्ट रूप से परिभाषित स्वामित्व का अभाव

- यह स्पष्ट नहीं है कि 3डी आईसी एकीकरण और पैकेजिंग/असेंबली का स्वामी कौन होना चाहिए। यह उन्नत अर्धचालक इंजीनियरिंग या उत्पाद ओईएम जैसे असेंबली हाउस हो सकते हैं।

डिजाइन शैलियों

विभाजन की सूक्ष्मता के आधार पर, विभिन्न डिजाइन शैलियों को प्रतिष्ठित किया जा सकता है। गेट-स्तरीय एकीकरण कई चुनौतियों का सामना करता है और वर्तमान में ब्लॉक-स्तरीय एकीकरण से कम व्यावहारिक प्रतीत होता है।[34]

- गेट-स्तरीय एकीकरण

- यह शैली मानक सेलों को कई डाइस के बीच विभाजित करती है। यह तार की लंबाई में कमी और महान लचीलेपन का प्रमाण देता है। चूंकि, जब तक कुछ न्यूनतम आकार के मॉड्यूल को संरक्षित नहीं किया जाता है, तब तक वायरलेस लंबाई में कमी को कम आंका जा सकता है। दूसरी ओर, इसके प्रतिकूल प्रभावों में इंटरकनेक्ट के लिए भारी संख्या में आवश्यक टीएसवी सम्मिलित हैं। इस डिज़ाइन शैली के लिए 3डी स्थान और मार्ग |स्थान-और-मार्ग उपकरण की आवश्यकता होती है, जो अभी तक अनुपलब्ध हैं। इसके अतिरिक्त, डिज़ाइन ब्लॉक को कई डाई में विभाजित करने का अर्थ है कि यह डाई स्टैकिंग से पहले पूरी तरह से अर्धचालक फैब्रिकेशन # उपकरण परीक्षण नहीं हो सकता है। डाई स्टैकिंग (पोस्ट-बन्ध परीक्षण) के बाद, एक भी विफल डाई कई अच्छे डाई को अनुपयोगी बना सकती है, उपज को कम कर सकती है। यह शैली प्रक्रिया भिन्नता (अर्धचालक) के प्रभाव को भी बढ़ाती है, विशेष रूप से इंटर-डाई भिन्नता। वास्तव में, 3डी आईसी एकीकरण के मूल प्रमाण के विपरीत, 2डी में निर्धारित समान परिपथ की तुलना में 3डी लेआउट अधिक व्यर्थ परिणाम दे सकता है।[35] इसके अतिरिक्त, इस डिजाइन शैली को उपलब्ध बौद्धिक संपदा को फिर से डिजाइन करने की आवश्यकता है, क्योंकि वर्तमान अर्धचालक बौद्धिक संपदा कोर और ईडीए उपकरण 3डी एकीकरण के लिए प्रावधान नहीं करते हैं।

- ब्लॉक-स्तरीय एकीकरण

- यह शैली अलग-अलग डाइस के लिए पूरे डिज़ाइन ब्लॉक को असाइन करती है। डिज़ाइन ब्लॉक अधिकांश नेटलिस्ट कनेक्टिविटी को समाहित करते हैं और वैश्विक इंटरकनेक्ट की छोटी संख्या से जुड़े होते हैं। इसलिए, ब्लॉक-स्तरीय एकीकरण टीएसवी ओवरहेड को कम करने का प्रमाण देता है। जटिल 3डी प्रणालियों में विभिन्न प्रकार के डाइस का संयोजन तीव्र और कम-शक्ति यादृच्छिक तर्क, कई मेमोरी प्रकार, एनालॉग और आरएफ परिपथ आदि के लिए अलग-अलग प्रौद्योगिकी नोड्स पर अलग-अलग निर्माण प्रक्रियाओं की आवश्यकता होती है। ब्लॉक-स्तरीय एकीकरण, जो अलग और अनुकूलित निर्माण प्रक्रियाओं की अनुमति देता है, इस प्रकार यह 3डी एकीकरण के लिए महत्वपूर्ण प्रतीत होता है। इसके अतिरिक्त, यह शैली वर्तमान 2डी डिज़ाइन से 3डी आईसी डिज़ाइन में संक्रमण की सुविधा प्रदान कर सकती है। मूल रूप से, 3डी-जागरूक उपकरण केवल विभाजन और थर्मल विश्लेषण के लिए आवश्यक हैं।[36] 2डी उपकरणों और 2डी ब्लॉक्स का उपयोग करके अलग-अलग डाइस को डिज़ाइन किया जाएगा। यह विश्वसनीय आईपी ब्लॉकों की व्यापक उपलब्धता से प्रेरित है। उपलब्ध 2डी आईपी ब्लॉक का उपयोग करना और आईपी ब्लॉक को फिर से डिज़ाइन करने और टीएसवी को एम्बेड करने के अतिरिक्त ब्लॉक के बीच खाली स्थान में अनिवार्य टीएसवी को रखना अधिक सुविधाजनक है।[34] परीक्षण के लिए डिजाइन संरचनाएं आईपी ब्लॉक का प्रमुख घटक हैं और इसलिए इसका उपयोग 3डी आईसी के परीक्षण की सुविधा के लिए किया जा सकता है। इसके अतिरिक्त, महत्वपूर्ण पथों को अधिकतर 2डी ब्लॉकों के अन्दर एम्बेड किया जा सकता है, जो टीएसवी के प्रभाव को सीमित करता है और विनिर्माण उपज पर इंटर-डाई भिन्नता को सीमित करता है। अंत में, आधुनिक चिप डिजाइन के लिए अधिकांशतः इंजीनियरिंग चेंज ऑर्डर चिप डिजाइन अंतिम मिनट में इंजीनियरिंग परिवर्तन की आवश्यकता होती है। व्यय को सीमित करने के लिए इस तरह के परिवर्तनों के प्रभाव को एकल डाइस तक सीमित करना आवश्यक है।

इतिहास

1960 में बेल लैब्स में मोहम्मद ओटाला द्वारा एमओएस एकीकृत परिपथ (एमओएस आईसी) चिप को पहली बार प्रस्तावित किए जाने के कई वर्ष बाद,[37] 1964 में टेक्सस उपकरण के शोधकर्ता रॉबर्ट डब्ल्यू हैस्टी, रॉलैंड ई. जॉनसन और एडवर्ड डब्ल्यू महल द्वारा त्रि-आयामी एमओएस एकीकृत परिपथ की अवधारणा प्रस्तावित की गई थी।[38] 1969 में, एनईसी के शोधकर्ताओं कात्सुहिरो ओनोडा, रियो इगारशी, तोशियो वाडा, शो नाकानुमा और टोरू सूजाइड द्वारा त्रि-आयामी एमओएस एकीकृत परिपथ मेमोरी चिप की अवधारणा प्रस्तावित की गई थी।[39]

आर्म ने उच्च-डेंसिटी 3डी लॉजिक परीक्षण चिप बनाई है,[40] और इंटेल अपने फोवरोस 3डी लॉजिक चिप पैकिंग के साथ इसका उपयोग करके सीपीयू को शिप करने की योजना बना रहा है।[41]

प्रदर्शन (1983–2012)

जापान (1983–2005)

3डी आईसी का पहली बार जापान में 1980 के दशक में सफलतापूर्वक प्रदर्शन किया गया था, जहां 3डी आईसी पर अनुसंधान और विकास (आर और डी) 1981 में रिसर्च एंड डेवलपमेंट एसोसिएशन फॉर फ्यूचर (न्यू) इलेक्ट्रॉन उपकरणेस द्वारा थ्री डायमेंशनल परिपथ एलीमेंट आर एंड डी प्रोजेक्ट के साथ प्रारंभ किया गया था।[42] प्रारंभ में 3डी आईसी डिजाइन के दो रूपों की जांच की जा रही थी, पुन: क्रिस्टलीकरण और वेफर बन्धिंग, जिसमें पुन: क्रिस्टलीकरण का उपयोग करने वाले प्रारंभिक सफल प्रदर्शन थे।[11] अक्टूबर 1983 में, एस. कवामुरा, नोबुओ सासाकी और टी. इवई सहित द्रोह अनुसंधान दल ने लेजर बीम पुनर्संरचना का उपयोग करते हुए त्रि-आयामी पूरक धातु-ऑक्साइड-अर्धचालक (सीएमओएस) एकीकृत परिपथ का अर्धचालक उपकरण निर्माण सफलतापूर्वक किया। इसमें संरचना सम्मिलित थी, जिसमें एक प्रकार का ट्रांजिस्टर सीधे विपरीत प्रकार के ट्रांजिस्टर के ऊपर बना होता है, जिसमें अलग-अलग द्वार और बीच में इन्सुलेटर होता है। सिलिकॉन नाइट्राइड और फॉस्फोसिलिकेट ग्लास (पीएसजी) फिल्म की डबल-परत का उपयोग ऊपर और नीचे के उपकरणों के बीच मध्यवर्ती इन्सुलेट परत के रूप में किया गया था। इसने अलग-अलग गेट्स और बीच में इन्सुलेटिंग परत के साथ लंबवत-स्टैक्ड ट्रांजिस्टर से बना बहु-स्तरित 3 डी उपकरण को साकार करने का आधार प्रदान किया।[43] दिसंबर 1983 में, उसी फुजित्सु अनुसंधान दल ने सिलिकॉन-पर-इन्सुलेटर (एसओआई) सीएमओएस संरचना के साथ 3डी एकीकृत परिपथ का निर्माण किया।[44] अगले वर्ष, उन्होंने बीम पुन: क्रिस्टलीकरण का उपयोग करके लंबवत-स्टैक्ड दोहरी एसओआई/सीएमओएस संरचना के साथ 3डी गेट सरणी तैयार की।[45]

1986 में, मित्सुबिशी इलेक्ट्रिक के शोधकर्ताओं योइची अकासाका और तदाशी निशिमुरा ने 3डी आईसी के लिए मूलभूत अवधारणाएं और प्रस्तावित प्रौद्योगिकियां प्रस्तुत कीं थी।[46][47] अगले वर्ष, निशिमुरा, अकासाका और ओसाका विश्वविद्यालय के स्नातक यासुओ इनूए सहित मित्सुबिशी शोध दल ने 3डी आईसी पर इमेज सिग्नल प्रोसेसर (आईएसपी) तैयार किया, जिसमें फोटो सेंसर, सीएमओएस ए-टू-डी कनवर्टर, अंकगणितीय तर्क इकाइयां और तीन-परत संरचना में व्यवस्थित शिफ्ट रजिस्टर (एएलयू) सम्मिलित हैं।[48] 1989 में, योशीहिरो हयाशी के नेतृत्व में एनईसी शोध दल ने लेज़र बीम क्रिस्टलीकरण का उपयोग करके चार-परत संरचना वाला 3डी आईसी बनाया।[49][46] 1990 में, के. यामाजाकी, वाई. इतोह और ए. वाडा सहित पैनासोनिक की शोध टीम ने चार-परत 3डी आईसी पर समानांतर प्रसंस्करण (डीएसपी कार्यान्वयन) इमेज सिग्नल प्रोसेसर तैयार किया, जिसमें एसओआई (सिलिकॉन-ऑन-इन्सुलेटर) परतें थीं। लेजर पुनर्संरचना, और प्रकाशीय संवेदक, स्तर डिटेक्टर, अर्धचालक मेमोरी और एएलयू से युक्त चार परतें थी।[50]

3डी आईसी डिजाइन का सबसे सामान्य रूप वेफर बन्धिंग है।[11] वेफर बन्धिंग को प्रारंभ में संचयी रूप से बंधुआ आईसी (क्यूबिक) कहा जाता था, जिसने 1981 में जापान में थ्री डायमेंशनल परिपथ एलिमेंट R&D प्रोजेक्ट के साथ विकास प्रारंभ किया और 1990 में योशिहिरो हयाशी की एनईसी रिसर्च टीम द्वारा पूरा किया गया, जिसने ऐसी विधि का प्रदर्शन किया जिसमें कई पतली-फिल्म उपकरण हैं। बंधुआ संचयी रूप से, जो बड़ी संख्या में उपकरण परतों की अनुमति देगा। उन्होंने अलग-अलग वेफर्स में अलग-अलग उपकरणों के निर्माण, वेफर्स की मोटाई में कमी, फ्रंट और बैक लीड प्रदान करने और पतले डाई (एकीकृत परिपथ) को एक-दूसरे से जोड़ने का प्रस्ताव दिया। उन्होंने क्यूबिक विधि का उपयोग ऊपर से नीचे तक दो सक्रिय परत वाले उपकरण को बनाने और परीक्षण करने के लिए किया, जिसमें बल्क-Si एनएमओएस एफईटी निचली परत और पतली एनएमओएस एफईटी ऊपरी परत होती है, और प्रस्तावित क्यूबिक तकनीक जो तीन से अधिक सक्रिय परतों के साथ 3डी आईसी का निर्माण कर सकती है।[46][42][51]

1980 के दशक में जापान में थ्रू-सिलिकॉन थ्रू (टीएसवी) प्रक्रिया से निर्मित पहले 3डी आईसी स्टैक्ड चिप का आविष्कार किया गया था। हिताची ने 1983 में जापानी पेटेंट अंकित किया, उसके बाद 1984 में फुजित्सु ने अंकित कराया। 1986 में, फुजित्सु द्वारा अंकित जापानी पेटेंट ने टीएसवी का उपयोग करके स्टैक्ड चिप संरचना का वर्णन किया।[42] 1989 में, तोहोकू विश्वविद्यालय के मित्सुमसा कोयोनागी ने टीएसवी के साथ वेफर-टू-वेफर बन्धिंग की विधि का बीड़ा उठाया, जिसका उपयोग उन्होंने 1989 में 3डी बड़े पैमाने पर एकीकरण चिप बनाने के लिए किया।[42][52][53] 1999 में, जापान में एसोसिएशन ऑफ़ सुपर-एडवांस्ड इलेक्ट्रॉनिक्स टेक्नोलॉजीज (एसेट) ने टीएसवी विधि का उपयोग करके 3डी आईसी चिप के विकास के लिए धन देना प्रारंभ किया, जिसे उच्च घनत्व इलेक्ट्रॉनिक प्रणाली इंटीग्रेशन टेक्नोलॉजी प्रोजेक्ट पर आर&डी कहा जाता है।[42][54] थ्रू-सिलिकॉन थ्रू (टीएसवी) शब्द को ट्रू-सी टेक्नोलॉजीज के शोधकर्ताओं सर्गेई सवास्तिओक, ओ. सिनियाग्यूइन और ई. कोर्कज़िन्स्की द्वारा गढ़ा गया था, जिन्होंने 2000 में 3डी वेफर-स्तरीय पैकेजिंग (डब्ल्यूएलपी) समाधान के लिए टीएसवी विधि प्रस्तावित की थी।[55]

मित्सुमसा कोयनागी के नेतृत्व में तोहोकू विश्वविद्यालय में कोयनागी समूह ने 2000 में तीन-परत मेमोरी चिप, 2001 में तीन-परत कृत्रिम रेटिना चिप, 2002 में तीन-परत माइक्रोप्रोसेसर और 2005 में चिप दस-परत मेमोरी बनाने के लिए टीएसवी विधि का उपयोग किया।[52] उसी वर्ष, कौस्तव बनर्जी, शुकरी जे. सौरी, पवन कपूर और कृष्णा सी. सारस्वत की स्टैनफोर्ड यूनिवर्सिटी की शोध टीम ने नई 3डी चिप डिजाइन प्रस्तुत की, जो इंटरकनेक्ट संबंधित समस्याओं को कम करने के लिए ऊर्ध्वाधर आयाम का उपयोग करती है और प्रौद्योगिकियों के विषम एकीकरण की सुविधा प्रदान करती है। प्रणाली- ऑन- चिप (एसओसी) डिजाइन का अनुभव किया गया।[56][57]

2001 में, टी. इमोटो, एम. मात्सुई और सी. ताकुबो सहित तोशीबा अनुसंधान दल ने 3डी आईसी पैकेजों के निर्माण के लिए प्रणाली ब्लॉक मॉड्यूल वेफर बन्धिंग प्रक्रिया विकसित की थी।[58][59]

यूरोप (1988–2005)

फ्राउनहोफर सोसायटी और सीमेंस ने 1987 में 3डी आईसी एकीकरण पर शोध प्रारंभ किया।[42] 1988 में, उन्होंने पॉली-सिलिकॉन के पुन: क्रिस्टलीकरण के आधार पर 3डी सीएमओएस आईसी उपकरणों का निर्माण किया।[60] 1997 में, इंटर-चिप थ्रू (आईसीवी) विधि फ्राउनहोफर द्वारा–पीटर रैम, मैनफ़्रेड एंगेलहार्ट, वर्नर पामलर, क्रिस्टोफ़ लैंडेसबर्गर और अर्मिन क्लम्प सहित सीमेंस अनुसंधान दल विकसित की गई थी।[61] यह सीमेंस सीएमओएस फैब वेफर्स पर आधारित पहली औद्योगिक 3डी आईसी प्रक्रिया थी। उस टीएसवी प्रक्रिया की भिन्नता को बाद में टीएसवी-एसएलआईडी (ठोस तरल अंतर-प्रसार) विधि कहा गया।[62] यह कम तापमान वाले वेफर बन्धिंग और इंटर-चिप वियास का उपयोग करके आईसी उपकरणों के ऊर्ध्वाधर एकीकरण पर आधारित 3डी आईसी डिजाइन के लिए दृष्टिकोण था, जिसे उन्होंने पेटेंट कराया था।

प्रासंगिक 3डी एकीकरण प्रौद्योगिकियों के उत्पादन के लिए रैम ने उद्योग-अकादमिक संघ विकसित किया। सीमेंस और फ्रौनहोफर के बीच जर्मन वित्त पोषित सहकारी वीआईसी परियोजना में, उन्होंने पूर्ण औद्योगिक 3डी आईसी स्टैकिंग प्रक्रिया (1993-1996) का प्रदर्शन किया। अपने सीमेंस और फ्राउनहोफर सहयोगियों के साथ, रैम ने 3डी धातुकरण [Ti] जैसी प्रमुख प्रक्रियाओं का विवरण दिखाते हुए परिणाम प्रकाशित किए। ग्रासल, पी. रेम, एम. एंगेलहार्ड्ट, जेड गेब्रिक, ओ. स्पिंडलर, वीएलएसआई/यूएलएसआई इंटरकनेक्शन मेटालाइज़ेशन सम्मेलन के लिए पहला अंतर्राष्ट्रीय डाइलेक्ट्रिक्स - ड्युमिक, सांता क्लारा, सीए, 20–22 फरवरी, 1995 और ईसीटीसी 1995 में उन्होंने शीघ्र प्रस्तुत किया प्रोसेसर में स्टैक्ड मेमोरी पर जांच की।[63]

2000 के दशक के प्रारंभ में, फ्रौनहोफर और इन्फिनॉन म्यूनिख के शोधकर्ताओं की टीम ने 3डी टीएसवी प्रौद्योगिकियों की जांच की, जिसमें जर्मन/ऑस्ट्रियाई यूरेका परियोजना वीएसआई के अन्दर डाई-टू-सब्सट्रेट स्टैकिंग पर विशेष ध्यान दिया गया और पहले यूरोपीय 3डी के रूप में यूरोपीय एकीकृत परियोजनाओं ई-क्यूब्स का प्रारंभ हुआ। प्रौद्योगिकी मंच, और ए.ओ., इन्फिनियन, सीमेंस, ईपीएफएल, आईएमईसी और टाइन्डल के साथ ई-ब्रेन, जहां विषम 3डी एकीकृत प्रणाली प्रदर्शकों का निर्माण और मूल्यांकन किया गया था। ई-दिमाग परियोजना का विशेष ध्यान अत्यधिक विश्वसनीय 3डी एकीकृत सेंसर प्रणाली के लिए उपन्यास कम तापमान प्रक्रियाओं का विकास था।[64]

संयुक्त राज्य अमेरिका (1999–2012)

कॉपर-टू-कॉपर वेफर बन्धिंग, जिसे क्यू-क्यू कनेक्शन या क्यू-क्यू वेफर बन्धिंग भी कहा जाता है, को 1999 में एंडी फैन, अदनान-उर रहमान और राफेल रीफ से मिलकर शोध दल द्वारा एमआईटी में विकसित किया गया था।[11][65] रीफ और फैन ने 2001–2002 के समय कुआन-नेंग चेन, शामिक दास, चुआन सेंग टैन और निशा चेका सहित अन्य एमआईटी शोधकर्ताओं के साथ क्यू-क्यू वेफर बन्धिंग की जांच की।[11] 2003 में, डीएआरपीए और माइक्रोइलेक्ट्रॉनिक सेंटर ऑफ़ नॉर्थ कैरोलिना (एमसीएनसी) ने 3डी आईसी विधि पर R&D का वित्तपोषण प्रारंभ किया।[42]

2004 में, तेजारोन अर्धचालक[66] छह अलग-अलग डिजाइनों से कार्य कर रहे 3डी उपकरणों का निर्माण किया।[67] चिप दो परतों में वर्टिकल इंटरकनेक्शन के लिए पहले टंगस्टन टीएसवी के साथ बनाए गए थे। दो वेफर्स को आमने-सामने रखा गया और तांबे की प्रक्रिया से जोड़ा गया। शीर्ष वेफर को पतला किया गया था और दो-वेफर स्टैक को चिप में डाला गया था। पहली चिप का परीक्षण साधारण मेमोरी रजिस्टर था, लेकिन सेट में सबसे उल्लेखनीय 8051 प्रोसेसर/मेमोरी स्टैक था[68] जिसने समान 2डी असेंबली की तुलना में बहुत अधिक गति और कम विद्युत् की उपभोग का प्रदर्शन किया।

2004 में, इंटेल ने पेंटियम 4 सीपीयू का 3डी संस्करण प्रस्तुत किया।[69] चिप को फेस-टू-फेस स्टैकिंग का उपयोग करके दो डाइस के साथ निर्मित किया गया था, जिसने संरचना के माध्यम से घने की अनुमति दी थी। बैकसाइड टीएसवी का उपयोग इनपुट/आउटपुट और विद्युत् आपूर्ति के लिए किया जाता है। 3डी फ्लोरप्लान के लिए, डिजाइनरों ने मैन्युअल रूप से विद्युत् की कमी और प्रदर्शन में संशोधन के उद्देश्य से प्रत्येक डाई में कार्यात्मक ब्लॉकों की व्यवस्था की थी। थर्मल हॉटस्पॉट को सीमित करने के लिए बड़े और उच्च-शक्ति वाले ब्लॉकों को विभाजित करना और सावधानीपूर्वक पुनर्व्यवस्था की अनुमति देना था। 2डी पेंटियम 4 की तुलना में 3डी डिजाइन 15% प्रदर्शन संशोधन (पाइपलाइन चरणों को समाप्त करने के कारण) और 15% विद्युत् की बचत (रिपीटर और कम वायरिंग के कारण) प्रदान करता है।

इंटेल द्वारा 2007 में प्रारंभ की गई टेराफ्लॉप्स रिसर्च चिप स्टैक्ड मेमोरी के साथ प्रायोगिक 80-कोर डिज़ाइन है। मेमोरी बैंडविड्थ की उच्च मांग के कारण, पारंपरिक इनपुट/आउटपुट दृष्टिकोण 10 से 25 W की उपभोग करेगा।[29] उस पर संशोधन करने के लिए, इंटेल डिजाइनरों ने टीएसवी-आधारित मेमोरी बस प्रयुक्त की थी। प्रत्येक कोर स्टेटिक रैंडम-एक्सेस मेमोरी डाई में मेमोरी टाइल से जुड़ा होता है, जो लिंक के साथ 12 GB/s बैंडविड्थ प्रदान करता है, जिसके परिणामस्वरूप केवल 2.2 W की उपभोग करते हुए 1 TB/s की कुल बैंडविड्थ होती है।

2008 में रोचेस्टर विश्वविद्यालय में प्रोफेसर ईबी फ्रीडमैन और उनके छात्रों द्वारा 3डी प्रोसेसर का अकादमिक कार्यान्वयन प्रस्तुत किया गया था। चिप 1.4 GHz पर चलती है और इसे स्टैक्ड चिप के बीच अनुकूलित वर्टिकल प्रोसेसिंग के लिए डिज़ाइन किया गया था जो 3डी प्रोसेसर क्षमताओं को प्रदान करता है, जो पारंपरिक स्तरित चिप तक नहीं पहुंच सकता।[70] त्रि-आयामी चिप के निर्माण में चुनौती यह थी, कि सभी परतों को बिना किसी बाधा के सामंजस्य के साथ कार्य किया जाए जो परत से दूसरी परत तक जाने वाली सूचना के टुकड़े में हस्तक्षेप करे।[71]

आईएसएससीसी 2012 में, ग्लोबल फाउंड्रीज की 130 एनएम प्रक्रिया और तेजारॉन की फास्टैक विधि का उपयोग करते हुए दो 3डी-आईसी-आधारित मल्टी-कोर डिजाइन प्रस्तुत किए गए और प्रदर्शित किए गए:

- 3डी-एमएपीएस,[72] जॉर्जिया तकनीकी संस्थान में स्कूल ऑफ इलेक्ट्रिकल एंड कंप्यूटर इंजीनियरिंग के शोधकर्ताओं द्वारा टू-लॉजिक-डाई स्टैक के साथ 64 कस्टम कोर कार्यान्वयन का प्रदर्शन किया गया।

- सेंटिप3डी,[73] एआरएम कॉर्टेक्स-एम3 कोर पर आधारित नियर-थ्रेशोल्ड डिज़ाइन, मिशिगन विश्वविद्यालय में इलेक्ट्रिकल इंजीनियरिंग और कंप्यूटर विज्ञान विभाग से था।

वाणिज्यिक 3डी आईसी (2004–उपस्थित)

3डी आईसी चिप का सबसे पहला व्यावसायिक उपयोग सोनी के प्लेस्टेशन पोर्टेबल (पीएसपी) हैंडहेल्ड गेम कंसोल में हुआ था, जिसे 2004 में प्रचलित किया गया था। पीएसपी हार्डवेयर में ईडीरैम (एम्बेडेड डायनेमिक रैंडम-एक्सेस मेमोरी) मेमोरी सम्मिलित है, जिसे तोशीबा द्वारा 3डी प्रणाली-इन में निर्मित किया गया है। पैकेज चिप दो डाई (एकीकृत परिपथ) के साथ लंबवत रूप से खड़ी होती है।[6] तोशिबा ने उस समय इसे सेमी-एम्बेडेड डीरैम कहा, बाद में इसे स्टैक्ड पैकेज ऑन पैकेज|चिप-ऑन-चिप (सीओसी) समाधान कहा था।[6][74]

अप्रैल 2007 में, तोशिबा ने आठ-परत वाली 3डी आईसी, 16 GB टीएचजीएएमएम्बेडेड एनएएनडी फ्लैश मेमोरी चिप का व्यवसायीकरण किया, जिसे आठ स्टैक्ड 2 GB एनएएनडी फ्लैश चिप के साथ निर्मित किया गया था।[75] सितंबर 2007 में, हाइनिक्स ने 16 GB फ्लैश मेमोरी चिप के साथ 24-लेयर 3डी आईसी विधि का प्रारंभ किया, जिसे वेफर बन्धिंग प्रक्रिया का उपयोग करके 24 स्टैक्ड एनएएनडी फ्लैश चिप के साथ निर्मित किया गया था।[76] तोशिबा ने 2008 में अपनी 32 GB टीएचजीबीएम फ्लैश चिप के लिए आठ-परत वाली 3डी आईसी का भी उपयोग किया था।[77] 2010 में, तोशिबा ने अपने 128 GB टीएचजीबीएम2 फ्लैश चिप के लिए 16-लेयर 3डी आईसी का उपयोग किया, जिसे 16 स्टैक्ड 8 GB चिप के साथ निर्मित किया गया था।[78] 2010 के दशक में, 3डी आईसी मोबाइल उपकरणों में एनएएनडी फ्लैश मेमोरी के लिए मल्टी-चिप पैकेज और पैकेज समाधान के रूप में व्यापक व्यावसायिक उपयोग में आया।[6]

एल्पिडा मेमोरी ने सितंबर 2009 में पहली 8 GB डीआरएएम चिप (चार डीडीआर3 एसडीआरएएम डाइस के साथ खड़ी) विकसित की, और इसे जून 2011 में प्रचलित किया।[79] टीएसएमसी ने जनवरी 2010 में टीएसवी विधि के साथ 3डी आईसी उत्पादन की योजना की घोषणा की थी।[79] 2011 में, एसके हाइनिक्स ने टीएसवी विधि का उपयोग करते हुए 16 GB डीडीआर3 एसडीआरएएम (40 nm क्लास) प्रस्तुत किए,[80] सैमसंग इलेक्ट्रॉनिक्स ने सितंबर में टीएसवी पर आधारित 3डी-स्टैक्ड 32 GB डीडीआर3 (30 nm क्लास) प्रस्तुत किया और फिर सैमसंग और माइक्रोन टेक्नोलॉजी ने अक्टूबर में टीएसवी आधारित हाइब्रिड मेमोरी क्यूब (एचएमसी) तकनीक की घोषणा की थी।[79]

सैमसंग, एएमडी और एसके हाइनिक्स द्वारा विकसित उच्च बैंडविड्थ मेमोरी (एचबीएम), स्टैक्ड चिप और टीएसवी का उपयोग करता है। पहली एचबीएम मेमोरी चिप 2013 में एसके हाइनिक्स द्वारा निर्मित की गई थी।[80] जनवरी 2016 में, सैमसंग इलेक्ट्रॉनिक्स ने प्रति स्टैक 8 GB तक एचबीएम2 के प्रारंभिक बड़े पैमाने पर उत्पादन की घोषणा की थी।[81][82]

2017 में, सैमसंग इलेक्ट्रॉनिक्स ने अपनी 3डी वी-नैन्ड विधि (चार्ज ट्रैप फ्लैश विधि पर आधारित) के साथ 3डी आईसी स्टैकिंग को जोड़ा, आठ स्टैक्ड 64-लेयर वी-नैन्ड चिप के साथ अपनी 512 GB KLUFG8R1EM फ्लैश मेमोरी चिप का निर्माण किया।[83] 2019 में, सैमसंग ने 16 स्टैक्ड वी-नैन्ड डाइज़ के साथ 1 TB फ्लैश चिप का उत्पादन किया।[84][85] 2018 तक, इंटेल प्रदर्शन को उत्तम बनाने के लिए 3डी आईसी के उपयोग पर विचार कर रहा है।[86] As of 2022[update], 232-लेयर नैन्ड, अर्थात् मेमोरी उपकरण, चिप माइक्रोन द्वारा बनाई गई हैं,[87] जो पहले अप्रैल 2019 में 96-लेयर चिप बना रही थीं; और तोशिबा ने 2018 में 96-लेयर उपकरण बनाए।

यह भी देखें

- चार्ज ट्रैप फ्लैश (सीटीएफ)

- फिनफेट (3डी ट्रांजिस्टर)

- एमओएसएफईटी

- मल्टीगेट उपकरण (मुगफेट)

- वी-नैन्ड (3डी नैन्ड)

टिप्पणियाँ

- ↑ "सेमि.ऑर्ग" (PDF). Archived (PDF) from the original on 2015-09-24.

- ↑ "What is 3D Integration? - 3D InCites". Archived from the original on 2014-12-30.

- ↑ Jump up to: 3.0 3.1 3.2 3.3 J. Knechtel, O. Sinanoglu, I. M. Elfadel, J. Lienig, C. C. N. Sze, "Large-Scale 3D Chips: Challenges and Solutions for Design Automation, Testing, and Trustworthy Integration" Archived 2017-08-07 at the Wayback Machine, in IPSJ Transactions on System LSI Design Methodology, vol. 10, pp. 45–62, Aug. 2017

- ↑ "INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS 2011 EDITION" (PDF). Archived from the original (PDF) on 2014-12-30. Retrieved 2014-12-30.

- ↑ "Comparing Samsung's 3D NAND with Traditional 3D ICs". 2013-08-16.

- ↑ Jump up to: 6.0 6.1 6.2 6.3 James, Dick (2014). "3D ICs in the real world". 25th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC 2014): 113–119. doi:10.1109/ASMC.2014.6846988. ISBN 978-1-4799-3944-2. S2CID 42565898.

- ↑ "Samsung starts production of 3D DDR4 DRAM modules". 2014-08-27. Archived from the original on 2014-12-31.

- ↑ Michallet, Jean-Eric. "CoolCube™: A True 3DVLSI Alternative to Scaling". www.3DInCites.com. Archived from the original on January 22, 2016. Retrieved March 24, 2014.

- ↑ von Trapp, Francoise (2015-03-16). "Monolithic 3D IC Heats Up at DATE 2015". 3D InCites. 3D InCites. Archived from the original on April 2, 2015. Retrieved March 16, 2015.

- ↑ Maestre Caro, A.; Travaly, Y.; Maes, G.; Borghs, G.; Armini, S. (2011). "Enabling Cu-Cu connection in (Dual) damascene interconnects by selective deposition of two different SAM molecules". 2011 IEEE International Interconnect Technology Conference. pp. 1–3. doi:10.1109/IITC.2011.5940263. ISBN 978-1-4577-0503-8. S2CID 30235970.

- ↑ Jump up to: 11.0 11.1 11.2 11.3 11.4 Reif, Rafael; Tan, Chuan Seng; Fan, Andy; Chen, Kuan-Neng; Das, Shamik; Checka, Nisha (2002). "3-D Interconnects Using Cu Wafer Bonding: Technology and Applications" (PDF). Advanced Metallization Conference: 37–44. S2CID 2514964. Archived from the original (PDF) on 15 July 2019. Retrieved 15 July 2019.

- ↑ Real World Technologies. "3D Integration: A Revolution in Design". May 2, 2007. "3D Integration: A Revolution in Design". Archived from the original on 2010-12-22. Retrieved 2011-03-18.

- ↑ Chen, D.Y.; Chiou, W.C.; Chen, M.F.; Wang, T.D.; Ching, K.M.; Tu, H.J.; Wu, W.J.; Yu, C.L.; Yang, K.F.; Chang, H.B.; Tseng, M.H.; Hsiao, C.W.; Lu, Y.J.; Hu, H.P.; Lin, Y.C.; Hsu, C.S.; Shue, Winston S.; Yu, C.H. (2009). "Enabling 3D-IC foundry technologies for 28 nm node and beyond: through-silicon-via integration with high throughput die-to-wafer stacking". 2009 IEEE International Electron Devices Meeting (IEDM). pp. 1–4. doi:10.1109/IEDM.2009.5424350. ISBN 978-1-4244-5639-0. S2CID 35980364.

- ↑ Developer, Shed. "3D Processors, Stacking Core". September 20, 2005. "3D Processors, Stacking Cores". Archived from the original on 2012-03-16. Retrieved 2012-10-29.,

- ↑ Developer, Shed. "3D Processors, Stacking Core". September 20, 2005. "Page 2 - 3D Processors, Stacking Cores". Archived from the original on 2011-07-09. Retrieved 2011-02-24.

- ↑ Xiangyu Dong and Yuan Xie, "System-level Cost Analysis and Design Exploration for 3D ICs", Proc. of Asia and South Pacific Design Automation Conference, 2009, "Yuan Xie's 3D IC Research Page". Archived from the original on 2010-04-24. Retrieved 2010-05-20.

- ↑ "3D IC Technology Delivers The Total Package" "3D IC Technology Delivers the Total Package". Archived from the original on 2010-10-31. Retrieved 2011-01-27. Electronic Design July 02, 2010

- ↑ James J-Q Lu, Ken Rose, & Susan Vitkavage "3D Integration: Why, What, Who, When?" "3D Integration: Why, What, Who, When?". Archived from the original on 2008-02-12. Retrieved 2008-01-22. Future Fab Intl. Volume 23, 2007

- ↑ William J. Dally, "Future Directions for On-Chip Interconnection Networks" page 17, "Archived copy" (PDF). Archived (PDF) from the original on 2010-06-12. Retrieved 2008-01-22.

{{cite web}}: CS1 maint: archived copy as title (link) Computer Systems Laboratory Stanford University, 2006 - ↑ Johnson, R Colin. "3-D chip stacks standardized". July 10, 2008. "3-D chip stacks standardized". Archived from the original on 2012-09-30. Retrieved 2014-05-15.

- ↑ "3D-ICs and Integrated Circuit Security" "Archived copy" (PDF). Archived (PDF) from the original on 2008-09-07. Retrieved 2008-02-08.

{{cite web}}: CS1 maint: archived copy as title (link) Tezzaron Semiconductor, 2008 - ↑ Dong Hyuk Woo, Nak Hee Seong, Dean L. Lewis, and Hsien-Hsin S. Lee. "An Optimized 3D-Stacked Memory Architecture by Exploiting Excessive, High-Density TSV Bandwidth". In Proceedings of the 16th International Symposium on High-Performance Computer Architecture, pp. 429–440, Bangalore, India, January 2010.

- ↑ "Predicting the Performance of a 3D Processor-Memory Chip Stack" Jacob, P., McDonald, J.F. et al.Design & Test of Computers, IEEE Volume 22, Issue 6, Nov.–Dec. 2005 Page(s):540–547

- ↑ A. Palesko, The Cost of 3D ICs, 3D InCites Knowledge Portal, January 9, 2015 "The Cost of 3D ICs". 2015-01-09. Archived from the original on 2015-01-09. Retrieved 2015-01-09.

- ↑ MazikMedia, Inc, publisher, sites maintained by jamagination (www.jamagination.com). "Robert Patti, "Impact of Wafer-Level 3D Stacking on the Yield of ICs". Future Fab Intl. Volume 23, 2007". Future-fab.com. Archived from the original on 2014-05-17. Retrieved 2014-05-15.

{{cite web}}: CS1 maint: multiple names: authors list (link) - ↑ Jump up to: 26.0 26.1 Hsien-Hsin S. Lee and Krishnendu Chakrabarty, "Test challenges for 3D integrated circuits", IEEE Design and Test of Computers, Special issue on 3D IC Design and Test, vol. 26, no. 5, pp. 26–35, Sep/Oct 2009

- ↑ ""EDA's big three unready for 3D chip packaging". EE Times Asia, October 25, 2007". Eetasia.com. Archived from the original on July 18, 2008. Retrieved 2014-05-15.

- ↑ Jump up to: 28.0 28.1 28.2 28.3 D. H. Kim, S. Mukhopadhyay, S. K. Lim, "Through-silicon-via aware interconnect prediction and optimization for 3D stacked ICs", in Proc. of Int. Workshop Sys.-Level Interconn. Pred., 2009, pp. 85–92.

- ↑ Jump up to: 29.0 29.1 S. Borkar, "3D integration for energy efficient system design", in Proc. Design Autom. Conf., 2011, pp. 214–219.

- ↑ ""3-D chip stacks standardized". EE Times November 7, 2008". Eetimes.com. 2014-05-09. Archived from the original on September 30, 2012. Retrieved 2014-05-15.

- ↑ ""SEMI International Standards Program Forms 3D Stacked IC Standards Committee". SEMI press release December 7, 2010". Semi.org. 2010-12-07. Archived from the original on May 17, 2014. Retrieved 2014-05-15.

- ↑ ""ADVANCED PACKAGING: 3D TSV Technologies Scenarios: Via First or Via Last? 2010 report". Yole report, 2010". I-micronews.com. 2010-01-01. Archived from the original on 2014-05-17. Retrieved 2014-05-15.

- ↑ "Si, glass interposers for 3D packaging: analysts' takes". Advanced Packaging August 10, 2010 Archived March 14, 2011, at the Wayback Machine

- ↑ Jump up to: 34.0 34.1 J. Knechtel, I. L. Markov, J. Lienig, "Assembling 2D Blocks into 3D Chips" Archived 2016-03-04 at the Wayback Machine, in IEEE Trans. on CAD of ICs and Systems, vol. 31, no. 2, pp. 228–241, Feb. 2012

- ↑ S. Garg, D. Marculescu, "3D-GCP: An analytical model for the impact of process variations on the critical path delay distribution of 3D ICs", in Proc. Int. Symp. Quality Electron. Des., 2009, pp. 147–155

- ↑ L. K. Scheffer, "CAD implications of new interconnect technologies", in Proc. Design Autom. Conf., 2007, pp. 576–581.

- ↑ Moskowitz, Sanford L. (2016). Advanced Materials Innovation: Managing Global Technology in the 21st century. John Wiley & Sons. pp. 165–167. ISBN 9780470508923.

- ↑ U.S. Patent 3,613,226

- ↑ U.S. Patent 3,651,490

- ↑ "A Look At Trishul: Arm's First High-Density 3D Logic Stacked Test-Chip". WikiChip Fuse (in English). 2021-06-11. Retrieved 2022-10-05.

- ↑ Lobo, Savia (2018-12-13). "Intel unveils the first 3D Logic Chip packaging technology, 'Foveros', powering its new 10nm chips, 'Sunny Cove'". Packt Hub (in English). Retrieved 2022-10-05.

- ↑ Jump up to: 42.0 42.1 42.2 42.3 42.4 42.5 42.6 Kada, Morihiro (2015). "Research and Development History of Three-Dimensional Integration Technology" (PDF). Three-Dimensional Integration of Semiconductors: Processing, Materials, and Applications. Springer. pp. 8–13. ISBN 9783319186757. Archived from the original (PDF) on 2021-10-23. Retrieved 2019-07-19.

- ↑ Kawamura, S.; Sasaki, Nobuo; Iwai, T.; Nakano, M.; Takagi, M. (October 1983). "त्रि-आयामी सीएमओएस आईसी का बीम पुन: क्रिस्टलीकरण का उपयोग करके बनाया गया है". IEEE Electron Device Letters. 4 (10): 366–368. Bibcode:1983IEDL....4..366K. doi:10.1109/EDL.1983.25766. ISSN 0741-3106. S2CID 35184408.

- ↑ Kawamura, S.; Sasaki, N.; Iwai, T.; Mukai, R.; Nakano, M.; Takagi, M. (December 1983). "3-Dimensional SOI/CMOS IC's fabricated by beam recrystallization". 1983 International Electron Devices Meeting: 364–367. doi:10.1109/IEDM.1983.190517. S2CID 11689645.

- ↑ Kawamura, S.; Sasaki, Nobuo; Iwai, T.; Mukai, R.; Nakano, M.; Takagi, M. (1984). "3-Dimensional Gate Array with Vertically Stacked Dual SOI/CMOS Structure Fabricated by Beam Recrystallization". 1984 Symposium on VLSI Technology. Digest of Technical Papers: 44–45.

- ↑ Jump up to: 46.0 46.1 46.2 Garrou, Philip (6 August 2008). "Introduction to 3D Integration" (PDF). Handbook of 3D Integration: Technology and Applications of 3D Integrated Circuits. Wiley-VCH. p. 4. doi:10.1002/9783527623051.ch1. ISBN 9783527623051.

- ↑ Akasaka, Yoichi; Nishimura, T. (December 1986). "Concept and basic technologies for 3-D IC structure". 1986 International Electron Devices Meeting: 488–491. doi:10.1109/IEDM.1986.191227. S2CID 10393330.

- ↑ Nishimura, T.; Inoue, Yasuo; Sugahara, K.; Kusunoki, S.; Kumamoto, T.; Nakagawa, S.; Nakaya, M.; Horiba, Yasutaka; Akasaka, Yoichi (December 1987). "उच्च प्रदर्शन छवि सिग्नल प्रोसेसर के लिए तीन आयामी आईसी". 1987 International Electron Devices Meeting: 111–114. doi:10.1109/IEDM.1987.191362. S2CID 12936958.

- ↑ Hayashi, Yoshihiro; Kunio, T.; Oyama, K.; Morimoto, M. (December 1989). "तीन आयामी आईसी, चार स्टैक्ड सक्रिय डिवाइस परतें हैं". International Technical Digest on Electron Devices Meeting: 837–840. doi:10.1109/IEDM.1989.74183. S2CID 113995937.

- ↑ Yamazaki, K.; Itoh, Y.; Wada, A.; Morimoto, K.; Tomita, Y. (December 1990). "4-layer 3-D IC technologies for parallel signal processing". International Technical Digest on Electron Devices: 599–602. doi:10.1109/IEDM.1990.237127. S2CID 114856400.

- ↑ Hayashi, Yoshihiro; Wada, S.; Kajiyana, K.; Oyama, K.; Koh, R.; Takahashi, S.; Kunio, T. (1990). "'संचयी रूप से बंधी हुई आईसी' (क्यूबिक) तकनीक का उपयोग करके त्रि-आयामी आईसी का निर्माण". Digest of Technical Papers.1990 Symposium on VLSI Technology: 95–96. doi:10.1109/VLSIT.1990.111025. S2CID 27465273.

- ↑ Jump up to: 52.0 52.1 Fukushima, T.; Tanaka, T.; Koyanagi, Mitsumasa (2007). "Thermal Issues of 3D ICs" (PDF). SEMATECH. Tohoku University. Archived from the original (PDF) on 16 May 2017. Retrieved 16 May 2017.

- ↑ Tanaka, Tetsu; Lee, Kang Wook; Fukushima, Takafumi; Koyanagi, Mitsumasa (2011). "3D Integration Technology and Heterogeneous Integration". S2CID 62780117. Retrieved 19 July 2019 – via Semantic Scholar.

{{cite journal}}: Cite journal requires|journal=(help) - ↑ Takahashi, Kenji; Tanida, Kazumasa (2011). "Vertical Interconnection by ASET". Handbook of 3D Integration, Volume 1: Technology and Applications of 3D Integrated Circuits. John Wiley & Sons. p. 339. ISBN 9783527623068.

- ↑ Savastionk, S.; Siniaguine, O.; Korczynski, E. (2000). "Thru-silicon vias for 3D WLP". Proceedings International Symposium on Advanced Packaging Materials Processes, Properties and Interfaces (Cat. No.00TH8507): 206–207. doi:10.1109/ISAPM.2000.869271. ISBN 0-930815-59-9. S2CID 110397071.

- ↑ Lavanyashree, B.J. (August 2016). "3-Dimensional (3D) ICs: A Survey" (PDF). International Journal of Digital Application & Contemporary Research. 5 (1). Archived from the original (PDF) on 2019-03-04.

- ↑ Banerjee, Kaustav; Souri, Shukri J.; Kapur, Pawan; Saraswat, Krishna C. (2001). "3-D ICs: a novel chip design for improving deep-submicrometer interconnect performance and systems-on-chip integration". Proceedings of the IEEE. 89 (5): 602–633. doi:10.1109/5.929647. ISSN 0018-9219.

- ↑ Garrou, Philip (6 August 2008). "Introduction to 3D Integration" (PDF). Handbook of 3D Integration: Technology and Applications of 3D Integrated Circuits. Wiley-VCH. p. 4. doi:10.1002/9783527623051.ch1. ISBN 9783527623051.

- ↑ Imoto, T.; Matsui, M.; Takubo, C.; Akejima, S.; Kariya, T.; Nishikawa, T.; Enomoto, R. (2001). "Development of 3-Dimensional Module Package, "System Block Module"". Electronic Components and Technology Conference. Institute of Electrical and Electronics Engineers (51): 552–7. ISBN 0780370384.

- ↑ Ramm, Peter (22 January 2016). "Fraunhofer EMFT: Our Early and Ongoing Work in 3D Integration". 3D InCites. Retrieved 22 September 2019.

- ↑ Ramm, P.; Bollmann, D.; Braun, R.; Buchner, R.; Cao-Minh, U.; et al. (November 1997). "लंबवत एकीकृत सर्किट के लिए तीन आयामी धातुकरण". Microelectronic Engineering. 37–38: 39–47. doi:10.1016/S0167-9317(97)00092-0. S2CID 22232571.

- ↑ Macchiolo, A.; Andricek, L.; Moser, H. G.; Nisius, R.; Richter, R. H.; Weigell, P. (1 January 2012). "ATLAS पिक्सेल अपग्रेड के लिए SLID-ICV वर्टिकल इंटीग्रेशन टेक्नोलॉजी". Physics Procedia. 37: 1009–1015. arXiv:1202.6497. Bibcode:2012PhPro..37.1009M. doi:10.1016/j.phpro.2012.02.444. ISSN 1875-3892. S2CID 91179768.

- ↑ M.B. Kleiner, S.A. Kuehn, P. Ramm, W. Weber, IEEE Transactions on Components, Packaging, and Manufacturing Technology - Part B, Vol. 19, No. 4 (1996)

- ↑ "HOME".

- ↑ Fan, Andy; Rahman, Adnan-ur; Reif, Rafael (February 2, 1999). "कॉपर वेफर बॉन्डिंग". Electrochemical and Solid-State Letters. 2 (10): 534. doi:10.1149/1.1390894. S2CID 98300746.

- ↑ "Tezzaron Semiconductor: The Z Path Forward". Tezzaron Semiconductor. Retrieved 19 July 2019.

- ↑ "Six 3D designs precede 90% power-saving claims from Tezzaron - EE Times". Archived from the original on 2014-10-31.

- ↑ Cole, Bernard. "Terrazon applies 3D stacking technology to 8051 MCU core". EETimes. Retrieved 10 August 2020.

- ↑ B. Black, D. Nelson, C. Webb, and N. Samra, "3D Processing Technology and Its Impact on iA32 Microprocessors", in Proc. of Int. Conf. on Computer Design, pp. 316–318, 2004.

- ↑ Steve Seguin (2008-09-16). "Seguin, Steve. "World's First Stacked 3D Processor Created". September 16, 2008". Tomshardware.com. Retrieved 2014-05-15.

- ↑ "Science Daily. "3-D Computer Processor: 'Rochester Cube' Points Way To More Powerful Chip Designs". September 17, 2008". Sciencedaily.com. Archived from the original on May 17, 2014. Retrieved 2014-05-15.

- ↑ 3D-MAPS project webpage at Georgia Tech "3D-MAPS Many-Core Processor". Archived from the original on 2015-03-08. Retrieved 2012-04-02.

- ↑ "Centip3De: A 64-Core, 3D Stacked, Near-Threshold System" (PDF).

- ↑ "सिस्टम-इन-पैकेज (SiP)". Toshiba. Archived from the original on 3 April 2010. Retrieved 3 April 2010.

- ↑ "तोशिबा ने मोबाइल उपभोक्ता उत्पादों के लिए उद्योग की उच्चतम क्षमता वाली एंबेडेड नंद फ्लैश मेमोरी का वाणिज्यीकरण किया". Toshiba. April 17, 2007. Archived from the original on November 23, 2010. Retrieved 23 November 2010.

- ↑ "हाइनिक्स ने नंद चिप उद्योग को चौंका दिया". Korea Times. 5 September 2007. Retrieved 8 July 2019.

- ↑ "तोशिबा ने सबसे बड़ा डेंसिटी एंबेडेड एनएएनडी फ्लैश मेमोरी डिवाइस पेश किया". Toshiba. 7 August 2008. Retrieved 21 June 2019.

- ↑ "तोशिबा ने उद्योग का सबसे बड़ा एंबेडेड नंद फ्लैश मेमोरी मॉड्यूल लॉन्च किया". Toshiba. 17 June 2010. Retrieved 21 June 2019.

- ↑ Jump up to: 79.0 79.1 79.2 Kada, Morihiro (2015). "Research and Development History of Three-Dimensional Integration Technology". Three-Dimensional Integration of Semiconductors: Processing, Materials, and Applications. Springer. pp. 15–8. ISBN 9783319186757.

- ↑ Jump up to: 80.0 80.1 "History: 2010s". SK Hynix. Archived from the original on 17 May 2021. Retrieved 8 July 2019.

- ↑ "Samsung Begins Mass Producing World's Fastest DRAM – Based on Newest High Bandwidth Memory (HBM) Interface". news.samsung.com.

- ↑ Hruska, Joel (19 January 2016). "Samsung announces mass production of next-generation HBM2 memory – ExtremeTech". Extremetech.

- ↑ Shilov, Anton (December 5, 2017). "Samsung Starts Production of 512 GB UFS NAND Flash Memory: 64-Layer V-NAND, 860 MB/s Reads". AnandTech. Retrieved 23 June 2019.

- ↑ Manners, David (30 January 2019). "सैमसंग 1TB फ्लैश eUFS मॉड्यूल बनाता है". Electronics Weekly. Retrieved 23 June 2019.

- ↑ Tallis, Billy (October 17, 2018). "Samsung Shares SSD Roadmap for QLC NAND And 96-layer 3D NAND". AnandTech. Retrieved 27 June 2019.

- ↑ "Intel unveils a groundbreaking way to make 3D chips". Engadget.

- ↑ Smith, Ryan. "Micron's 232 Layer NAND Now Shipping: 1Tbit, 6-Plane Dies With 50% More I/O Bandwidth". www.anandtech.com. Retrieved 2022-08-03.

संदर्भ

- JEDECが「DDR4」とTSVを使う「3DS」メモリ技術の概要を明らかに - 後藤弘茂のWeekly海外ニュース Impress Watch Co. (issued:2011-11-08, 2011-11-08)

- 貫通電極を用いたチップ積層技術の開発 (Japanese) – oki technical review #211 Vol.74 #3 (issued:2007-10, 2011-11-08)

- TSV (Through Silicon Via:Si貫通電極) (Japanese) – Akita Elpida Memory, inc (2011-11-08)

अग्रिम पठन

- Philip Garrou, Christopher Bower, Peter Ramm: Handbook of 3D Integration, Technology and Applications of 3D Integrated Circuits Vol. 1 and Vol. 2, Wiley-VCH, Weinheim 2008, ISBN 978-3-527-32034-9.

- Yuan Xie, Jason Cong, Sachin Sapatnekar: Three-Dimensional Integrated Circuit Design: Eda, Design And Microarchitectures, Publisher: Springer, ISBN 1-4419-0783-1, ISBN 978-1-4419-0783-7, 978-1441907837, Publishing Date: Dec. 2009.

- Philip Garrou, Mitsumasa Koyanagi, Peter Ramm: Handbook of 3D Integration, 3D Process Technology Vol. 3, Wiley-VCH, Weinheim 2014, ISBN 978-3-527-33466-7.

- Paul D. Franzon, Erik Jan Marinissen, Muhannad S. Bakir, Philip Garrou, Mitsumasa Koyanagi, Peter Ramm: Handbook of 3D Integration: "Design, Test, and Thermal Management of 3D Integrated Circuits", Vol. 4, Wiley-VCH, Weinheim 2019, ISBN 978-3-527-33855-9.

बाहरी संबंध

- Euronymous (2007-05-02). "3D Integration: A Revolution in Design". Real World Technologies. Retrieved 2014-05-15.

- Semiconductors (2006). "Mapping progress in 3D IC integration". Solid State Technology. Retrieved 2014-05-15.[permanent dead link]

- Peter Ramm; et al. (2010-09-16). "3D Integration Technology: Status and Application Development". 2010 Proceedings of ESSCIRC. IEEE. pp. 9–16. doi:10.1109/ESSCIRC.2010.5619857. hdl:11250/2463188. ISBN 978-1-4244-6664-1. S2CID 1239311.

- Mingjie Lin; Abbas El Gamal; Yi-chang Lu & Simon Wong (2006-02-22). "Performance Benefits of Monolithically Stacked 3D-FPGA (invited)". IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. Portal.acm.org. 26 (2): 113. doi:10.1145/1117201.1117219. ISBN 978-1595932921. S2CID 7818893.

- "Joint Project for Mechanical Qualification of Next Generation High Density Package-on-Package (PoP) with Through Mold Via Technology". Retrieved 2014-05-15.[permanent dead link]

- "Advancements in Stacked Chip Scale Packaging (S-CSP), Provides System-in-a-Package Functionality for Wireless and Handheld Applications". Retrieved 2014-05-15.[permanent dead link]

- Smith, Lee (July 6, 2010). "Achieving the 3rd Generation From 3D Packaging to 3D IC Architectures". Future Fab International. Amkor Technology. Retrieved 2014-05-15.[permanent dead link]

- "Factors Affecting Electromigration and Current Carrying Capacity of Flip Chip and 3D IC Interconnects". Retrieved 2014-05-15.[permanent dead link]

- "Evaluation for UV Laser Dicing Process and its Reliability for Various Designs of Stack Chip Scale Package". Retrieved 2014-05-15.[permanent dead link]

- "High Density PoP (Package-on-Package) and Package Stacking Development". Retrieved 2014-05-15.[permanent dead link]

- "3D Interconnect Technology Coming to Light". EDN. 2004. Archived from the original on 2008-12-03. Retrieved 2008-01-22.

- "Three-dimensional SoCs perform for future". EE Design. 2003. Retrieved 2014-05-15.

- "MagnaChip, Tezzaron form partnership for 3D chips". EE Times. 2004. Archived from the original on 2013-01-21.

- "Matrix preps 64-Mbyte write-once memory". EE Times. 2001. Archived from the original on 2008-05-15. Retrieved 2014-05-15.

- "Samsung starts mass producing first 3D vertical NAND flash, August 2013". Electroiq.com. 2013-08-06. Archived from the original on 2013-08-18. Retrieved 2014-05-15.

- "CEA Leti placed monolithic 3D as the next generation technology as alternative to dimension scaling, August 2013". Electroiq.com. Archived from the original on 2013-08-19. Retrieved 2014-05-15.

- "3D integration: A status report". 2009. Archived from the original on 2013-01-22. Retrieved 2011-01-21.

- Deepak C. Sekar & Zvi Or-Bach. "Monolithic 3D-ICs with Single Crystal Silicon Layers" (PDF). Retrieved 2014-05-15.

- "Global 3D Chips/3D IC Market to Reach US$5.2 Billion by 2015". PRWeb. 2010. Retrieved 2014-05-15.

- "Samsung Develops 30nm-class 32GB Green DDR3 for Next-generation Servers, Using TSV Package Technology". Samsung.com. 2011. Retrieved 2014-05-15.

- "How Might 3-D ICs Come Together?". Semiconductor International. 2008. Archived from the original on 2010-03-04. Retrieved 2009-06-11.

- "Three-Dimensional ICs Solve the Interconnect Paradox". Semiconductor International. 2005. Archived from the original on 2008-02-12. Retrieved 2008-01-22.

- "Ziptronix, Raytheon Prove 3-D Integration of 0.5 µm CMOS Device". Semiconductor International. 2007. Archived from the original on 2007-11-06. Retrieved 2008-01-22.

- Peter Ramm; Armin Klumpp; Josef Weber; Maaike Taklo (2010). "3D System-on-Chip Technologies for More than Moore Systems". Journal of Microsystem Technologies. Springerlink.com. 16 (7): 1051–1055. doi:10.1007/s00542-009-0976-1. S2CID 55824967.

- Philip Garrou, James Lu & Peter Ramm (2012). "Chapter 15". Three-Dimensional Integration. Retrieved 2014-05-15.

{{cite book}}:|work=ignored (help)