अनुप्रयोग-विशिष्ट एकीकृत परिपथ: Difference between revisions

No edit summary |

No edit summary |

||

| Line 3: | Line 3: | ||

{{More footnotes|date=October 2015}} | {{More footnotes|date=October 2015}} | ||

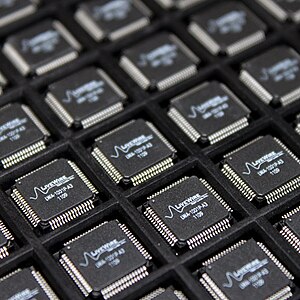

[[File:SSDTR-ASIC technology.jpg|thumb|अनुप्रयोग-विशिष्ट एकीकृत सर्किट (ASIC) चिप्स की एक ट्रे]] | [[File:SSDTR-ASIC technology.jpg|thumb|अनुप्रयोग-विशिष्ट एकीकृत सर्किट (एएसआईसी (ASIC)) चिप्स की एक ट्रे]] | ||

एक एप्लिकेशन-विशिष्ट एकीकृत सर्किट (एएसआईसी) एक एकीकृत सर्किट (आईसी) चिप है जिसे सामान्य प्रयोजन के उपयोग के बजाय किसी विशेष उपयोग के लिए अनुकूलित किया जाता है।उदाहरण के लिए, डिजिटल वॉयस रिकॉर्डर या उच्च दक्षता वाले वीडियो कोडेक (जैसे एएमडी वीसीई) में चलने के लिए डिज़ाइन की गई चिप एक एएसआईसी है। यह 7400 श्रृंखला या 4000 श्रृंखला की तरह है।<ref name=":0">{{Cite book|title=ASIC Design in the Silicon Sandbox: A Complete Guide to Building Mixed-signal Integrated Circuits|last=Barr|first=Keith|date=2007|publisher=McGraw-Hill|isbn=978-0-07-148161-8|location=New York|oclc=76935560}}</ref> ASIC चिप्स आमतौर पर मेटल ऑक्साइड सेमीकंडक्टर (MOS) तकनीक का उपयोग करके बनाए जाते हैं, उदाहरण के लिए एमओएस एकीकृत सर्किट चिप्स के रूप में। <ref name="computerhistory1967"/> | एक एप्लिकेशन-'''विशिष्ट एकीकृत सर्किट (एएसआईसी)''' एक एकीकृत सर्किट (आईसी) चिप है जिसे सामान्य प्रयोजन के उपयोग के बजाय किसी विशेष उपयोग के लिए अनुकूलित किया जाता है।उदाहरण के लिए, डिजिटल वॉयस रिकॉर्डर या उच्च दक्षता वाले वीडियो कोडेक (जैसे एएमडी वीसीई) में चलने के लिए डिज़ाइन की गई चिप एक एएसआईसी है। यह 7400 श्रृंखला या 4000 श्रृंखला की तरह है।<ref name=":0">{{Cite book|title=ASIC Design in the Silicon Sandbox: A Complete Guide to Building Mixed-signal Integrated Circuits|last=Barr|first=Keith|date=2007|publisher=McGraw-Hill|isbn=978-0-07-148161-8|location=New York|oclc=76935560}}</ref> एएसआईसी (ASIC) चिप्स आमतौर पर मेटल ऑक्साइड सेमीकंडक्टर एसओएस (MOS) तकनीक का उपयोग करके बनाए जाते हैं, उदाहरण के लिए एमओएस एकीकृत सर्किट चिप्स के रूप में। <ref name="computerhistory1967"/> | ||

जैसे-जैसे फीचर आकार सिकुड़ते गए हैं और डिज़ाइन टूल में वर्षों में सुधार हुआ है, ASIC में संभव अधिकतम जटिलता (और इसलिए कार्यक्षमता) 5,000 लॉजिक गेट्स से बढ़कर 100 मिलियन से अधिक हो गई है। आधुनिक ASIC में अक्सर संपूर्ण माइक्रोप्रोसेसर, ROM, RAM, EEPROM, फ्लैश मेमोरी और अन्य बड़े बिल्डिंग ब्लॉक सहित मेमोरी ब्लॉक शामिल होते हैं। ऐसे ASIC को अक्सर SoC (सिस्टम-ऑन-चिप) कहा जाता है। डिजिटल ASIC के डिजाइनर अक्सर एक हार्डवेयर विवरण भाषा (HDL) का उपयोग करते हैं, जैसे वेरिलोग या वीएचडीएल, एएसआईसी की कार्यक्षमता का वर्णन करने के लिए<ref name=":0" /> | जैसे-जैसे फीचर आकार सिकुड़ते गए हैं और डिज़ाइन टूल में वर्षों में सुधार हुआ है, एएसआईसी (ASIC) में संभव अधिकतम जटिलता (और इसलिए कार्यक्षमता) 5,000 लॉजिक गेट्स से बढ़कर 100 मिलियन से अधिक हो गई है। आधुनिक एएसआईसी (ASIC) में अक्सर संपूर्ण माइक्रोप्रोसेसर, '''रोम (ROM) , रैम (RAM), ईईपीरोम (EEPROM)''', फ्लैश मेमोरी और अन्य बड़े बिल्डिंग ब्लॉक सहित मेमोरी ब्लॉक शामिल होते हैं। ऐसे एएसआईसी (ASIC) को अक्सर एसओसी (SoC) (सिस्टम-ऑन-चिप) कहा जाता है। डिजिटल एएसआईसी (ASIC) के डिजाइनर अक्सर एक हार्डवेयर विवरण भाषा '''एचडीएल (HDL)''' का उपयोग करते हैं, जैसे वेरिलोग या वीएचडीएल, एएसआईसी की कार्यक्षमता का वर्णन करने के लिए<ref name=":0" /> | ||

फील्ड प्रोग्रामेबल गेट एरेज़ (FPGA) ब्रेडबोर्ड पर आधुनिक दिन प्रौद्योगिकी सुधार हैं, इसका मतलब है कि ASIC के विपरीत उन्हें एप्लिकेशन विशिष्ट नहीं बनाया गया है। प्रोग्रामेबल लॉजिक ब्लॉक और प्रोग्रामेबल इंटरकनेक्ट एक ही FPGA को कई अलग-अलग अनुप्रयोगों में उपयोग करने की अनुमति देते हैं। छोटे डिज़ाइन या कम उत्पादन मात्रा के लिए, | फील्ड प्रोग्रामेबल गेट एरेज़ '''एफपीजीए (FPGA)''' ब्रेडबोर्ड पर आधुनिक दिन प्रौद्योगिकी सुधार हैं, इसका मतलब है कि एएसआईसी (ASIC) के विपरीत उन्हें एप्लिकेशन विशिष्ट नहीं बनाया गया है। प्रोग्रामेबल लॉजिक ब्लॉक और प्रोग्रामेबल इंटरकनेक्ट एक ही एफपीजीए (FPGA) को कई अलग-अलग अनुप्रयोगों में उपयोग करने की अनुमति देते हैं। छोटे डिज़ाइन या कम उत्पादन मात्रा के लिए, एफपीजीए (FPGA)s एएसआईसी (ASIC) डिज़ाइन की तुलना में अधिक लागत प्रभावी हो सकते हैं, यहाँ तक कि उत्पादन में भी। एएसआईसी (ASIC) की गैर-आवर्ती इंजीनियरिंग (NRE) लागत लाखों डॉलर में चल सकती है। इसलिए, डिवाइस निर्माता आमतौर पर प्रोटोटाइप और कम उत्पादन मात्रा वाले उपकरणों के लिए एफपीजीए (FPGA)s पसंद करते हैं और एएसआईसी बहुत बड़े उत्पादन संस्करणों के लिए जहां एनआरई लागत को कई उपकरणों में परिशोधित किया जा सकता है। | ||

== इतिहास == | == इतिहास == | ||

प्रारंभिक | प्रारंभिक एएसआईसी (ASIC)s ने गेट ऐरे तकनीक का उपयोग किया। 1967 तक, फेरांति और इंटरडिजाइन प्रारंभिक द्विध्रुवी गेट सरणियों का निर्माण कर रहे थे। 1967 में, फेयरचाइल्ड सेमीकंडक्टर ने द्विध्रुवी '''डायोड-ट्रांजिस्टर लॉजिक डीटीएल (DTL)''' और '''ट्रांजिस्टर-ट्रांजिस्टर लॉजिक टीटीएल (TTL)''' सरणियों के माइक्रोमैट्रिक्स परिवार की शुरुआत की।<ref name="computerhistory1967">{{cite web |title=1967: Application Specific Integrated Circuits employ Computer-Aided Design |url=https://www.computerhistory.org/siliconengine/application-specific-integrated-circuits-employ-computer-aided-design/ |website=The Silicon Engine |publisher=[[Computer History Museum]] |access-date=9 November 2019}}</ref> | ||

पूरक धातु ऑक्साइड सेमीकंडक्टर (CMOS) तकनीक ने गेट सरणियों के व्यापक व्यावसायीकरण का द्वार खोल दिया। पहला CMOS गेट सरणियाँ रॉबर्ट लिप द्वारा 1974 में International Microcircuits, Inc. (IMI)<ref name="computerhistory1967" /> के लिए विकसित किया गया था।<ref>{{Cite book|url=http://www.computerhistory.org/collections/catalog/102706880|title=Lipp, Bob oral history|website=[[Computer History Museum]]|date=14 February 2017|publisher=Computer History Museum|access-date=2018-01-28}}</ref><ref>{{Cite web|url=http://www.computerhistory.org/siliconengine/people/|title=People|website=The Silicon Engine|publisher=Computer History Museum|access-date=2018-01-28}}</ref> | '''पूरक धातु ऑक्साइड सेमीकंडक्टर सीएमओएस (CMOS)''' तकनीक ने गेट सरणियों के व्यापक व्यावसायीकरण का द्वार खोल दिया। पहला सीएमओएस (CMOS) गेट सरणियाँ रॉबर्ट लिप द्वारा 1974 में इंटरनेशनल माइक्रोसर्किट इंक. (International Microcircuits, Inc. (IMI))<ref name="computerhistory1967" /> के लिए विकसित किया गया था।<ref>{{Cite book|url=http://www.computerhistory.org/collections/catalog/102706880|title=Lipp, Bob oral history|website=[[Computer History Museum]]|date=14 February 2017|publisher=Computer History Museum|access-date=2018-01-28}}</ref><ref>{{Cite web|url=http://www.computerhistory.org/siliconengine/people/|title=People|website=The Silicon Engine|publisher=Computer History Museum|access-date=2018-01-28}}</ref> | ||

मेटल ऑक्साइड सेमीकंडक्टर (MOS) मानक सेल तकनीक फेयरचाइल्ड और मोटोरोला द्वारा पेश की गई थी, जो 1970 के दशक में व्यापार नाम माइक्रोमोसाइक और पॉलीसेल के तहत है। इस तकनीक का बाद में वीएलएसआई टेक्नोलॉजी (1979 में स्थापित) और एलएसआई लॉजिक (1981) द्वारा सफलतापूर्वक व्यावसायीकरण किया गया।<ref name="computerhistory1967" /> | '''मेटल ऑक्साइड सेमीकंडक्टर एमओएस (MOS)''' मानक सेल तकनीक फेयरचाइल्ड और मोटोरोला द्वारा पेश की गई थी, जो 1970 के दशक में व्यापार नाम माइक्रोमोसाइक और पॉलीसेल के तहत है। इस तकनीक का बाद में वीएलएसआई टेक्नोलॉजी (1979 में स्थापित) और '''एलएसआई (LSI)''' लॉजिक (1981) द्वारा सफलतापूर्वक व्यावसायीकरण किया गया।<ref name="computerhistory1967" /> | ||

गेट एरे सर्किट्री का एक सफल व्यावसायिक अनुप्रयोग जो 1981 और 1982 में पेश किए गए लो एंड 8 बिट | गेट एरे सर्किट्री का एक सफल व्यावसायिक अनुप्रयोग जो 1981 और 1982 में पेश किए गए लो एंड 8 बिट जेड एक्स (ZX) 81 और जेड एक्स (ZX) स्पेक्ट्रम पर्सनल कंप्यूटर में पाया गया था। इनका उपयोग सिनक्लेयर रिसर्च (यूके) द्वारा अनिवार्य रूप से कम लागत वाले इनपुट आउटपुट समाधान के रूप में किया गया था जिसका उद्देश्य कंप्यूटर के ग्राफिक्स को संभालना था। | ||

मेटल इंटरकनेक्ट मास्क को बदलकर अनुकूलन हुआ। गेट सरणियों में कुछ हज़ार फाटकों तक की जटिलताएँ थीं; इसे अब मिड स्केल इंटीग्रेशन कहा जाता है। बाद के संस्करण अधिक सामान्यीकृत हो गए, धातु और पॉलीसिलिकॉन दोनों परतों द्वारा अनुकूलित विभिन्न आधार मर जाते हैं। कुछ बेस डेज़ में रैंडम एक्सेस मेमोरी (RAM) तत्व भी शामिल होते हैं। | मेटल इंटरकनेक्ट मास्क को बदलकर अनुकूलन हुआ। गेट सरणियों में कुछ हज़ार फाटकों तक की जटिलताएँ थीं; इसे अब मिड स्केल इंटीग्रेशन कहा जाता है। बाद के संस्करण अधिक सामान्यीकृत हो गए, धातु और '''पॉलीसिलिकॉन''' दोनों परतों द्वारा अनुकूलित विभिन्न आधार मर जाते हैं। कुछ बेस डेज़ में रैंडम एक्सेस मेमोरी (RAM) तत्व भी शामिल होते हैं। | ||

== मानक-कोशिका डिजाइन == | == मानक-कोशिका डिजाइन == | ||

1980 के दशक के मध्य में, एक डिज़ाइनर ASIC निर्माता का चयन करेगा और निर्माता से उपलब्ध डिज़ाइन टूल का उपयोग करके उनके डिज़ाइन को लागू करेगा जबकि तृतीय पक्ष डिज़ाइन उपकरण उपलब्ध थे, तीसरे पक्ष के डिज़ाइन टूल से लेआउट के लिए कोई प्रभावी लिंक नहीं था और विभिन्न ASIC निर्माताओं की वास्तविक अर्धचालक प्रक्रिया प्रदर्शन विशेषताओं। अधिकांश डिजाइनरों ने अपने डिजाइन के कार्यान्वयन को पूरा करने के लिए कारखाने के विशिष्ट उपकरणों का इस्तेमाल किया। जो इस समस्या का समाधान है, जिससे बहुत अधिक घनत्व वाला उपकरण भी प्राप्त हुआ, और यह मानक कोशिकाओं का कार्यान्वयन था।<ref name="MichaelJohnSebastianSmith">{{cite book|author=Smith, Michael John Sebastian|title=Application-Specific Integrated Circuits|publisher=Addison-Wesley Professional|year=1997|isbn=978-0-201-50022-6}}</ref> | 1980 के दशक के मध्य में, एक डिज़ाइनर एएसआईसी (ASIC) निर्माता का चयन करेगा और निर्माता से उपलब्ध डिज़ाइन टूल का उपयोग करके उनके डिज़ाइन को लागू करेगा जबकि तृतीय पक्ष डिज़ाइन उपकरण उपलब्ध थे, तीसरे पक्ष के डिज़ाइन टूल से लेआउट के लिए कोई प्रभावी लिंक नहीं था और विभिन्न एएसआईसी (ASIC) निर्माताओं की वास्तविक अर्धचालक प्रक्रिया प्रदर्शन विशेषताओं। अधिकांश डिजाइनरों ने अपने डिजाइन के कार्यान्वयन को पूरा करने के लिए कारखाने के विशिष्ट उपकरणों का इस्तेमाल किया। जो इस समस्या का समाधान है, जिससे बहुत अधिक घनत्व वाला उपकरण भी प्राप्त हुआ, और यह '''मानक कोशिकाओं''' का कार्यान्वयन था।<ref name="MichaelJohnSebastianSmith">{{cite book|author=Smith, Michael John Sebastian|title=Application-Specific Integrated Circuits|publisher=Addison-Wesley Professional|year=1997|isbn=978-0-201-50022-6}}</ref> | ||

प्रत्येक ASIC निर्माता ज्ञात विद्युत विशेषताओं के साथ कार्यात्मक ब्लॉक बना सकता है, जैसे प्रसार विलंब, समाई और अधिष्ठापन, जिसे तृतीय पक्ष टूल में भी प्रदर्शित किया जा सकता है। मानक सेल डिजाइन बहुत उच्च गेट घनत्व और अच्छे विद्युत प्रदर्शन को प्राप्त करने के लिए इन कार्यात्मक ब्लॉकों का उपयोग है। मानक सेल डिज़ाइन {{Section link||गेट सरणी और अर्ध कस्टम डिज़ाइन (Gate-array and semi-custom design)|nopage=y}} और {{Section link||पूर्ण कस्टम डिज़ाइन (Full-custom design)|nopage=y}} के बीच इसकी गैर-आवर्ती इंजीनियरिंग और आवर्ती घटक लागत के साथ-साथ प्रदर्शन और विकास की गति (बाजार में समय सहित) के बीच मध्यवर्ती है। | प्रत्येक एएसआईसी (ASIC) निर्माता ज्ञात विद्युत विशेषताओं के साथ कार्यात्मक ब्लॉक बना सकता है, जैसे प्रसार विलंब, समाई और अधिष्ठापन, जिसे तृतीय पक्ष टूल में भी प्रदर्शित किया जा सकता है। मानक सेल डिजाइन बहुत उच्च गेट घनत्व और अच्छे विद्युत प्रदर्शन को प्राप्त करने के लिए इन कार्यात्मक ब्लॉकों का उपयोग है। मानक सेल डिज़ाइन {{Section link||गेट सरणी और अर्ध कस्टम डिज़ाइन (Gate-array and semi-custom design)|nopage=y}} और {{Section link||पूर्ण कस्टम डिज़ाइन (Full-custom design)|nopage=y}} के बीच इसकी गैर-आवर्ती इंजीनियरिंग और आवर्ती घटक लागत के साथ-साथ प्रदर्शन और विकास की गति (बाजार में समय सहित) के बीच मध्यवर्ती है। | ||

1990 के दशक के अंत तक, तर्क संश्लेषण उपकरण उपलब्ध हो गए। ऐसे उपकरण एचडीएल विवरण को गेट स्तर की नेटलिस्ट में संकलित कर सकते हैं। स्टैंडर्ड सेल इंटीग्रेटेड सर्किट (ICs) को निम्नलिखित वैचारिक चरणों में डिज़ाइन किया गया है जिन्हें इलेक्ट्रॉनिक्स डिज़ाइन फ्लो कहा जाता है, हालांकि ये चरण व्यवहार में महत्वपूर्ण रूप से ओवरलैप करते हैं: | 1990 के दशक के अंत तक, तर्क संश्लेषण उपकरण उपलब्ध हो गए। ऐसे उपकरण एचडीएल विवरण को गेट स्तर की नेटलिस्ट में संकलित कर सकते हैं। स्टैंडर्ड सेल इंटीग्रेटेड सर्किट (ICs) को निम्नलिखित वैचारिक चरणों में डिज़ाइन किया गया है जिन्हें इलेक्ट्रॉनिक्स डिज़ाइन फ्लो कहा जाता है, हालांकि ये चरण व्यवहार में महत्वपूर्ण रूप से ओवरलैप करते हैं: | ||

# '''आवश्यकताएँ इंजीनियरिंग''': डिज़ाइन इंजीनियरों की एक टीम एक नए ASIC के लिए आवश्यक कार्यों की गैर-औपचारिक समझ के साथ शुरू होती है, जो आमतौर पर आवश्यकताओं के विश्लेषण से प्राप्त होता है। | # '''आवश्यकताएँ इंजीनियरिंग''': डिज़ाइन इंजीनियरों की एक टीम एक नए एएसआईसी (ASIC) के लिए आवश्यक कार्यों की गैर-औपचारिक समझ के साथ शुरू होती है, जो आमतौर पर आवश्यकताओं के विश्लेषण से प्राप्त होता है। | ||

# '''रजिस्टर-ट्रांसफर लेवल (RTL) डिज़ाइन''': डिज़ाइन टीम हार्डवेयर विवरण भाषा का उपयोग करके इन लक्ष्यों को प्राप्त करने के लिए ASIC के विवरण का निर्माण करती है। यह प्रक्रिया एक उच्च स्तरीय भाषा में कंप्यूटर प्रोग्राम लिखने के समान है। | # '''रजिस्टर-ट्रांसफर लेवल आरटीएल (RTL) डिज़ाइन''': डिज़ाइन टीम हार्डवेयर विवरण भाषा का उपयोग करके इन लक्ष्यों को प्राप्त करने के लिए एएसआईसी (ASIC) के विवरण का निर्माण करती है। यह प्रक्रिया एक उच्च स्तरीय भाषा में कंप्यूटर प्रोग्राम लिखने के समान है। | ||

# '''कार्यात्मक सत्यापन''': उद्देश्य के लिए उपयुक्तता कार्यात्मक सत्यापन द्वारा सत्यापित की जाती है। इसमें परीक्षण बेंच के माध्यम से तर्क अनुकरण, औपचारिक सत्यापन, अनुकरण, या सिमिक्स के समान शुद्ध सॉफ्टवेयर मॉडल बनाने और मूल्यांकन करने जैसी तकनीकें शामिल हो सकती हैं। प्रत्येक सत्यापन तकनीक के फायदे और नुकसान हैं, और अक्सर ASIC सत्यापन के लिए कई विधियों का एक साथ उपयोग किया जाता है। अधिकांश | # '''कार्यात्मक सत्यापन''': उद्देश्य के लिए उपयुक्तता कार्यात्मक सत्यापन द्वारा सत्यापित की जाती है। इसमें परीक्षण बेंच के माध्यम से तर्क अनुकरण, औपचारिक सत्यापन, अनुकरण, या सिमिक्स के समान शुद्ध सॉफ्टवेयर मॉडल बनाने और मूल्यांकन करने जैसी तकनीकें शामिल हो सकती हैं। प्रत्येक सत्यापन तकनीक के फायदे और नुकसान हैं, और अक्सर एएसआईसी (ASIC) सत्यापन के लिए कई विधियों का एक साथ उपयोग किया जाता है। अधिकांश एफपीजीए (FPGA)s के विपरीत, एएसआईसी (ASIC) को एक बार गढ़े जाने के बाद पुन: प्रोग्राम नहीं किया जा सकता है और इसलिए एएसआईसी (ASIC) डिज़ाइन जो पूरी तरह से सही नहीं हैं, वे बहुत अधिक महंगे हैं, जिससे पूर्ण परीक्षण कवरेज की आवश्यकता बढ़ जाती है। | ||

# '''लॉजिक सिंथेसिस''': लॉजिक सिंथेसिस आरटीएल डिज़ाइन को एक बड़े संग्रह में बदल देता है जिसे निचले स्तर के निर्माण कहा जाता है जिसे मानक सेल कहा जाता है। इन निर्माणों को एक मानक सेल लाइब्रेरी से लिया गया है जिसमें विशिष्ट कार्य करने वाले लॉजिक गेट्स के पूर्व-विशिष्ट संग्रह शामिल हैं। मानक सेल आमतौर पर ASIC के नियोजित निर्माता के लिए विशिष्ट होते हैं। मानक कोशिकाओं का परिणामी संग्रह और उनके बीच आवश्यक विद्युत कनेक्शन को गेट लेवल नेटलिस्ट कहा जाता है। | # '''लॉजिक सिंथेसिस''': लॉजिक सिंथेसिस आरटीएल डिज़ाइन को एक बड़े संग्रह में बदल देता है जिसे निचले स्तर के निर्माण कहा जाता है जिसे मानक सेल कहा जाता है। इन निर्माणों को एक मानक सेल लाइब्रेरी से लिया गया है जिसमें विशिष्ट कार्य करने वाले लॉजिक गेट्स के पूर्व-विशिष्ट संग्रह शामिल हैं। मानक सेल आमतौर पर एएसआईसी (ASIC) के नियोजित निर्माता के लिए विशिष्ट होते हैं। मानक कोशिकाओं का परिणामी संग्रह और उनके बीच आवश्यक विद्युत कनेक्शन को गेट लेवल नेटलिस्ट कहा जाता है। | ||

# '''प्लेसमेंट''': गेट स्तरीय नेटलिस्ट को अगली बार प्लेसमेंट टूल द्वारा संसाधित किया जाता है जो मानक कोशिकाओं को अंतिम ASIC का प्रतिनिधित्व करने वाले एकीकृत सर्किट डाई के क्षेत्र में रखता है। प्लेसमेंट टूल मानक सेल का एक अनुकूलित प्लेसमेंट खोजने का प्रयास करता है, और यह विभिन्न निर्दिष्ट बाधाओं के अधीन है। | # '''प्लेसमेंट''': गेट स्तरीय नेटलिस्ट को अगली बार प्लेसमेंट टूल द्वारा संसाधित किया जाता है जो मानक कोशिकाओं को अंतिम एएसआईसी (ASIC) का प्रतिनिधित्व करने वाले एकीकृत सर्किट डाई के क्षेत्र में रखता है। प्लेसमेंट टूल मानक सेल का एक अनुकूलित प्लेसमेंट खोजने का प्रयास करता है, और यह विभिन्न निर्दिष्ट बाधाओं के अधीन है। | ||

# '''रूटिंग''': एक इलेक्ट्रॉनिक्स रूटिंग टूल मानक कोशिकाओं का भौतिक स्थान लेता है और उनके बीच विद्युत कनेक्शन बनाने के लिए नेटलिस्ट का उपयोग करता है। चूंकि खोज स्थान बड़ा है, इसलिए यह प्रक्रिया "विश्व स्तर पर इष्टतम" समाधान के बजाय "पर्याप्त" उत्पन्न करेगी। आउटपुट एक फाइल है जिसका उपयोग सेमीकंडक्टर फैब्रिकेशन सुविधा को सक्षम करने वाले फोटोमास्क का एक सेट बनाने के लिए किया जा सकता है, जिसे आमतौर पर भौतिक एकीकृत परिपथों के निर्माण के लिए 'फैब' या 'फाउंड्री' कहा जाता है। प्लेसमेंट और रूटिंग का आपस में गहरा संबंध है और इन्हें सामूहिक रूप से इलेक्ट्रॉनिक्स डिजाइन में स्थान और मार्ग कहा जाता है। | # '''रूटिंग''': एक इलेक्ट्रॉनिक्स रूटिंग टूल मानक कोशिकाओं का भौतिक स्थान लेता है और उनके बीच विद्युत कनेक्शन बनाने के लिए नेटलिस्ट का उपयोग करता है। चूंकि खोज स्थान बड़ा है, इसलिए यह प्रक्रिया "विश्व स्तर पर इष्टतम" समाधान के बजाय "पर्याप्त" उत्पन्न करेगी। आउटपुट एक फाइल है जिसका उपयोग सेमीकंडक्टर फैब्रिकेशन सुविधा को सक्षम करने वाले फोटोमास्क का एक सेट बनाने के लिए किया जा सकता है, जिसे आमतौर पर भौतिक एकीकृत परिपथों के निर्माण के लिए 'फैब' या 'फाउंड्री' कहा जाता है। प्लेसमेंट और रूटिंग का आपस में गहरा संबंध है और इन्हें सामूहिक रूप से इलेक्ट्रॉनिक्स डिजाइन में स्थान और मार्ग कहा जाता है। | ||

# '''साइन-ऑफ''': अंतिम लेआउट को देखते हुए, सर्किट निष्कर्षण परजीवी प्रतिरोधों और समाई की गणना करता है। डिजिटल सर्किट के मामले में, इसे फिर देरी की जानकारी में मैप किया जाएगा जिससे सर्किट प्रदर्शन का अनुमान लगाया जा सकता है, आमतौर पर स्थैतिक समय विश्लेषण द्वारा। यह, और अन्य अंतिम परीक्षण जैसे कि डिज़ाइन नियम की जाँच और शक्ति विश्लेषण को सामूहिक रूप से साइनऑफ़ कहा जाता है, यह सुनिश्चित करने के लिए है कि डिवाइस प्रक्रिया, वोल्टेज और तापमान के सभी चरम सीमाओं पर सही ढंग से कार्य करेगा। जब यह परीक्षण पूरा हो जाता है तो चिप निर्माण के लिए फोटोमास्क जानकारी जारी की जाती है। | # '''साइन-ऑफ''': अंतिम लेआउट को देखते हुए, सर्किट निष्कर्षण परजीवी प्रतिरोधों और समाई की गणना करता है। डिजिटल सर्किट के मामले में, इसे फिर देरी की जानकारी में मैप किया जाएगा जिससे सर्किट प्रदर्शन का अनुमान लगाया जा सकता है, आमतौर पर स्थैतिक समय विश्लेषण द्वारा। यह, और अन्य अंतिम परीक्षण जैसे कि डिज़ाइन नियम की जाँच और शक्ति विश्लेषण को सामूहिक रूप से साइनऑफ़ कहा जाता है, यह सुनिश्चित करने के लिए है कि डिवाइस प्रक्रिया, वोल्टेज और तापमान के सभी चरम सीमाओं पर सही ढंग से कार्य करेगा। जब यह परीक्षण पूरा हो जाता है तो चिप निर्माण के लिए फोटोमास्क जानकारी जारी की जाती है। | ||

| Line 39: | Line 39: | ||

== गेट-सरणी और अर्ध-कस्टम डिजाइन == | == गेट-सरणी और अर्ध-कस्टम डिजाइन == | ||

[[File:S-MOS Systems ASIC SLA6140.jpg|thumb|एक गेट-सरणी ASIC की माइक्रोस्कोप फोटोग्राफ पूर्वनिर्धारित तर्क कोशिकाओं और कस्टम इंटरकनेक्ट्स को दर्शाता है।यह विशेष डिज़ाइन उपलब्ध लॉजिक गेट्स के 20% से कम का उपयोग करता है।]] | [[File:S-MOS Systems ASIC SLA6140.jpg|thumb|एक गेट-सरणी एएसआईसी (ASIC) की माइक्रोस्कोप फोटोग्राफ पूर्वनिर्धारित तर्क कोशिकाओं और कस्टम इंटरकनेक्ट्स को दर्शाता है।यह विशेष डिज़ाइन उपलब्ध लॉजिक गेट्स के 20% से कम का उपयोग करता है।]] | ||

गेट ऐरे डिज़ाइन एक निर्माण विधि है जिसमें विसरित परतें, प्रत्येक में ट्रांजिस्टर होते है और अन्य सक्रिय उपकरण, पूर्वनिर्धारित हैं और इलेक्ट्रॉनिक वेफर्स युक्त है ऐसे उपकरण "स्टॉक में रखे जाते हैं" या निर्माण प्रक्रिया के धातुकरण चरण से पहले असंबद्ध होते हैं। भौतिक डिजाइन प्रक्रिया अंतिम उपकरण के लिए इन परतों के अंतर्संबंधों को परिभाषित करती है। अधिकांश ASIC निर्माताओं के लिए, इसमें दो और नौ धातु परतें होती हैं प्रत्येक परत उसके नीचे की परत के लंबवत चलती है। गैर-आवर्ती इंजीनियरिंग लागत पूर्ण कस्टम डिज़ाइन की तुलना में बहुत कम है, चूंकि फोटोलिथोग्राफिक मास्क केवल धातु की परतों के लिए आवश्यक हैं। उत्पादन चक्र बहुत कम हैं, चूंकि धातुकरण एक अपेक्षाकृत त्वरित प्रक्रिया है; जिससे बाजार के लिए समय में तेजी आ रही है। | '''गेट ऐरे डिज़ाइन''' एक निर्माण विधि है जिसमें विसरित परतें, प्रत्येक में ट्रांजिस्टर होते है और अन्य सक्रिय उपकरण, पूर्वनिर्धारित हैं और इलेक्ट्रॉनिक वेफर्स युक्त है ऐसे उपकरण "स्टॉक में रखे जाते हैं" या निर्माण प्रक्रिया के धातुकरण चरण से पहले असंबद्ध होते हैं। भौतिक डिजाइन प्रक्रिया अंतिम उपकरण के लिए इन परतों के अंतर्संबंधों को परिभाषित करती है। अधिकांश एएसआईसी (ASIC) निर्माताओं के लिए, इसमें दो और नौ धातु परतें होती हैं प्रत्येक परत उसके नीचे की परत के लंबवत चलती है। गैर-आवर्ती इंजीनियरिंग लागत पूर्ण कस्टम डिज़ाइन की तुलना में बहुत कम है, चूंकि फोटोलिथोग्राफिक मास्क केवल धातु की परतों के लिए आवश्यक हैं। उत्पादन चक्र बहुत कम हैं, चूंकि धातुकरण एक अपेक्षाकृत त्वरित प्रक्रिया है; जिससे बाजार के लिए समय में तेजी आ रही है। | ||

गेट ऐरे | गेट ऐरे एएसआईसी (ASIC)s हमेशा तेजी से डिजाइन और प्रदर्शन के बीच एक समझौता होते हैं एक निर्माता द्वारा स्टॉक वेफर के रूप में रखे जाने पर दिए गए डिज़ाइन को मैप करने के रूप में जो कभी भी 100% सर्किट उपयोग नहीं देता है। अक्सर इंटरकनेक्ट को रूट करने में कठिनाइयों के लिए बड़े एरे डिवाइस पर माइग्रेशन की आवश्यकता होती है, जिसके परिणामस्वरूप पीस पार्ट की कीमत में वृद्धि होती है। ये कठिनाइयाँ अक्सर इंटरकनेक्ट को विकसित करने के लिए उपयोग किए जाने वाले लेआउट ईडीए (EDA) सॉफ़्टवेयर का परिणाम होती हैं। | ||

शुद्ध तर्क केवल गेट सरणी डिजाइन आज सर्किट डिजाइनरों द्वारा शायद ही कभी लागू किया जाता है, इन्हें लगभग पूरी तरह से फील्ड प्रोग्राम करने योग्य उपकरणों द्वारा बदल दिया गया है। ऐसे उपकरणों में सबसे प्रमुख हैं फील्ड प्रोग्रामेबल गेट एरेज़ (FPGAs) जिसे उपयोगकर्ता द्वारा प्रोग्राम किया जा सकता है और इस प्रकार न्यूनतम टूलींग शुल्क, गैर-आवर्ती इंजीनियरिंग, केवल मामूली रूप से बढ़ी हुई टुकड़ा भाग लागत, और तुलनीय प्रदर्शन प्रदान करते हैं। | शुद्ध तर्क केवल गेट सरणी डिजाइन आज सर्किट डिजाइनरों द्वारा शायद ही कभी लागू किया जाता है, इन्हें लगभग पूरी तरह से फील्ड प्रोग्राम करने योग्य उपकरणों द्वारा बदल दिया गया है। ऐसे उपकरणों में सबसे प्रमुख हैं फील्ड प्रोग्रामेबल गेट एरेज़ (एफपीजीए (FPGAs)) जिसे उपयोगकर्ता द्वारा प्रोग्राम किया जा सकता है और इस प्रकार न्यूनतम टूलींग शुल्क, गैर-आवर्ती इंजीनियरिंग, केवल मामूली रूप से बढ़ी हुई टुकड़ा भाग लागत, और तुलनीय प्रदर्शन प्रदान करते हैं। | ||

आज, गेट सरणियाँ संरचित | आज, गेट सरणियाँ संरचित एएसआईसी (ASIC)s में विकसित हो रही हैं जिसमें सीपीयू (CPU), डिजिटल सिग्नल प्रोसेसर इकाइयों, बाह्य उपकरणों, मानक इंटरफेस, एकीकृत मेमोरी, एसरैम (SRAM), और पुन: कॉन्फ़िगर करने योग्य, अनकमिटेड लॉजिक जैसे बड़े आईपी (IP) कोर शामिल हैं। यह बदलाव काफी हद तक इसलिए है क्योंकि एएसआईसी (ASIC) डिवाइस सिस्टम कार्यक्षमता के बड़े ब्लॉक को एकीकृत करने में सक्षम हैं, और चिप पर सिस्टम एसओसीएस (SoCs) को ग्लू लॉजिक, संचार सबसिस्टम (जैसे चिप पर नेटवर्क), बाह्य उपकरणों और अन्य घटकों की आवश्यकता होती है। केवल कार्यात्मक इकाइयों और बुनियादी अंतर्संबंध के बजाय। | ||

क्षेत्र में उनके लगातार उपयोग में, | क्षेत्र में उनके लगातार उपयोग में, एएसआईसी (ASIC)s का जिक्र करते समय "गेट एरे" और "सेमी-कस्टम" शब्द पर्यायवाची हैं। प्रोसेस इंजीनियर आमतौर पर "सेमी कस्टम" शब्द का उपयोग करते हैं, जबकि "गेट एरे" का उपयोग आमतौर पर लॉजिक (या गेट लेवल) डिजाइनरों द्वारा किया जाता है। | ||

== फुल-कस्टम डिज़ाइन == | == फुल-कस्टम डिज़ाइन == | ||

[[File:VLSI VL82C486 Single Chip 486 System Controller HV.jpg|thumb|कस्टम ASIC (486 चिपसेट) की माइक्रोस्कोप फोटोग्राफ टॉप पर गेट-आधारित डिज़ाइन और नीचे की ओर कस्टम सर्किटरी दिखा रहा है]] | [[File:VLSI VL82C486 Single Chip 486 System Controller HV.jpg|thumb|कस्टम एएसआईसी (ASIC) (486 चिपसेट) की माइक्रोस्कोप फोटोग्राफ टॉप पर गेट-आधारित डिज़ाइन और नीचे की ओर कस्टम सर्किटरी दिखा रहा है]] | ||

इसके विपरीत, पूर्ण कस्टम ASIC डिज़ाइन डिवाइस की सभी फोटोलिथोग्राफ़िक परतों को परिभाषित करता है।<ref name="MichaelJohnSebastianSmith"/> पूर्ण-कस्टम डिज़ाइन का उपयोग ASIC डिज़ाइन और मानक उत्पाद डिज़ाइन दोनों के लिए किया जाता है। | इसके विपरीत, पूर्ण कस्टम एएसआईसी (ASIC) डिज़ाइन डिवाइस की सभी फोटोलिथोग्राफ़िक परतों को परिभाषित करता है।<ref name="MichaelJohnSebastianSmith"/> पूर्ण-कस्टम डिज़ाइन का उपयोग एएसआईसी (ASIC) डिज़ाइन और मानक उत्पाद डिज़ाइन दोनों के लिए किया जाता है। | ||

पूर्ण कस्टम डिज़ाइन के लाभों में कम क्षेत्र (और इसलिए आवर्ती घटक लागत), प्रदर्शन सुधार, और एनालॉग घटकों और अन्य पूर्व-डिज़ाइन किए गए को एकीकृत करने की क्षमता भी और इस प्रकार पूरी तरह से सत्यापित घटक, जैसे माइक्रोप्रोसेसर कोर, जो एक चिप पर एक सिस्टम बनाते हैं। | '''पूर्ण कस्टम डिज़ाइन''' के लाभों में कम क्षेत्र (और इसलिए आवर्ती घटक लागत), प्रदर्शन सुधार, और एनालॉग घटकों और अन्य पूर्व-डिज़ाइन किए गए को एकीकृत करने की क्षमता भी और इस प्रकार पूरी तरह से सत्यापित घटक, जैसे माइक्रोप्रोसेसर कोर, जो एक चिप पर एक सिस्टम बनाते हैं। | ||

पूर्ण कस्टम डिज़ाइन के नुकसान में विनिर्माण और डिज़ाइन समय में वृद्धि, गैर-आवर्ती इंजीनियरिंग लागत में वृद्धि शामिल हो सकती है, जो कंप्यूटर एडेड डिज़ाइन (CAD) और इलेक्ट्रॉनिक डिज़ाइन ऑटोमेशन सिस्टम में अधिक जटिलता है, और डिजाइन टीम की ओर से बहुत अधिक कौशल की आवश्यकता है। | पूर्ण कस्टम डिज़ाइन के नुकसान में विनिर्माण और डिज़ाइन समय में वृद्धि, गैर-आवर्ती इंजीनियरिंग लागत में वृद्धि शामिल हो सकती है, जो कंप्यूटर एडेड डिज़ाइन कैड (CAD) और इलेक्ट्रॉनिक डिज़ाइन ऑटोमेशन सिस्टम में अधिक जटिलता है, और डिजाइन टीम की ओर से बहुत अधिक कौशल की आवश्यकता है। | ||

हालांकि, केवल-डिजिटल डिज़ाइनों के लिए, "मानक-सेल" सेल लाइब्रेरी, आधुनिक CAD सिस्टम के साथ, यह कम जोखिम के साथ काफी प्रदर्शन/लागत लाभ प्रदान कर सकता है। स्वचालित लेआउट उपकरण त्वरित और उपयोग में आसान हैं और डिजाइन के किसी भी प्रदर्शन सीमित पहलू को "हैंड-ट्वीक" या मैन्युअल रूप से अनुकूलित करने की संभावना भी प्रदान करते हैं। | हालांकि, केवल-डिजिटल डिज़ाइनों के लिए, "मानक-सेल" सेल लाइब्रेरी, आधुनिक कैड (CAD) सिस्टम के साथ, यह कम जोखिम के साथ काफी प्रदर्शन/लागत लाभ प्रदान कर सकता है। स्वचालित लेआउट उपकरण त्वरित और उपयोग में आसान हैं और डिजाइन के किसी भी प्रदर्शन सीमित पहलू को "हैंड-ट्वीक" या मैन्युअल रूप से अनुकूलित करने की संभावना भी प्रदान करते हैं। | ||

यह विशेष रूप से एक डिज़ाइन के लिए बुनियादी लॉजिक गेट्स, सर्किट या लेआउट का उपयोग करके डिज़ाइन किया गया है। | यह विशेष रूप से एक डिज़ाइन के लिए बुनियादी लॉजिक गेट्स, सर्किट या लेआउट का उपयोग करके डिज़ाइन किया गया है। | ||

== संरचित डिजाइन == | == संरचित डिजाइन == | ||

संरचित ASIC डिज़ाइन (जिसे "प्लेटफ़ॉर्म ASIC डिज़ाइन" भी कहा जाता है) सेमीकंडक्टर उद्योग में एक अपेक्षाकृत नया चलन है, जिसके परिणामस्वरूप इसकी परिभाषा में कुछ बदलाव आया है। हालाँकि, एक संरचित ASIC का मूल आधार यह है कि निर्माण चक्र समय और डिज़ाइन चक्र समय दोनों जो सेल-आधारित एएसआईसी की तुलना में कम हो गया है, क्योंकि पूर्व परिभाषित धातु परतें (इस प्रकार विनिर्माण समय को कम करना) और सिलिकॉन पर क्या है (इस प्रकार डिजाइन चक्र समय को कम करना) का पूर्व लक्षण वर्णन है। | '''संरचित एएसआईसी (ASIC) डिज़ाइन''' (जिसे "प्लेटफ़ॉर्म एएसआईसी (ASIC) डिज़ाइन" भी कहा जाता है) सेमीकंडक्टर उद्योग में एक अपेक्षाकृत नया चलन है, जिसके परिणामस्वरूप इसकी परिभाषा में कुछ बदलाव आया है। हालाँकि, एक संरचित एएसआईसी (ASIC) का मूल आधार यह है कि निर्माण चक्र समय और डिज़ाइन चक्र समय दोनों जो सेल-आधारित एएसआईसी की तुलना में कम हो गया है, क्योंकि पूर्व परिभाषित धातु परतें (इस प्रकार विनिर्माण समय को कम करना) और सिलिकॉन पर क्या है (इस प्रकार डिजाइन चक्र समय को कम करना) का पूर्व लक्षण वर्णन है। | ||

एम्बेडेड सिस्टम की नींव से परिभाषा में कहा गया है कि:<ref>{{Cite book|title=Foundations of Embedded Systems|last1=Barkalov|first1=Alexander|last2=Titarenko|first2=Larysa|last3=Mazurkiewicz|first3=Małgorzata|date=2019|publisher=Springer International Publishing|isbn=9783030119607|series=Studies in Systems, Decision and Control|volume=195|location=Cham|language=en|doi=10.1007/978-3-030-11961-4|s2cid=86596100}}</ref> {{quote|In a "structured ASIC" design, the logic mask-layers of a device are predefined by the ASIC vendor (or in some cases by a third party). Design differentiation and customization is achieved by creating custom metal layers that create custom connections between predefined lower-layer logic elements. "Structured ASIC" technology is seen as bridging the gap between field-programmable gate arrays and "standard-cell" ASIC designs. Because only a small number of chip layers must be custom-produced, "structured ASIC" designs have much smaller non-recurring expenditures (NRE) than "standard-cell" or "full-custom" chips, which require that a full mask set be produced for every design.|sign=|source=Foundations of Embedded Systems}} | एम्बेडेड सिस्टम की नींव से परिभाषा में कहा गया है कि:<ref>{{Cite book|title=Foundations of Embedded Systems|last1=Barkalov|first1=Alexander|last2=Titarenko|first2=Larysa|last3=Mazurkiewicz|first3=Małgorzata|date=2019|publisher=Springer International Publishing|isbn=9783030119607|series=Studies in Systems, Decision and Control|volume=195|location=Cham|language=en|doi=10.1007/978-3-030-11961-4|s2cid=86596100}}</ref> {{quote|In a "structured ASIC" design, the logic mask-layers of a device are predefined by the ASIC vendor (or in some cases by a third party). Design differentiation and customization is achieved by creating custom metal layers that create custom connections between predefined lower-layer logic elements. "Structured ASIC" technology is seen as bridging the gap between field-programmable gate arrays and "standard-cell" ASIC designs. Because only a small number of chip layers must be custom-produced, "structured ASIC" designs have much smaller non-recurring expenditures (NRE) than "standard-cell" or "full-custom" chips, which require that a full mask set be produced for every design.|sign=|source=Foundations of Embedded Systems}} | ||

यह प्रभावी रूप से गेट सरणी के समान परिभाषा है। एक संरचित ASIC को एक गेट सरणी से जो अलग करता है वह यह है कि एक गेट सरणी में, पूर्वनिर्धारित धातु की परतें विनिर्माण को तेजी से बदलने का काम करती हैं। एक संरचित ASIC में, पूर्वनिर्धारित धातुकरण का उपयोग मुख्य रूप से मास्क सेट की लागत को कम करने के साथ-साथ डिजाइन चक्र के समय को काफी कम करने के लिए होता है। | यह प्रभावी रूप से गेट सरणी के समान परिभाषा है। एक संरचित एएसआईसी (ASIC) को एक गेट सरणी से जो अलग करता है वह यह है कि एक गेट सरणी में, पूर्वनिर्धारित धातु की परतें विनिर्माण को तेजी से बदलने का काम करती हैं। एक संरचित एएसआईसी (ASIC) में, पूर्वनिर्धारित धातुकरण का उपयोग मुख्य रूप से मास्क सेट की लागत को कम करने के साथ-साथ डिजाइन चक्र के समय को काफी कम करने के लिए होता है। | ||

उदाहरण के लिए, सेल आधारित या गेट ऐरे डिज़ाइन में उपयोगकर्ता को अक्सर पावर, क्लॉक और टेस्ट स्ट्रक्चर को स्वयं डिज़ाइन करना चाहिए। इसके विपरीत, ये अधिकांश संरचित ASIC में पूर्वनिर्धारित होते हैं और इसलिए गेट ऐरे आधारित डिज़ाइनों की तुलना में डिज़ाइनर के लिए समय और खर्च बचा सकते हैं। इसी तरह, संरचित ASIC के लिए उपयोग किए जाने वाले डिज़ाइन टूल सेल आधारित टूल की तुलना में काफी कम लागत और उपयोग में आसान (तेज़) हो सकते हैं, क्योंकि उन्हें वे सभी कार्य करने की आवश्यकता नहीं है जो सेल आधारित उपकरण करते हैं। कुछ मामलों में, संरचित ASIC विक्रेता को अपने डिवाइस के लिए अनुकूलित टूल की आवश्यकता होती है (उदाहरण के लिए, कस्टम भौतिक संश्लेषण) का उपयोग किया जाए, और डिजाइन को और अधिक तेज़ी से निर्माण में लाने की अनुमति भी देता है। | उदाहरण के लिए, सेल आधारित या गेट ऐरे डिज़ाइन में उपयोगकर्ता को अक्सर पावर, क्लॉक और टेस्ट स्ट्रक्चर को स्वयं डिज़ाइन करना चाहिए। इसके विपरीत, ये अधिकांश संरचित एएसआईसी (ASIC) में पूर्वनिर्धारित होते हैं और इसलिए गेट ऐरे आधारित डिज़ाइनों की तुलना में डिज़ाइनर के लिए समय और खर्च बचा सकते हैं। इसी तरह, संरचित एएसआईसी (ASIC) के लिए उपयोग किए जाने वाले डिज़ाइन टूल सेल आधारित टूल की तुलना में काफी कम लागत और उपयोग में आसान (तेज़) हो सकते हैं, क्योंकि उन्हें वे सभी कार्य करने की आवश्यकता नहीं है जो सेल आधारित उपकरण करते हैं। कुछ मामलों में, संरचित एएसआईसी (ASIC) विक्रेता को अपने डिवाइस के लिए अनुकूलित टूल की आवश्यकता होती है (उदाहरण के लिए, कस्टम भौतिक संश्लेषण) का उपयोग किया जाए, और डिजाइन को और अधिक तेज़ी से निर्माण में लाने की अनुमति भी देता है। | ||

== सेल लाइब्रेरी, आईपी-आधारित डिज़ाइन, हार्ड और सॉफ्ट मैक्रोज़ == | == सेल लाइब्रेरी, आईपी-आधारित डिज़ाइन, हार्ड और सॉफ्ट मैक्रोज़ == | ||

तार्किक आदिम के सेल पुस्तकालय आमतौर पर डिवाइस निर्माता द्वारा सेवा के हिस्से के रूप में प्रदान किए जाते हैं। हालांकि उन्हें कोई अतिरिक्त लागत नहीं लगेगी, उनकी रिहाई एक गैर प्रकटीकरण समझौते (एनडीए) की शर्तों द्वारा कवर की जाएगी और उन्हें निर्माता द्वारा बौद्धिक संपदा के रूप में माना जाएगा। आमतौर पर, उनके भौतिक डिज़ाइन को पूर्व परिभाषित किया जाएगा ताकि उन्हें "हार्ड मैक्रोज़" कहा जा सके। | तार्किक आदिम के सेल पुस्तकालय आमतौर पर डिवाइस निर्माता द्वारा सेवा के हिस्से के रूप में प्रदान किए जाते हैं। हालांकि उन्हें कोई अतिरिक्त लागत नहीं लगेगी, उनकी रिहाई एक गैर प्रकटीकरण समझौते (एनडीए NDA) की शर्तों द्वारा कवर की जाएगी और उन्हें निर्माता द्वारा बौद्धिक संपदा के रूप में माना जाएगा। आमतौर पर, उनके भौतिक डिज़ाइन को पूर्व परिभाषित किया जाएगा ताकि उन्हें "हार्ड मैक्रोज़" कहा जा सके। | ||

अधिकांश इंजीनियर जिसे "बौद्धिक संपदा" समझते हैं, वे हैं आईपी कोर, ये डिज़ाइन किसी तीसरे पक्ष से बड़े ASIC के उप घटकों के रूप में खरीदे गए हैं। उन्हें हार्डवेयर विवरण भाषा के रूप में प्रदान किया जा सकता है (जिसे अक्सर "सॉफ्ट मैक्रो" कहा जाता है), या पूरी तरह से रूटेड डिज़ाइन के रूप में जिसे सीधे ASIC के मास्क पर प्रिंट किया जा सकता है (जिसे अक्सर "हार्ड मैक्रो" कहा जाता है)। कई संगठन अब ऐसे पूर्व-डिज़ाइन किए गए कोर सीपीयू, ईथरनेट, यूएसबी या टेलीफोन इंटरफेस बेचते हैं और बड़े संगठनों के पास शेष संगठन के लिए कोर तैयार करने के लिए एक संपूर्ण विभाग या प्रभाग हो सकता है। कंपनी एआरएम (एडवांस्ड आरआईएससी मशीन्स) केवल आईपी कोर बेचती है, जिससे यह एक सक्षम निर्माता बन जाता है। | अधिकांश इंजीनियर जिसे "बौद्धिक संपदा" समझते हैं, वे हैं आईपी कोर, ये डिज़ाइन किसी तीसरे पक्ष से बड़े एएसआईसी (ASIC) के उप घटकों के रूप में खरीदे गए हैं। उन्हें हार्डवेयर विवरण भाषा के रूप में प्रदान किया जा सकता है (जिसे अक्सर "सॉफ्ट मैक्रो" कहा जाता है), या पूरी तरह से रूटेड डिज़ाइन के रूप में जिसे सीधे एएसआईसी (ASIC) के मास्क पर प्रिंट किया जा सकता है (जिसे अक्सर "हार्ड मैक्रो" कहा जाता है)। कई संगठन अब ऐसे पूर्व-डिज़ाइन किए गए कोर सीपीयू, ईथरनेट, यूएसबी या टेलीफोन इंटरफेस बेचते हैं और बड़े संगठनों के पास शेष संगठन के लिए कोर तैयार करने के लिए एक संपूर्ण विभाग या प्रभाग हो सकता है। कंपनी एआरएम (एडवांस्ड आरआईएससी मशीन्स) केवल आईपी कोर बेचती है, जिससे यह एक सक्षम निर्माता बन जाता है। | ||

वास्तव में, संरचित ASIC डिजाइन में अब उपलब्ध कार्यों की विस्तृत श्रृंखला 1990 के दशक के अंत और 2000 के दशक की शुरुआत में इलेक्ट्रॉनिक्स में अभूतपूर्व सुधार का परिणाम है; एक कोर के रूप में बनाने में बहुत समय और निवेश लगता है, इसका पुन: उपयोग और आगे विकास उत्पाद चक्र के समय में नाटकीय रूप से कटौती करता है और बेहतर उत्पाद बनाता है। इसके अतिरिक्त, ओपन-सोर्स हार्डवेयर संगठन जैसे ओपन कोर मुफ्त आईपी कोर एकत्र कर रहे हैं, हार्डवेयर डिजाइन में ओपन सोर्स सॉफ्टवेयर आंदोलन के समानांतर। | वास्तव में, संरचित एएसआईसी (ASIC) डिजाइन में अब उपलब्ध कार्यों की विस्तृत श्रृंखला 1990 के दशक के अंत और 2000 के दशक की शुरुआत में इलेक्ट्रॉनिक्स में अभूतपूर्व सुधार का परिणाम है; एक कोर के रूप में बनाने में बहुत समय और निवेश लगता है, इसका पुन: उपयोग और आगे विकास उत्पाद चक्र के समय में नाटकीय रूप से कटौती करता है और बेहतर उत्पाद बनाता है। इसके अतिरिक्त, ओपन-सोर्स हार्डवेयर संगठन जैसे ओपन कोर मुफ्त आईपी कोर एकत्र कर रहे हैं, हार्डवेयर डिजाइन में ओपन सोर्स सॉफ्टवेयर आंदोलन के समानांतर। | ||

सॉफ्ट मैक्रोज़ अक्सर प्रक्रिया से स्वतंत्र होते हैं (अर्थात उन्हें निर्माण प्रक्रियाओं और विभिन्न निर्माताओं की एक विस्तृत श्रृंखला पर गढ़ा जा सकता है)। हार्ड मैक्रोज़ प्रक्रिया-सीमित होते हैं और आमतौर पर आगे के डिज़ाइन प्रयासों को किसी भिन्न प्रक्रिया या निर्माता में माइग्रेट (पोर्ट) करने के लिए निवेश किया जाना चाहिए। | सॉफ्ट मैक्रोज़ अक्सर प्रक्रिया से स्वतंत्र होते हैं (अर्थात उन्हें निर्माण प्रक्रियाओं और विभिन्न निर्माताओं की एक विस्तृत श्रृंखला पर गढ़ा जा सकता है)। हार्ड मैक्रोज़ प्रक्रिया-सीमित होते हैं और आमतौर पर आगे के डिज़ाइन प्रयासों को किसी भिन्न प्रक्रिया या निर्माता में माइग्रेट (पोर्ट) करने के लिए निवेश किया जाना चाहिए। | ||

== मल्टी-प्रोजेक्ट वेफर्स == | == मल्टी-प्रोजेक्ट वेफर्स == | ||

कुछ निर्माता और IC डिज़ाइन हाउस कम लागत वाले प्रोटोटाइप प्राप्त करने की एक विधि के रूप में मल्टी प्रोजेक्ट वेफर सर्विस (MPW) प्रदान करते हैं। अक्सर शटल कहा जाता है, ये एमपीडब्ल्यू, जिसमें कई डिज़ाइन होते हैं, "कट एंड गो" आधार पर नियमित, निर्धारित अंतराल पर चलते हैं, आमतौर पर निर्माता की ओर से सीमित देयता होती है। अनुबंध में बेयर डाइस की डिलीवरी या मुट्ठी भर उपकरणों की असेंबली और पैकेजिंग शामिल है। सेवा में आमतौर पर एक भौतिक डिज़ाइन डेटाबेस (यानी मास्किंग जानकारी या पैटर्न जनरेशन (पीजी | कुछ निर्माता और आईसी (IC) डिज़ाइन हाउस कम लागत वाले प्रोटोटाइप प्राप्त करने की एक विधि के रूप में '''मल्टी प्रोजेक्ट वेफर सर्विस एमपीडब्लू (MPW)''' प्रदान करते हैं। अक्सर शटल कहा जाता है, ये एमपीडब्ल्यू, जिसमें कई डिज़ाइन होते हैं, "कट एंड गो" आधार पर नियमित, निर्धारित अंतराल पर चलते हैं, आमतौर पर निर्माता की ओर से सीमित देयता होती है। अनुबंध में बेयर डाइस की डिलीवरी या मुट्ठी भर उपकरणों की असेंबली और पैकेजिंग शामिल है। सेवा में आमतौर पर एक भौतिक डिज़ाइन डेटाबेस (यानी मास्किंग जानकारी या पैटर्न जनरेशन (पीजी PG टेप) की आपूर्ति शामिल होती है। प्रक्रिया में कम भागीदारी के कारण निर्माता को अक्सर "'''सिलिकॉन फाउंड्री'''" के रूप में जाना जाता है। | ||

== अनुप्रयोग-विशिष्ट मानक उत्पाद == | == अनुप्रयोग-विशिष्ट मानक उत्पाद == | ||

[[File:Kyocera FS-C5200DN - interface board - Renesas M66591GP-4189.jpg|thumb|Renesas M66591GP: | [[File:Kyocera FS-C5200DN - interface board - Renesas M66591GP-4189.jpg|thumb|रेनिसास (Renesas) M66591GP: यूएसबी (USB)2.0 परिधीय नियंत्रक]] | ||

एक अनुप्रयोग विशिष्ट मानक उत्पाद या ASSP एक एकीकृत परिपथ है जो एक विशिष्ट कार्य को लागू करता है जो एक व्यापक बाजार के लिए अपील करता है। ASIC के विपरीत जो कार्यों के संग्रह को जोड़ती है और ये एक ग्राहक द्वारा या उसके लिए डिज़ाइन किए गए हैं, | एक '''अनुप्रयोग विशिष्ट मानक उत्पाद या एएसएसपी (ASSP)''' एक एकीकृत परिपथ है जो एक विशिष्ट कार्य को लागू करता है जो एक व्यापक बाजार के लिए अपील करता है। एएसआईसी (ASIC) के विपरीत जो कार्यों के संग्रह को जोड़ती है और ये एक ग्राहक द्वारा या उसके लिए डिज़ाइन किए गए हैं, एएसएसपी (ASSP)s शेल्फ घटकों के रूप में उपलब्ध हैं। ऑटोमोटिव से लेकर संचार तक सभी उद्योगों में एएसएसपी (ASSP) का उपयोग किया जाता है। एक सामान्य नियम के रूप में, यदि आप डेटा बुक में कोई डिज़ाइन पा सकते हैं, तो शायद यह एएसआईसी (ASIC) नहीं है, लेकिन कुछ अपवाद हैं। उदाहरण के लिए, दो आईसी जिन्हें एएसआईसी माना जा सकता है या नहीं, एक पीसी के लिए एक नियंत्रक चिप और एक मॉडेम के लिए एक चिप है। ये दोनों उदाहरण किसी एप्लिकेशन के लिए विशिष्ट हैं (जो एएसआईसी (ASIC) के लिए विशिष्ट है) लेकिन कई अलग-अलग सिस्टम विक्रेताओं को बेचे जाते हैं (जो मानक भागों के लिए विशिष्ट है)। एएसआईसी (ASIC) जैसे कि इन्हें कभी-कभी एप्लिकेशन '''विशिष्ट मानक उत्पाद''' (एएसएसपी -ASSP) कहा जाता है। | ||

एएसएसपी के उदाहरण एन्कोडिंग/डिकोडिंग चिप, ईथरनेट नेटवर्क इंटरफेस कंट्रोलर चिप आदि हैं। | एएसएसपी (ASSP) के उदाहरण एन्कोडिंग/डिकोडिंग चिप, ईथरनेट नेटवर्क इंटरफेस कंट्रोलर चिप आदि हैं। | ||

IEEE एक ASSP पत्रिका प्रकाशित करता था,<ref>[http://ieeexplore.ieee.org/xpl/tocresult.jsp?isnumber=26080 IEEE ASSP Issue 2, Part 1 – April 1984]</ref> जिसे 1990 में IEEE सिग्नल प्रोसेसिंग मैगज़ीन में बदल दिया गया था। | '''आईईईई (IEEE)''' एक एएसएसपी (ASSP) पत्रिका प्रकाशित करता था,<ref>[http://ieeexplore.ieee.org/xpl/tocresult.jsp?isnumber=26080 IEEE ASSP Issue 2, Part 1 – April 1984]</ref> जिसे 1990 में आईईईई (IEEE) सिग्नल प्रोसेसिंग मैगज़ीन में बदल दिया गया था। | ||

== यह भी देखें == | == यह भी देखें == | ||

{{cols}} | {{cols}} | ||

* आवेदन-विशिष्ट अनुदेश सेट प्रोसेसर (ASIP) | * आवेदन-विशिष्ट अनुदेश सेट प्रोसेसर (एएसआईपी ASIP) | ||

* कॉम्प्लेक्स प्रोग्रामेबल लॉजिक डिवाइस (CPLD) | * कॉम्प्लेक्स प्रोग्रामेबल लॉजिक डिवाइस (सीपीएलडी CPLD) | ||

* इलेक्ट्रॉनिक डिजाइन स्वचालन (EDA या ECAD) | * इलेक्ट्रॉनिक डिजाइन स्वचालन (ईडीए EDA या ईसीएडी ECAD) | ||

* फील्ड-प्रोग्रामेबल गेट एरे (FPGA) | * फील्ड-प्रोग्रामेबल गेट एरे (एफपीजीए FPGA) | ||

* मल्टी-प्रोजेक्ट चिप (एमपीसी) | * मल्टी-प्रोजेक्ट चिप (एमपीसी MPC) | ||

* बहुत बड़े पैमाने पर एकीकरण (VLSI) | * बहुत बड़े पैमाने पर एकीकरण (वीएलएसआई VLSI) | ||

* सिस्टम-ऑन-ए-चिप (SOC) | * सिस्टम-ऑन-ए-चिप (एसओसी SOC) | ||

* मुख्य रूप से हार्डवेयर में आधारित कंप्यूटिंग के अवलोकन के लिए हार्डवेयर त्वरण | * मुख्य रूप से हार्डवेयर में आधारित कंप्यूटिंग के अवलोकन के लिए हार्डवेयर त्वरण | ||

{{colend}} | {{colend}} | ||

Revision as of 01:16, 31 August 2022

This article includes a list of general references, but it lacks sufficient corresponding inline citations. (October 2015) (Learn how and when to remove this template message) |

एक एप्लिकेशन-विशिष्ट एकीकृत सर्किट (एएसआईसी) एक एकीकृत सर्किट (आईसी) चिप है जिसे सामान्य प्रयोजन के उपयोग के बजाय किसी विशेष उपयोग के लिए अनुकूलित किया जाता है।उदाहरण के लिए, डिजिटल वॉयस रिकॉर्डर या उच्च दक्षता वाले वीडियो कोडेक (जैसे एएमडी वीसीई) में चलने के लिए डिज़ाइन की गई चिप एक एएसआईसी है। यह 7400 श्रृंखला या 4000 श्रृंखला की तरह है।[1] एएसआईसी (ASIC) चिप्स आमतौर पर मेटल ऑक्साइड सेमीकंडक्टर एसओएस (MOS) तकनीक का उपयोग करके बनाए जाते हैं, उदाहरण के लिए एमओएस एकीकृत सर्किट चिप्स के रूप में। [2]

जैसे-जैसे फीचर आकार सिकुड़ते गए हैं और डिज़ाइन टूल में वर्षों में सुधार हुआ है, एएसआईसी (ASIC) में संभव अधिकतम जटिलता (और इसलिए कार्यक्षमता) 5,000 लॉजिक गेट्स से बढ़कर 100 मिलियन से अधिक हो गई है। आधुनिक एएसआईसी (ASIC) में अक्सर संपूर्ण माइक्रोप्रोसेसर, रोम (ROM) , रैम (RAM), ईईपीरोम (EEPROM), फ्लैश मेमोरी और अन्य बड़े बिल्डिंग ब्लॉक सहित मेमोरी ब्लॉक शामिल होते हैं। ऐसे एएसआईसी (ASIC) को अक्सर एसओसी (SoC) (सिस्टम-ऑन-चिप) कहा जाता है। डिजिटल एएसआईसी (ASIC) के डिजाइनर अक्सर एक हार्डवेयर विवरण भाषा एचडीएल (HDL) का उपयोग करते हैं, जैसे वेरिलोग या वीएचडीएल, एएसआईसी की कार्यक्षमता का वर्णन करने के लिए[1]

फील्ड प्रोग्रामेबल गेट एरेज़ एफपीजीए (FPGA) ब्रेडबोर्ड पर आधुनिक दिन प्रौद्योगिकी सुधार हैं, इसका मतलब है कि एएसआईसी (ASIC) के विपरीत उन्हें एप्लिकेशन विशिष्ट नहीं बनाया गया है। प्रोग्रामेबल लॉजिक ब्लॉक और प्रोग्रामेबल इंटरकनेक्ट एक ही एफपीजीए (FPGA) को कई अलग-अलग अनुप्रयोगों में उपयोग करने की अनुमति देते हैं। छोटे डिज़ाइन या कम उत्पादन मात्रा के लिए, एफपीजीए (FPGA)s एएसआईसी (ASIC) डिज़ाइन की तुलना में अधिक लागत प्रभावी हो सकते हैं, यहाँ तक कि उत्पादन में भी। एएसआईसी (ASIC) की गैर-आवर्ती इंजीनियरिंग (NRE) लागत लाखों डॉलर में चल सकती है। इसलिए, डिवाइस निर्माता आमतौर पर प्रोटोटाइप और कम उत्पादन मात्रा वाले उपकरणों के लिए एफपीजीए (FPGA)s पसंद करते हैं और एएसआईसी बहुत बड़े उत्पादन संस्करणों के लिए जहां एनआरई लागत को कई उपकरणों में परिशोधित किया जा सकता है।

इतिहास

प्रारंभिक एएसआईसी (ASIC)s ने गेट ऐरे तकनीक का उपयोग किया। 1967 तक, फेरांति और इंटरडिजाइन प्रारंभिक द्विध्रुवी गेट सरणियों का निर्माण कर रहे थे। 1967 में, फेयरचाइल्ड सेमीकंडक्टर ने द्विध्रुवी डायोड-ट्रांजिस्टर लॉजिक डीटीएल (DTL) और ट्रांजिस्टर-ट्रांजिस्टर लॉजिक टीटीएल (TTL) सरणियों के माइक्रोमैट्रिक्स परिवार की शुरुआत की।[2]

पूरक धातु ऑक्साइड सेमीकंडक्टर सीएमओएस (CMOS) तकनीक ने गेट सरणियों के व्यापक व्यावसायीकरण का द्वार खोल दिया। पहला सीएमओएस (CMOS) गेट सरणियाँ रॉबर्ट लिप द्वारा 1974 में इंटरनेशनल माइक्रोसर्किट इंक. (International Microcircuits, Inc. (IMI))[2] के लिए विकसित किया गया था।[3][4]

मेटल ऑक्साइड सेमीकंडक्टर एमओएस (MOS) मानक सेल तकनीक फेयरचाइल्ड और मोटोरोला द्वारा पेश की गई थी, जो 1970 के दशक में व्यापार नाम माइक्रोमोसाइक और पॉलीसेल के तहत है। इस तकनीक का बाद में वीएलएसआई टेक्नोलॉजी (1979 में स्थापित) और एलएसआई (LSI) लॉजिक (1981) द्वारा सफलतापूर्वक व्यावसायीकरण किया गया।[2]

गेट एरे सर्किट्री का एक सफल व्यावसायिक अनुप्रयोग जो 1981 और 1982 में पेश किए गए लो एंड 8 बिट जेड एक्स (ZX) 81 और जेड एक्स (ZX) स्पेक्ट्रम पर्सनल कंप्यूटर में पाया गया था। इनका उपयोग सिनक्लेयर रिसर्च (यूके) द्वारा अनिवार्य रूप से कम लागत वाले इनपुट आउटपुट समाधान के रूप में किया गया था जिसका उद्देश्य कंप्यूटर के ग्राफिक्स को संभालना था।

मेटल इंटरकनेक्ट मास्क को बदलकर अनुकूलन हुआ। गेट सरणियों में कुछ हज़ार फाटकों तक की जटिलताएँ थीं; इसे अब मिड स्केल इंटीग्रेशन कहा जाता है। बाद के संस्करण अधिक सामान्यीकृत हो गए, धातु और पॉलीसिलिकॉन दोनों परतों द्वारा अनुकूलित विभिन्न आधार मर जाते हैं। कुछ बेस डेज़ में रैंडम एक्सेस मेमोरी (RAM) तत्व भी शामिल होते हैं।

मानक-कोशिका डिजाइन

1980 के दशक के मध्य में, एक डिज़ाइनर एएसआईसी (ASIC) निर्माता का चयन करेगा और निर्माता से उपलब्ध डिज़ाइन टूल का उपयोग करके उनके डिज़ाइन को लागू करेगा जबकि तृतीय पक्ष डिज़ाइन उपकरण उपलब्ध थे, तीसरे पक्ष के डिज़ाइन टूल से लेआउट के लिए कोई प्रभावी लिंक नहीं था और विभिन्न एएसआईसी (ASIC) निर्माताओं की वास्तविक अर्धचालक प्रक्रिया प्रदर्शन विशेषताओं। अधिकांश डिजाइनरों ने अपने डिजाइन के कार्यान्वयन को पूरा करने के लिए कारखाने के विशिष्ट उपकरणों का इस्तेमाल किया। जो इस समस्या का समाधान है, जिससे बहुत अधिक घनत्व वाला उपकरण भी प्राप्त हुआ, और यह मानक कोशिकाओं का कार्यान्वयन था।[5]

प्रत्येक एएसआईसी (ASIC) निर्माता ज्ञात विद्युत विशेषताओं के साथ कार्यात्मक ब्लॉक बना सकता है, जैसे प्रसार विलंब, समाई और अधिष्ठापन, जिसे तृतीय पक्ष टूल में भी प्रदर्शित किया जा सकता है। मानक सेल डिजाइन बहुत उच्च गेट घनत्व और अच्छे विद्युत प्रदर्शन को प्राप्त करने के लिए इन कार्यात्मक ब्लॉकों का उपयोग है। मानक सेल डिज़ाइन § गेट सरणी और अर्ध कस्टम डिज़ाइन (Gate-array and semi-custom design) और § पूर्ण कस्टम डिज़ाइन (Full-custom design) के बीच इसकी गैर-आवर्ती इंजीनियरिंग और आवर्ती घटक लागत के साथ-साथ प्रदर्शन और विकास की गति (बाजार में समय सहित) के बीच मध्यवर्ती है।

1990 के दशक के अंत तक, तर्क संश्लेषण उपकरण उपलब्ध हो गए। ऐसे उपकरण एचडीएल विवरण को गेट स्तर की नेटलिस्ट में संकलित कर सकते हैं। स्टैंडर्ड सेल इंटीग्रेटेड सर्किट (ICs) को निम्नलिखित वैचारिक चरणों में डिज़ाइन किया गया है जिन्हें इलेक्ट्रॉनिक्स डिज़ाइन फ्लो कहा जाता है, हालांकि ये चरण व्यवहार में महत्वपूर्ण रूप से ओवरलैप करते हैं:

- आवश्यकताएँ इंजीनियरिंग: डिज़ाइन इंजीनियरों की एक टीम एक नए एएसआईसी (ASIC) के लिए आवश्यक कार्यों की गैर-औपचारिक समझ के साथ शुरू होती है, जो आमतौर पर आवश्यकताओं के विश्लेषण से प्राप्त होता है।

- रजिस्टर-ट्रांसफर लेवल आरटीएल (RTL) डिज़ाइन: डिज़ाइन टीम हार्डवेयर विवरण भाषा का उपयोग करके इन लक्ष्यों को प्राप्त करने के लिए एएसआईसी (ASIC) के विवरण का निर्माण करती है। यह प्रक्रिया एक उच्च स्तरीय भाषा में कंप्यूटर प्रोग्राम लिखने के समान है।

- कार्यात्मक सत्यापन: उद्देश्य के लिए उपयुक्तता कार्यात्मक सत्यापन द्वारा सत्यापित की जाती है। इसमें परीक्षण बेंच के माध्यम से तर्क अनुकरण, औपचारिक सत्यापन, अनुकरण, या सिमिक्स के समान शुद्ध सॉफ्टवेयर मॉडल बनाने और मूल्यांकन करने जैसी तकनीकें शामिल हो सकती हैं। प्रत्येक सत्यापन तकनीक के फायदे और नुकसान हैं, और अक्सर एएसआईसी (ASIC) सत्यापन के लिए कई विधियों का एक साथ उपयोग किया जाता है। अधिकांश एफपीजीए (FPGA)s के विपरीत, एएसआईसी (ASIC) को एक बार गढ़े जाने के बाद पुन: प्रोग्राम नहीं किया जा सकता है और इसलिए एएसआईसी (ASIC) डिज़ाइन जो पूरी तरह से सही नहीं हैं, वे बहुत अधिक महंगे हैं, जिससे पूर्ण परीक्षण कवरेज की आवश्यकता बढ़ जाती है।

- लॉजिक सिंथेसिस: लॉजिक सिंथेसिस आरटीएल डिज़ाइन को एक बड़े संग्रह में बदल देता है जिसे निचले स्तर के निर्माण कहा जाता है जिसे मानक सेल कहा जाता है। इन निर्माणों को एक मानक सेल लाइब्रेरी से लिया गया है जिसमें विशिष्ट कार्य करने वाले लॉजिक गेट्स के पूर्व-विशिष्ट संग्रह शामिल हैं। मानक सेल आमतौर पर एएसआईसी (ASIC) के नियोजित निर्माता के लिए विशिष्ट होते हैं। मानक कोशिकाओं का परिणामी संग्रह और उनके बीच आवश्यक विद्युत कनेक्शन को गेट लेवल नेटलिस्ट कहा जाता है।

- प्लेसमेंट: गेट स्तरीय नेटलिस्ट को अगली बार प्लेसमेंट टूल द्वारा संसाधित किया जाता है जो मानक कोशिकाओं को अंतिम एएसआईसी (ASIC) का प्रतिनिधित्व करने वाले एकीकृत सर्किट डाई के क्षेत्र में रखता है। प्लेसमेंट टूल मानक सेल का एक अनुकूलित प्लेसमेंट खोजने का प्रयास करता है, और यह विभिन्न निर्दिष्ट बाधाओं के अधीन है।

- रूटिंग: एक इलेक्ट्रॉनिक्स रूटिंग टूल मानक कोशिकाओं का भौतिक स्थान लेता है और उनके बीच विद्युत कनेक्शन बनाने के लिए नेटलिस्ट का उपयोग करता है। चूंकि खोज स्थान बड़ा है, इसलिए यह प्रक्रिया "विश्व स्तर पर इष्टतम" समाधान के बजाय "पर्याप्त" उत्पन्न करेगी। आउटपुट एक फाइल है जिसका उपयोग सेमीकंडक्टर फैब्रिकेशन सुविधा को सक्षम करने वाले फोटोमास्क का एक सेट बनाने के लिए किया जा सकता है, जिसे आमतौर पर भौतिक एकीकृत परिपथों के निर्माण के लिए 'फैब' या 'फाउंड्री' कहा जाता है। प्लेसमेंट और रूटिंग का आपस में गहरा संबंध है और इन्हें सामूहिक रूप से इलेक्ट्रॉनिक्स डिजाइन में स्थान और मार्ग कहा जाता है।

- साइन-ऑफ: अंतिम लेआउट को देखते हुए, सर्किट निष्कर्षण परजीवी प्रतिरोधों और समाई की गणना करता है। डिजिटल सर्किट के मामले में, इसे फिर देरी की जानकारी में मैप किया जाएगा जिससे सर्किट प्रदर्शन का अनुमान लगाया जा सकता है, आमतौर पर स्थैतिक समय विश्लेषण द्वारा। यह, और अन्य अंतिम परीक्षण जैसे कि डिज़ाइन नियम की जाँच और शक्ति विश्लेषण को सामूहिक रूप से साइनऑफ़ कहा जाता है, यह सुनिश्चित करने के लिए है कि डिवाइस प्रक्रिया, वोल्टेज और तापमान के सभी चरम सीमाओं पर सही ढंग से कार्य करेगा। जब यह परीक्षण पूरा हो जाता है तो चिप निर्माण के लिए फोटोमास्क जानकारी जारी की जाती है।

उद्योग में सामान्य कौशल के स्तर के साथ लागू किए गए ये कदम, लगभग हमेशा एक अंतिम उपकरण का उत्पादन करता है जो मूल डिजाइन को सही ढंग से लागू करता है, जब तक दोषों को बाद में भौतिक निर्माण प्रक्रिया द्वारा पेश नहीं किया जाता है।[6]

डिज़ाइन चरण जिसे डिज़ाइन प्रवाह भी कहा जाता है, मानक उत्पाद डिज़ाइन के लिए भी सामान्य हैं। महत्वपूर्ण अंतर यह है कि मानक सेल डिज़ाइन निर्माता के सेल पुस्तकालयों का उपयोग करता है जिनका उपयोग संभावित रूप से सैकड़ों अन्य डिज़ाइन कार्यान्वयन में किया गया है और इसलिए पूर्ण कस्टम डिज़ाइन की तुलना में बहुत कम जोखिम वाले हैं। मानक सेल एक डिज़ाइन घनत्व उत्पन्न करते हैं जो कि लागत प्रभावी है, और वे गेट सरणियों के विपरीत, आईपी कोर और स्थिर रैंडम एक्सेस मेमोरी (एसआरएएम) को प्रभावी ढंग से एकीकृत कर सकते हैं।

गेट-सरणी और अर्ध-कस्टम डिजाइन

गेट ऐरे डिज़ाइन एक निर्माण विधि है जिसमें विसरित परतें, प्रत्येक में ट्रांजिस्टर होते है और अन्य सक्रिय उपकरण, पूर्वनिर्धारित हैं और इलेक्ट्रॉनिक वेफर्स युक्त है ऐसे उपकरण "स्टॉक में रखे जाते हैं" या निर्माण प्रक्रिया के धातुकरण चरण से पहले असंबद्ध होते हैं। भौतिक डिजाइन प्रक्रिया अंतिम उपकरण के लिए इन परतों के अंतर्संबंधों को परिभाषित करती है। अधिकांश एएसआईसी (ASIC) निर्माताओं के लिए, इसमें दो और नौ धातु परतें होती हैं प्रत्येक परत उसके नीचे की परत के लंबवत चलती है। गैर-आवर्ती इंजीनियरिंग लागत पूर्ण कस्टम डिज़ाइन की तुलना में बहुत कम है, चूंकि फोटोलिथोग्राफिक मास्क केवल धातु की परतों के लिए आवश्यक हैं। उत्पादन चक्र बहुत कम हैं, चूंकि धातुकरण एक अपेक्षाकृत त्वरित प्रक्रिया है; जिससे बाजार के लिए समय में तेजी आ रही है।

गेट ऐरे एएसआईसी (ASIC)s हमेशा तेजी से डिजाइन और प्रदर्शन के बीच एक समझौता होते हैं एक निर्माता द्वारा स्टॉक वेफर के रूप में रखे जाने पर दिए गए डिज़ाइन को मैप करने के रूप में जो कभी भी 100% सर्किट उपयोग नहीं देता है। अक्सर इंटरकनेक्ट को रूट करने में कठिनाइयों के लिए बड़े एरे डिवाइस पर माइग्रेशन की आवश्यकता होती है, जिसके परिणामस्वरूप पीस पार्ट की कीमत में वृद्धि होती है। ये कठिनाइयाँ अक्सर इंटरकनेक्ट को विकसित करने के लिए उपयोग किए जाने वाले लेआउट ईडीए (EDA) सॉफ़्टवेयर का परिणाम होती हैं।

शुद्ध तर्क केवल गेट सरणी डिजाइन आज सर्किट डिजाइनरों द्वारा शायद ही कभी लागू किया जाता है, इन्हें लगभग पूरी तरह से फील्ड प्रोग्राम करने योग्य उपकरणों द्वारा बदल दिया गया है। ऐसे उपकरणों में सबसे प्रमुख हैं फील्ड प्रोग्रामेबल गेट एरेज़ (एफपीजीए (FPGAs)) जिसे उपयोगकर्ता द्वारा प्रोग्राम किया जा सकता है और इस प्रकार न्यूनतम टूलींग शुल्क, गैर-आवर्ती इंजीनियरिंग, केवल मामूली रूप से बढ़ी हुई टुकड़ा भाग लागत, और तुलनीय प्रदर्शन प्रदान करते हैं।

आज, गेट सरणियाँ संरचित एएसआईसी (ASIC)s में विकसित हो रही हैं जिसमें सीपीयू (CPU), डिजिटल सिग्नल प्रोसेसर इकाइयों, बाह्य उपकरणों, मानक इंटरफेस, एकीकृत मेमोरी, एसरैम (SRAM), और पुन: कॉन्फ़िगर करने योग्य, अनकमिटेड लॉजिक जैसे बड़े आईपी (IP) कोर शामिल हैं। यह बदलाव काफी हद तक इसलिए है क्योंकि एएसआईसी (ASIC) डिवाइस सिस्टम कार्यक्षमता के बड़े ब्लॉक को एकीकृत करने में सक्षम हैं, और चिप पर सिस्टम एसओसीएस (SoCs) को ग्लू लॉजिक, संचार सबसिस्टम (जैसे चिप पर नेटवर्क), बाह्य उपकरणों और अन्य घटकों की आवश्यकता होती है। केवल कार्यात्मक इकाइयों और बुनियादी अंतर्संबंध के बजाय।

क्षेत्र में उनके लगातार उपयोग में, एएसआईसी (ASIC)s का जिक्र करते समय "गेट एरे" और "सेमी-कस्टम" शब्द पर्यायवाची हैं। प्रोसेस इंजीनियर आमतौर पर "सेमी कस्टम" शब्द का उपयोग करते हैं, जबकि "गेट एरे" का उपयोग आमतौर पर लॉजिक (या गेट लेवल) डिजाइनरों द्वारा किया जाता है।

फुल-कस्टम डिज़ाइन

इसके विपरीत, पूर्ण कस्टम एएसआईसी (ASIC) डिज़ाइन डिवाइस की सभी फोटोलिथोग्राफ़िक परतों को परिभाषित करता है।[5] पूर्ण-कस्टम डिज़ाइन का उपयोग एएसआईसी (ASIC) डिज़ाइन और मानक उत्पाद डिज़ाइन दोनों के लिए किया जाता है।

पूर्ण कस्टम डिज़ाइन के लाभों में कम क्षेत्र (और इसलिए आवर्ती घटक लागत), प्रदर्शन सुधार, और एनालॉग घटकों और अन्य पूर्व-डिज़ाइन किए गए को एकीकृत करने की क्षमता भी और इस प्रकार पूरी तरह से सत्यापित घटक, जैसे माइक्रोप्रोसेसर कोर, जो एक चिप पर एक सिस्टम बनाते हैं।

पूर्ण कस्टम डिज़ाइन के नुकसान में विनिर्माण और डिज़ाइन समय में वृद्धि, गैर-आवर्ती इंजीनियरिंग लागत में वृद्धि शामिल हो सकती है, जो कंप्यूटर एडेड डिज़ाइन कैड (CAD) और इलेक्ट्रॉनिक डिज़ाइन ऑटोमेशन सिस्टम में अधिक जटिलता है, और डिजाइन टीम की ओर से बहुत अधिक कौशल की आवश्यकता है।

हालांकि, केवल-डिजिटल डिज़ाइनों के लिए, "मानक-सेल" सेल लाइब्रेरी, आधुनिक कैड (CAD) सिस्टम के साथ, यह कम जोखिम के साथ काफी प्रदर्शन/लागत लाभ प्रदान कर सकता है। स्वचालित लेआउट उपकरण त्वरित और उपयोग में आसान हैं और डिजाइन के किसी भी प्रदर्शन सीमित पहलू को "हैंड-ट्वीक" या मैन्युअल रूप से अनुकूलित करने की संभावना भी प्रदान करते हैं।

यह विशेष रूप से एक डिज़ाइन के लिए बुनियादी लॉजिक गेट्स, सर्किट या लेआउट का उपयोग करके डिज़ाइन किया गया है।

संरचित डिजाइन

संरचित एएसआईसी (ASIC) डिज़ाइन (जिसे "प्लेटफ़ॉर्म एएसआईसी (ASIC) डिज़ाइन" भी कहा जाता है) सेमीकंडक्टर उद्योग में एक अपेक्षाकृत नया चलन है, जिसके परिणामस्वरूप इसकी परिभाषा में कुछ बदलाव आया है। हालाँकि, एक संरचित एएसआईसी (ASIC) का मूल आधार यह है कि निर्माण चक्र समय और डिज़ाइन चक्र समय दोनों जो सेल-आधारित एएसआईसी की तुलना में कम हो गया है, क्योंकि पूर्व परिभाषित धातु परतें (इस प्रकार विनिर्माण समय को कम करना) और सिलिकॉन पर क्या है (इस प्रकार डिजाइन चक्र समय को कम करना) का पूर्व लक्षण वर्णन है।

एम्बेडेड सिस्टम की नींव से परिभाषा में कहा गया है कि:[7]

In a "structured ASIC" design, the logic mask-layers of a device are predefined by the ASIC vendor (or in some cases by a third party). Design differentiation and customization is achieved by creating custom metal layers that create custom connections between predefined lower-layer logic elements. "Structured ASIC" technology is seen as bridging the gap between field-programmable gate arrays and "standard-cell" ASIC designs. Because only a small number of chip layers must be custom-produced, "structured ASIC" designs have much smaller non-recurring expenditures (NRE) than "standard-cell" or "full-custom" chips, which require that a full mask set be produced for every design.

— Foundations of Embedded Systems

यह प्रभावी रूप से गेट सरणी के समान परिभाषा है। एक संरचित एएसआईसी (ASIC) को एक गेट सरणी से जो अलग करता है वह यह है कि एक गेट सरणी में, पूर्वनिर्धारित धातु की परतें विनिर्माण को तेजी से बदलने का काम करती हैं। एक संरचित एएसआईसी (ASIC) में, पूर्वनिर्धारित धातुकरण का उपयोग मुख्य रूप से मास्क सेट की लागत को कम करने के साथ-साथ डिजाइन चक्र के समय को काफी कम करने के लिए होता है।

उदाहरण के लिए, सेल आधारित या गेट ऐरे डिज़ाइन में उपयोगकर्ता को अक्सर पावर, क्लॉक और टेस्ट स्ट्रक्चर को स्वयं डिज़ाइन करना चाहिए। इसके विपरीत, ये अधिकांश संरचित एएसआईसी (ASIC) में पूर्वनिर्धारित होते हैं और इसलिए गेट ऐरे आधारित डिज़ाइनों की तुलना में डिज़ाइनर के लिए समय और खर्च बचा सकते हैं। इसी तरह, संरचित एएसआईसी (ASIC) के लिए उपयोग किए जाने वाले डिज़ाइन टूल सेल आधारित टूल की तुलना में काफी कम लागत और उपयोग में आसान (तेज़) हो सकते हैं, क्योंकि उन्हें वे सभी कार्य करने की आवश्यकता नहीं है जो सेल आधारित उपकरण करते हैं। कुछ मामलों में, संरचित एएसआईसी (ASIC) विक्रेता को अपने डिवाइस के लिए अनुकूलित टूल की आवश्यकता होती है (उदाहरण के लिए, कस्टम भौतिक संश्लेषण) का उपयोग किया जाए, और डिजाइन को और अधिक तेज़ी से निर्माण में लाने की अनुमति भी देता है।

सेल लाइब्रेरी, आईपी-आधारित डिज़ाइन, हार्ड और सॉफ्ट मैक्रोज़

तार्किक आदिम के सेल पुस्तकालय आमतौर पर डिवाइस निर्माता द्वारा सेवा के हिस्से के रूप में प्रदान किए जाते हैं। हालांकि उन्हें कोई अतिरिक्त लागत नहीं लगेगी, उनकी रिहाई एक गैर प्रकटीकरण समझौते (एनडीए NDA) की शर्तों द्वारा कवर की जाएगी और उन्हें निर्माता द्वारा बौद्धिक संपदा के रूप में माना जाएगा। आमतौर पर, उनके भौतिक डिज़ाइन को पूर्व परिभाषित किया जाएगा ताकि उन्हें "हार्ड मैक्रोज़" कहा जा सके।

अधिकांश इंजीनियर जिसे "बौद्धिक संपदा" समझते हैं, वे हैं आईपी कोर, ये डिज़ाइन किसी तीसरे पक्ष से बड़े एएसआईसी (ASIC) के उप घटकों के रूप में खरीदे गए हैं। उन्हें हार्डवेयर विवरण भाषा के रूप में प्रदान किया जा सकता है (जिसे अक्सर "सॉफ्ट मैक्रो" कहा जाता है), या पूरी तरह से रूटेड डिज़ाइन के रूप में जिसे सीधे एएसआईसी (ASIC) के मास्क पर प्रिंट किया जा सकता है (जिसे अक्सर "हार्ड मैक्रो" कहा जाता है)। कई संगठन अब ऐसे पूर्व-डिज़ाइन किए गए कोर सीपीयू, ईथरनेट, यूएसबी या टेलीफोन इंटरफेस बेचते हैं और बड़े संगठनों के पास शेष संगठन के लिए कोर तैयार करने के लिए एक संपूर्ण विभाग या प्रभाग हो सकता है। कंपनी एआरएम (एडवांस्ड आरआईएससी मशीन्स) केवल आईपी कोर बेचती है, जिससे यह एक सक्षम निर्माता बन जाता है।

वास्तव में, संरचित एएसआईसी (ASIC) डिजाइन में अब उपलब्ध कार्यों की विस्तृत श्रृंखला 1990 के दशक के अंत और 2000 के दशक की शुरुआत में इलेक्ट्रॉनिक्स में अभूतपूर्व सुधार का परिणाम है; एक कोर के रूप में बनाने में बहुत समय और निवेश लगता है, इसका पुन: उपयोग और आगे विकास उत्पाद चक्र के समय में नाटकीय रूप से कटौती करता है और बेहतर उत्पाद बनाता है। इसके अतिरिक्त, ओपन-सोर्स हार्डवेयर संगठन जैसे ओपन कोर मुफ्त आईपी कोर एकत्र कर रहे हैं, हार्डवेयर डिजाइन में ओपन सोर्स सॉफ्टवेयर आंदोलन के समानांतर।

सॉफ्ट मैक्रोज़ अक्सर प्रक्रिया से स्वतंत्र होते हैं (अर्थात उन्हें निर्माण प्रक्रियाओं और विभिन्न निर्माताओं की एक विस्तृत श्रृंखला पर गढ़ा जा सकता है)। हार्ड मैक्रोज़ प्रक्रिया-सीमित होते हैं और आमतौर पर आगे के डिज़ाइन प्रयासों को किसी भिन्न प्रक्रिया या निर्माता में माइग्रेट (पोर्ट) करने के लिए निवेश किया जाना चाहिए।

मल्टी-प्रोजेक्ट वेफर्स

कुछ निर्माता और आईसी (IC) डिज़ाइन हाउस कम लागत वाले प्रोटोटाइप प्राप्त करने की एक विधि के रूप में मल्टी प्रोजेक्ट वेफर सर्विस एमपीडब्लू (MPW) प्रदान करते हैं। अक्सर शटल कहा जाता है, ये एमपीडब्ल्यू, जिसमें कई डिज़ाइन होते हैं, "कट एंड गो" आधार पर नियमित, निर्धारित अंतराल पर चलते हैं, आमतौर पर निर्माता की ओर से सीमित देयता होती है। अनुबंध में बेयर डाइस की डिलीवरी या मुट्ठी भर उपकरणों की असेंबली और पैकेजिंग शामिल है। सेवा में आमतौर पर एक भौतिक डिज़ाइन डेटाबेस (यानी मास्किंग जानकारी या पैटर्न जनरेशन (पीजी PG टेप) की आपूर्ति शामिल होती है। प्रक्रिया में कम भागीदारी के कारण निर्माता को अक्सर "सिलिकॉन फाउंड्री" के रूप में जाना जाता है।

अनुप्रयोग-विशिष्ट मानक उत्पाद

एक अनुप्रयोग विशिष्ट मानक उत्पाद या एएसएसपी (ASSP) एक एकीकृत परिपथ है जो एक विशिष्ट कार्य को लागू करता है जो एक व्यापक बाजार के लिए अपील करता है। एएसआईसी (ASIC) के विपरीत जो कार्यों के संग्रह को जोड़ती है और ये एक ग्राहक द्वारा या उसके लिए डिज़ाइन किए गए हैं, एएसएसपी (ASSP)s शेल्फ घटकों के रूप में उपलब्ध हैं। ऑटोमोटिव से लेकर संचार तक सभी उद्योगों में एएसएसपी (ASSP) का उपयोग किया जाता है। एक सामान्य नियम के रूप में, यदि आप डेटा बुक में कोई डिज़ाइन पा सकते हैं, तो शायद यह एएसआईसी (ASIC) नहीं है, लेकिन कुछ अपवाद हैं। उदाहरण के लिए, दो आईसी जिन्हें एएसआईसी माना जा सकता है या नहीं, एक पीसी के लिए एक नियंत्रक चिप और एक मॉडेम के लिए एक चिप है। ये दोनों उदाहरण किसी एप्लिकेशन के लिए विशिष्ट हैं (जो एएसआईसी (ASIC) के लिए विशिष्ट है) लेकिन कई अलग-अलग सिस्टम विक्रेताओं को बेचे जाते हैं (जो मानक भागों के लिए विशिष्ट है)। एएसआईसी (ASIC) जैसे कि इन्हें कभी-कभी एप्लिकेशन विशिष्ट मानक उत्पाद (एएसएसपी -ASSP) कहा जाता है।

एएसएसपी (ASSP) के उदाहरण एन्कोडिंग/डिकोडिंग चिप, ईथरनेट नेटवर्क इंटरफेस कंट्रोलर चिप आदि हैं।

आईईईई (IEEE) एक एएसएसपी (ASSP) पत्रिका प्रकाशित करता था,[8] जिसे 1990 में आईईईई (IEEE) सिग्नल प्रोसेसिंग मैगज़ीन में बदल दिया गया था।

यह भी देखें

- आवेदन-विशिष्ट अनुदेश सेट प्रोसेसर (एएसआईपी ASIP)

- कॉम्प्लेक्स प्रोग्रामेबल लॉजिक डिवाइस (सीपीएलडी CPLD)

- इलेक्ट्रॉनिक डिजाइन स्वचालन (ईडीए EDA या ईसीएडी ECAD)

- फील्ड-प्रोग्रामेबल गेट एरे (एफपीजीए FPGA)

- मल्टी-प्रोजेक्ट चिप (एमपीसी MPC)

- बहुत बड़े पैमाने पर एकीकरण (वीएलएसआई VLSI)

- सिस्टम-ऑन-ए-चिप (एसओसी SOC)

- मुख्य रूप से हार्डवेयर में आधारित कंप्यूटिंग के अवलोकन के लिए हार्डवेयर त्वरण

संदर्भ

- ↑ 1.0 1.1 Barr, Keith (2007). ASIC Design in the Silicon Sandbox: A Complete Guide to Building Mixed-signal Integrated Circuits. New York: McGraw-Hill. ISBN 978-0-07-148161-8. OCLC 76935560.

- ↑ 2.0 2.1 2.2 2.3 "1967: Application Specific Integrated Circuits employ Computer-Aided Design". The Silicon Engine. Computer History Museum. Retrieved 9 November 2019.

- ↑ Lipp, Bob oral history. 14 February 2017. Retrieved 2018-01-28.

{{cite book}}:|website=ignored (help) - ↑ "People". The Silicon Engine. Computer History Museum. Retrieved 2018-01-28.

- ↑ 5.0 5.1 Smith, Michael John Sebastian (1997). Application-Specific Integrated Circuits. Addison-Wesley Professional. ISBN 978-0-201-50022-6.

- ↑ Hurley, Jaden Mclean & Carmen. (2019). Logic Design. EDTECH. ISBN 978-1-83947-319-7. OCLC 1132366891.

- ↑ Barkalov, Alexander; Titarenko, Larysa; Mazurkiewicz, Małgorzata (2019). Foundations of Embedded Systems. Studies in Systems, Decision and Control (in English). Vol. 195. Cham: Springer International Publishing. doi:10.1007/978-3-030-11961-4. ISBN 9783030119607. S2CID 86596100.

- ↑ IEEE ASSP Issue 2, Part 1 – April 1984

सूत्रों का कहना है

- Barr, Keith (2007). ASIC Design in the Silicon Sandbox: A Complete Guide to Building Mixed-Signal Integrated Circuits. McGraw Hill Professional. ISBN 978-0-07-148161-8.

- Anthony Cataldo (26 March 2002). "Xilinx looks to ease path to custom FPGAs". EE Times. CMP Media, LLC. Archived from the original on 29 September 2007. Retrieved 14 December 2006.

- "Xilinx intros next-gen EasyPath FPGAs priced below structured ASICs". EDP Weekly's IT Monitor. Millin Publishing, Inc. 18 October 2004.

- Golshan, K. (2007). Physical design essentials: an ASIC design implementation perspective. New York: Springer. ISBN 978-0-387-36642-5.

बाहरी संबंध

Media related to Application-specific integrated circuits at Wikimedia Commons

Media related to Application-specific integrated circuits at Wikimedia Commons

]