माइक्रोआर्किटेक्चर

कंप्यूटर इंजीनियरिंग में, माइक्रोआर्किटेक्चर , जिसे कंप्यूटर संगठन भी कहा जाता है और कभी-कभी इसे μarch या uarch के रूप में संक्षिप्त किया जाता है, विशेष केंद्रीय प्रसंस्करण इकाई में दिए गए निर्देश सेट आर्किटेक्चर ( आईएसए) को प्रयुक्त करने का विधि है।[1] किसी दिए गए आईएसए को विभिन्न माइक्रोआर्किटेक्चर के साथ कार्यान्वित किया जा सकता है;[2][3] किसी दिए गए डिज़ाइन के विभिन्न लक्ष्यों या प्रौद्योगिकी में परिवर्तन के कारण कार्यान्वयन भिन्न हो सकते हैं।[4]

इस प्रकार से कंप्यूटर आर्किटेक्चर माइक्रोआर्किटेक्चर और इंस्ट्रक्शन सेट आर्किटेक्चर का संयोजन है।

निर्देश सेट आर्किटेक्चर से संबंध

इंस्ट्रक्शन सेट आर्किटेक्चर सामान्यतः प्रोसेसर के प्रोग्रामिंग मॉडल के समान है जैसा कि असेंबली लैन्गवेग प्रोग्रामर या कंपाइलर लेखक द्वारा देखा जाता है। इस प्रकार से आईएसए में अन्य चीजों के अतिरिक्त इंस्ट्रक्शन सेट आर्किटेक्चर या निर्देश, निष्पादन मॉडल, प्रोसेसर रजिस्टर, पता और डेटा प्रारूप भी सम्मिलित हैं। किन्तु माइक्रोआर्किटेक्चर में प्रोसेसर के घटक भाग सम्मिलित होते हैं और ये आईएसए को प्रयुक्त करने के लिए कैसे आपस में जुड़ते हैं और कैसे संचालित होते हैं।

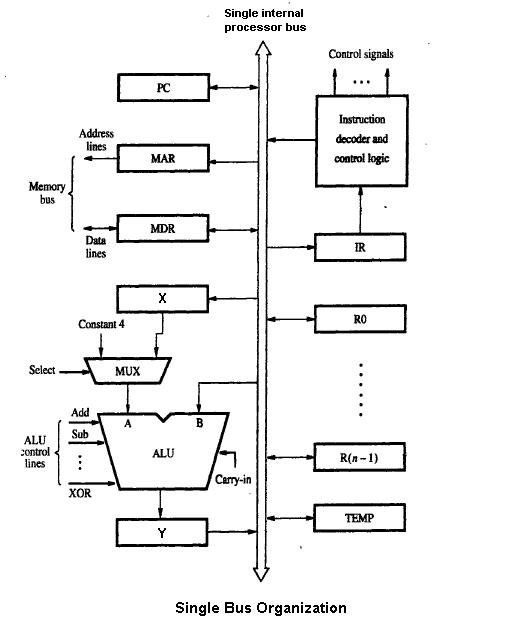

चूंकि किसी मशीन के माइक्रोआर्किटेक्चर को सामान्यतः (अधिक या कम विस्तृत) आरेखों के रूप में दर्शाया जाता है जो की मशीन के विभिन्न माइक्रोआर्किटेक्चर ल मूल के अंतर्संबंधों का वर्णन करता है, जो एकल गेट और रजिस्टर से लेकर अंकगणितीय तर्क इकाइयों (एएलयू) और यहां उससे भी उच्च मूल को पूर्ण करने के लिए कुछ भी हो सकता है। मूल ये आरेख सामान्यतः डेटापथ (जहां डेटा रखा जाता है) और नियंत्रण पथ (जिसे डेटा को चलाने के लिए कहा जा सकता है) को अलग करते हैं।[5]

अतः सिस्टम को डिज़ाइन करने वाला व्यक्ति सामान्यतः विशिष्ट माइक्रोआर्किटेक्चर को प्रकार के डेटा प्रवाह आरेख के रूप में खींचता है। और ब्लॉक आरेख की तरह, माइक्रोआर्किटेक्चर आरेख अंकगणित और तर्क इकाई और फ़ाइल पंजीकृत करें जैसे माइक्रोआर्किटेक्चर ल मूल को एकल योजनाबद्ध प्रतीक के रूप में दिखाता है। सामान्यतः , आरेख उन मूल को तीरों, मोटी रेखाओं और पतली रेखाओं से जोड़ता है जिससे तीन-राज्य बसों (जिनके लिए बस को चलाने वाले प्रत्येक उपकरण के लिए तीन-राज्य बफर की आवश्यकता होती है), यूनिडायरेक्शनल (सदैव स्रोत द्वारा संचालित, जैसे) के मध्य अंतर करने के लिए तीरों, मोटी रेखाओं और पतली रेखाओं से जोड़ता है। चूंकि एकल स्रोत, जैसे कि सरल कंप्यूटरों पर एड्रेस बस सदैव मेमोरी एड्रेस रजिस्टर द्वार संचालित होती है), और व्यक्तिगत नियंत्रण रेखाए द्वारा संचालित होती है। इस प्रकार से अधि सरल कंप्यूटरों में डेटापथ या डेटापथ का एकल बस संगठन होता है – उनके पास ही तीन-राज्य बस है। अधिक समिष्ट कंप्यूटरों का आरेख सामान्यतः कई तीन-स्तर बसें दिखाता है, जो की मशीन के साथ अधिक संचालन करने में सहायता करती हैं।

जिससे प्रत्येक माइक्रोआर्किटेक्चर ल मूल को इसे प्रयुक्त करने के लिए उपयोग किए जाने वाले तर्क द्वारा के अंतर्संबंधों का वर्णन करने वाले योजनाबद्ध विधि से दर्शाया गया है। और प्रत्येक लॉजिक गेट को परिपथ आरेख द्वारा दर्शाया जाता है जो कुछ विशेष लॉजिक वर्ग में इसे प्रयुक्त करने के लिए उपयोग किए जाने वाले ट्रांजिस्टर के कनेक्शन का वर्णन करता है। विभिन्न माइक्रोआर्किटेक्चर वाली मशीनों में समान निर्देश सेट आर्किटेक्चर हो सकता है, और इस प्रकार वे समान प्रोग्राम निष्पादित करने में सक्षम हो सकते हैं। जिससे अर्धचालक निर्माण में प्रगति के साथ-साथ नए माइक्रोआर्किटेक्चर और/या परिपथरी समाधान, नई पीढ़ियों के प्रोसेसर को समान आईएसए का उपयोग करते हुए उच्च प्रदर्शन प्राप्त करने की अनुमति देते हैं।

अतः सिद्धांत रूप में, एकल माइक्रोआर्किटेक्चर माइक्रोकोड या राइटेबल कंट्रोल स्टोर्स में केवल समान परिवर्तन के साथ अनेक अलग-अलग आईएसए निष्पादित कर सकता है।

दृष्टिकोण

इस प्रकार से निर्देश पाइपलाइन डेटापथ वर्तमान समय में माइक्रोआर्किटेक्चर में सबसे अधिक उपयोग किया जाने वाला डेटापथ डिज़ाइन है। इस विधियों का उपयोग अधिकांश आधुनिक माइक्रोप्रोसेसरों, माइक्रोकंट्रोलर और डिजिटल सिग्नल प्रोसेसर में किया जाता है। पाइपलाइनयुक्त आर्किटेक्चर असेंबली लाइन की तरह कई निर्देशों को निष्पादन में ओवरलैप करने की अनुमति देता है। अर्थात पाइपलाइन में कई अलग-अलग चरण सम्मिलित हैं जो की माइक्रोआर्किटेक्चर डिज़ाइन में मौलिक हैं।[5] इनमें से कुछ चरणों में निर्देश लाना, निर्देश डिकोड करना, निष्पादित करना और वापस लिखना सम्मिलित किया गया है। कुछ आर्किटेक्चर में मेमोरी एक्सेस जैसे अन्य चरण सम्मिलित होते हैं। अतः पाइपलाइनों का डिज़ाइन केंद्रीय सूक्ष्म आर्किटेक्चर कार्यों में से है।

निष्पादन इकाइयाँ माइक्रोआर्किटेक्चर के लिए भी आवश्यक हैं। और निष्पादन इकाइयों में अंकगणितीय तर्क इकाइयाँ (एएलयू) फ़्लोटिंग पॉइंट इकाई इकाइयाँ (एफपीयू), लोड/स्टोर इकाइयाँ, शाखा पूर्वानुमान और एकल निर्देश, एकाधिक डेटा सम्मिलित हैं। ये इकाइयाँ प्रोसेसर का संचालन या गणना करती हैं। निष्पादन इकाइयों की संख्या, उनकी विलंबता और थ्रूपुट का चुनाव केंद्रीय माइक्रोआर्किटेक्चर ल डिज़ाइन कार्य है। सिस्टम के अन्दर विचरो का आकार, विलंबता, थ्रूपुट और कनेक्टिविटी भी सूक्ष्म आर्किटेक्चर निर्णय हैं।

चूंकि सिस्टम-स्तरीय डिज़ाइन निर्णय जैसे कि मेमोरी नियंत्रक जैसे बाह्य उपकरणों को सम्मिलित करना है या नहीं, इसलिए माइक्रोआर्किटेक्चर ल डिज़ाइन प्रक्रिया का भाग माना जा सकता है। इसमें इन बाह्य उपकरणों के प्रदर्शन-स्तर और कनेक्टिविटी पर निर्णय सम्मिलित हैं।

आर्किटेक्चर डिज़ाइन के विपरीत, जहां विशिष्ट प्रदर्शन स्तर प्राप्त करना मुख्य लक्ष्य है, माइक्रोआर्किटेक्चर ल डिज़ाइन अन्य बाधाओं पर अधिक ध्यान देता है। चूंकि माइक्रोआर्किटेक्चर डिज़ाइन निर्णय सिस्टम में जो कुछ भी होता है उसे सीधे प्रभावित करते हैं, चिप क्षेत्र/निवेश , विद्युत की खपत, तर्क समिष्टतः , कनेक्टिविटी में सरलता , विनिर्माण क्षमता, डिबगिंग में सरलता और परीक्षण क्षमता जैसे नियम पर ध्यान दिया जाना चाहिए।

सूक्ष्म आर्किटेक्चर अवधारणाएँ

निर्देश चक्र

इस प्रकार से प्रोग्राम चलाने के लिए, सभी सिंगल- या मल्टी-चिप सीपीयू:

- निर्देश पढ़ें और उसे डिकोड करें

- निर्देश को संसाधित करने के लिए आवश्यक कोई भी संबद्ध डेटा खोजे

- निर्देश पर कार्रवाई करें

- परिणाम लिखें

इस प्रकार विद्युत विवृत होने तक निर्देश चक्र निरंतर दोहराया जाता है।

मल्टीसाइकल माइक्रोआर्किटेक्चर

ऐतिहासिक रूप से, प्रारंभिक कंप्यूटर मल्टीसाइकल डिज़ाइन वाले थे। सबसे लघु , कम-बहुमूल्य कंप्यूटर प्रायः अभी भी इस विधियों का उपयोग करते हैं। और मल्टीसाइकिल आर्किटेक्चर प्रायः तर्क मूल की कुल संख्या और उचित मात्रा में शक्ति का उपयोग करते हैं। उन्हें नियतात्मक समय और उच्च विश्वसनीयता के लिए डिज़ाइन किया जा सकता है। विशेष रूप से, नियमबद्ध शाखाएँ या व्यवधान लेते समय उनके पास रुकने के लिए कोई पाइपलाइन नहीं होती है। चूंकि , अन्य माइक्रोआर्किटेक्चर प्रायः समान तर्क वर्ग का उपयोग करके प्रति यूनिट समय में अधिक निर्देश निष्पादित करते हैं। इस प्रकार से उत्तम प्रदर्शन पर चर्चा करते समय, सुधार प्रायः मल्टीसाइकिल डिज़ाइन से संबंधित होता है।

मल्टीसाइकिल कंप्यूटर में, कंप्यूटर घड़ी के कई चक्रों में क्रम से चार चरण करता है। कुछ डिज़ाइन वैकल्पिक घड़ी किनारों पर क्रमिक चरणों को पूर्ण करके दो घड़ी चक्रों में अनुक्रम निष्पादित कर सकते हैं, संभवतः मुख्य चक्र के बाहर होने वाले लंबे संचालन के साथ उपयोग किया जाता है । इस प्रकार उदाहरण के लिए, प्रथम चक्र के बढ़ते किनारे पर प्रथम चरण, प्रथम चक्र के गिरते किनारे पर दूसरा चरण, आदि।

इस प्रकार से नियंत्रण तर्क में, चक्र काउंटर, चक्र स्थिति (उच्च या निम्न) और निर्देश डिकोड रजिस्टर के बिट्स का संयोजन यह निर्धारित करता है कि कंप्यूटर के प्रत्येक भाग को क्या करना चाहिए। किन्तु नियंत्रण तर्क को डिज़ाइन करने के लिए, प्रत्येक निर्देश के प्रत्येक चक्र में कंप्यूटर के प्रत्येक भाग के नियंत्रण संकेतों का वर्णन करने वाली बिट्स की श्रेणी बना सकते हैं। जिससे फिर, इस तर्क तालिका का परीक्षण सॉफ़्टवेयर सिमुलेशन रनिंग टेस्ट कोड में किया जा सकता है। यदि लॉजिक टेबल को मेमोरी में रखा जाता है और वास्तव में वास्तविक कंप्यूटर चलाने के लिए उपयोग किया जाता है, तो इसे माइक्रोप्रोग्राम कहा जाता है। कुछ कंप्यूटर डिज़ाइनों में, लॉजिक टेबल को लॉजिक गेट्स से बने कॉम्बिनेशन लॉजिक के रूप में अनुकूलित किया जाता है, सामान्यतः कंप्यूटर प्रोग्राम का उपयोग किया जाता है जो लॉजिक को अनुकूलित करता है। प्रारंभिक कंप्यूटरों ने नियंत्रण के लिए तदर्थ तर्क डिजाइन का उपयोग किया और इसे जब तक कि मौरिस विल्केस ने इस सारणीबद्ध दृष्टिकोण माइक्रोप्रोग्रामिंग का आविष्कार नहीं किया था ।[6]

निष्पादन गति बढ़ाना

चरणों की इस सरल दिखने वाली श्रृंखला को समिष्ट बनाने वाला तथ्य यह है कि मेमोरी पदानुक्रम, जिसमें कैश (कंप्यूटिंग), मुख्य मेमोरी और हार्ड डिस्क (जहां प्रोग्राम निर्देश और डेटा रहते हैं) जैसे गैर-वाष्पशील स्टोरेज सम्मिलित हैं, और सदैव प्रोसेसर की तुलना में धीमा रहा है । चरण (2) प्रायः कंप्यूटर बस पर डेटा पहुंचने में लंबी (सीपीयू शब्दों में) देरी का परिचय देता है। डिज़ाइनों में अधिक मात्रा में शोध किया गया है जिससे यथासंभव इन देरी से बचा जा सकता है । कुछ वर्षों में, केंद्रीय लक्ष्य समानांतर में अधिक निर्देशों को निष्पादित करना था, इस प्रकार प्रोग्राम की प्रभावी निष्पादन गति को बढ़ाना है। इन प्रयासों ने समिष्ट तर्क और परिपथ संरचनाएं प्रस्तुत कीं गई है । प्रारंभ में, इन विधियों के लिए आवश्यक परिपथरी की मात्रा के कारण इन विधियों को केवल बहुमूल्य मेनफ्रेम या सुपर कंप्यूटर पर ही प्रयुक्त किया जा सकता था। जैसे-जैसे अर्धचालक निर्माण में प्रगति हुई, इनमें से अधिक से अधिक विधियों को एकल अर्धचालक चिप पर प्रयुक्त किया जा सकता है। मूर का नियम देखें.

निर्देश सेट विकल्प

इस प्रकार से पिछले कुछ वर्षों में निर्देश सेट मूल रूप से अधिक सरल से कभी-कभी अधिक समिष्ट (विभिन्न स्तिथियों में) में परिवर्तित हो गए हैं। वर्तमान समय में, लोड-स्टोर आर्किटेक्चर, अधिक लंबे निर्देश शब्द और स्पष्ट रूप से समानांतर निर्देश कंप्यूटिंग प्रकार विधान में रहे हैं। आर्किटेक्चर जो डेटा समानता से निपट रहे हैं उनमें एकल निर्देश, एकाधिक डेटा और वेक्टर प्रोसेसर सम्मिलित हैं। सीपीयू आर्किटेक्चर की कक्षाओं को दर्शाने के लिए उपयोग किए जाने वाले कुछ लेबल विशेष रूप से वर्णनात्मक नहीं हैं, खासकर सीआईएससी लेबल; पूर्वप्रभावी रूप से समिष्ट अनुदेश सेट कंप्यूटर को दर्शाने वाले कई प्रारंभिक डिज़ाइन वास्तव में आधुनिक आरआईएससी प्रोसेसर (कई स्तिथियों में) की तुलना में अधिक सरल हैं।

चूंकि , निर्देश सेट आर्किटेक्चर का चुनाव उच्च-प्रदर्शन वाले उपकरणों को प्रयुक्त करने की समिष्टतः को अधिक प्रभावित कर सकता है। अर्थात पहले आरआईएससी प्रोसेसर को विकसित करने के लिए उपयोग की जाने वाली प्रमुख रणनीति, उच्च एन्कोडिंग नियमितता और सरलता के साथ संयुक्त रूप से न्यूनतम व्यक्तिगत अर्थ संबंधी समिष्टतः के निर्देशों को सरल बनाना था। इस प्रकार के समान निर्देश सरलता से प्राप्त किए गए है , इसके अतिरिक्त डिकोड किए गए और पाइपलाइन विधि से निष्पादित किए गए और उच्च परिचालन आवृत्तियों तक पहुंचने के लिए तर्क स्तरों की संख्या को कम करने की सरल रणनीति थी; निर्देश कैश-मेमोरीज़ को उच्च ऑपरेटिंग आवृत्ति और स्वाभाविक रूप से कम कोड घनत्व के लिए मुआवजा दिया गया था, जबकि उच्च रजिस्टर सेट का उपयोग जितना संभव हो उतना (धीमी) मेमोरी एक्सेस को फैक्टर करने के लिए किया गया था।

निर्देश पाइपलाइनिंग

इस प्रकार से प्रदर्शन को उत्तम बनाने की प्रथम और अधिक शक्तिशाली विधियों में से है जो की अनुदेश पाइपलाइनिंग का उपयोग है । और प्रारंभिक प्रोसेसर डिज़ाइन अगले निर्देश पर जाने से प्रथम निर्देश के लिए उपरोक्त सभी चरणों को पूर्ण करते है । परिपथरी के उच्च भागो को किसी चरण पर निष्क्रिय छोड़ दिया गया था; अतः उदाहरण के लिए, निर्देश डिकोडिंग परिपथरी निष्पादन आदि के समय निष्क्रिय रहेगी।

चूंकि पाइपलाइनिंग कई निर्देशों को एक ही समय में प्रोसेसर के माध्यम से कार्य करने की अनुमति देकर प्रदर्शन में सुधार करती है। उसी मूल उदाहरण में, प्रोसेसर नए निर्देश को डीकोड करना प्रारंभ कर देगा (चरण 1) जबकि अंतिम निर्देश परिणाम की प्रतीक्षा कर रहा था। यह समय में अधिकतम चार निर्देशों को "उड़ान में" की अनुमति देता है , जिससे प्रोसेसर चार गुना तीव्र दिखेगा। चूंकि किसी भी निर्देश को पूर्ण होने में उतना ही समय लगता है (अभी भी चार चरण हैं) कुल मिलाकर सीपीयू अधिक तीव्र से निर्देशों को समाप्त कर देता है।

अतः श्रेष्ट आरआईएससी निर्देश प्रक्रिया के प्रत्येक चरण को सावधानीपूर्वक अलग करके और उन्हें समान समय चक्र बनाकर पाइपलाइनों को लघु निर्माण करना अधिक सरल बनाता है। और संपूर्ण प्रोसेसर समनुक्रम विधान में काम करता है, जिसमें निर्देश एक ओर से आते हैं और परिणाम दूसरी ओर से आते हैं। उत्कृष्ट आरआईएससी पाइपलाइन की कम समिष्टतः के कारण, पाइपलाइनयुक्त कोर और निर्देश कैश को ही आकार के डाई पर रखा जा सकता है जो की अन्यथा सीआईएससी डिजाइन पर अकेले कोर को फिट करता है । यही वास्तविक कारण था कि आरआईएससी तीव्र था। स्पार्क और एमआईपीएस आर्किटेक्चर जैसे प्रारंभिक डिज़ाइन प्रायः समान क्लॉक स्पीड और मूल्य पर इंटेल और मोटोरोला सीआईएससी समाधानों की तुलना में 10 गुना अधिक तीव्र चलते थे।

चूंकि पाइपलाइनें किसी भी प्रकार से आरआईएससी डिज़ाइन तक सीमित नहीं हैं। किन्तु 1986 तक टॉप-ऑफ़-द-लाइन वीएएक्स कार्यान्वयन (वीएएक्स 8000) हैवी पाइपलाइन डिज़ाइन था, जो पहले वाणिज्यिक एमआईपीएस और स्पार्क डिज़ाइनों से थोड़ा पहले का था। अधिकांश आधुनिक सीपीयू (यहां तक कि एम्बेडेड सीपीयू) अब पाइपलाइन में हैं, और बिना पाइपलाइन वाले माइक्रोकोडेड सीपीयू केवल सबसे अधिक क्षेत्र-बाधित एम्बेडेड प्रोसेसर में देखे जाते हैं। वीएएक्स 8800 से लेकर आधुनिक पेंटियम 4 और एथलॉन तक उच्च सीआईएससी मशीनें, माइक्रोकोड और पाइपलाइन दोनों के साथ कार्यान्वित की जाती हैं। पाइपलाइनिंग और कैशिंग में सुधार दो प्रमुख माइक्रोआर्किटेक्चर ल प्रगति हैं जिन्होंने प्रोसेसर के प्रदर्शन को परिपथ विधियों के साथ सामंजस्य बनाए रखने में सक्षम बनाया है जिस पर वे आधारित हैं।

कैश

इस प्रकार से चिप निर्माण में उन्नति से अधिक समय नहीं बीता है जब डाई पर और भी अधिक परिपथरी लगाने की अनुमति मिल गई है और डिजाइनरों ने इसका उपयोग करने के विधियों की खोज प्रारंभ कर दी है । अधिक सरल में से ऑन-डाई सीपीयू कैश की बढ़ती मात्रा को जोड़ना था। और कैश अधिक तीव्र और बहुमूल्य मेमोरी है। इसे मुख्य मेमोरी से संवाद करने के लिए आवश्यक कई चक्रों के विपरीत कुछ चक्रों में ही एक्सेस किया जा सकता है। सीपीयू में कैश नियंत्रक सम्मिलित होता है जो कैश से पढ़ने और लिखने को स्वचालित करता है। यदि डेटा पहले से ही कैश में है तो इसे वहां से एक्सेस किया जा सकता है जिससे अधिक समय की बचत होती है, जबकि ऐसा नहीं है तब कैश नियंत्रक द्वारा इसे पढ़ते समय प्रोसेसर रुक जाता है।

अतः आरआईएससी डिज़ाइनों ने 1980 के दशक के मध्य से अंत तक कैश जोड़ना प्रारंभ किया, प्रायः कुल मिलाकर केवल 4 केबी समय के साथ यह संख्या बढ़ती गई, और सामान्य सीपीयू में अब कम से कम 2 एमबी होते हैं, जबकि अधिक शक्तिशाली सीपीयू 4 या 6 या 12 एमबी या यहां तक कि 32 एमबी या उससे अधिक के साथ आते हैं, जिनमें से सबसे अधिक 768 एमबी नई जारी ईपीवाईसी मिलान-एक्स लाइन में है, जो कि आयोजित किया गया है। मेमोरी पदानुक्रम. सामान्यतः , कम रुकावट के कारण अधिक कैश का अर्थ है और कम रुकावट के कारण अधिक प्रदर्शन है।

इस प्रकार से कैश और पाइपलाइन दूसरे से अधिक मेल खाते थे। अतः , ऐसी पाइपलाइन बनाने का कोई तथ्य नहीं था जो की ऑफ-चिप मेमोरी की एक्सेस विलंबता से तीव्र चल सकती है । इसके अतिरिक्त ऑन-चिप कैश मेमोरी का उपयोग करने का तथ्य है कि पाइपलाइन कैश एक्सेस विलंबता की गति से चल सकती है, जो समय की अधिक लघु लंबाई है। इससे प्रोसेसर की ऑपरेटिंग आवृत्तियों को ऑफ-चिप मेमोरी की तुलना में अधिक तीव्र दर से बढ़ने की अनुमति मिली है ।

शाखा पूर्वानुमान

निर्देश-स्तरीय समानता के माध्यम से उच्च प्रदर्शन प्राप्त करने में बाधा शाखाओं के कारण पाइपलाइन स्टालों और निस्तब्धता से उत्पन्न होती है। सामान्यतः , नियमबद्ध शाखा ली जाएगी या नहीं, यह पाइपलाइन में देर तक ज्ञात नहीं होता है क्योंकि नियमबद्ध शाखाएं रजिस्टर से आने वाले परिणामों पर निर्भर करती हैं। उस समय से जब प्रोसेसर के निर्देश डिकोडर को पता चला है कि उसे नियमबद्ध शाखा निर्देश का सामना करना पड़ा है, उस समय तक जब निर्णायक रजिस्टर मान को पढ़ा जा सकता है, पाइपलाइन को अनेक चक्रों के लिए रोकना होगा, या यदि ऐसा नहीं है और शाखा ले ली गई है, चुकी पाइपलाइन को निस्तब्धता करने की आवश्यकता है। जैसे-जैसे घड़ी की गति बढ़ती है, पाइपलाइन की गहराई भी इसके साथ बढ़ती है, और कुछ आधुनिक प्रोसेसर में 20 चरण या अधिक हो सकते हैं। औसतन, निष्पादित प्रत्येक पांचवां निर्देश शाखा है, इसलिए बिना किसी हस्तक्षेप के यह अधिक सीमा तक रुका हुआ है।

इस प्रकार से शाखा दंडों को कम करने के लिए शाखा पूर्वानुमान और सट्टा निष्पादन जैसी विधियों का उपयोग किया जाता है। शाखा पूर्वानुमान वह है जहां हार्डवेयर शिक्षित अनुमान लगाता है कि कोई विशेष शाखा ली जाएगी या नहीं, वास्तव में शाखा के पक्ष या दूसरे पक्ष को दूसरे पक्ष की तुलना में अधिक बार बुलाया जाता है। आधुनिक डिज़ाइनों में समिष्ट सांख्यिकीय पूर्वानुमान प्रणालियाँ होती हैं, जो अधिक स्पष्ट रूप से वर्तमान में पूर्वानुमान करने के लिए पिछली शाखाओं के परिणामों को दर्शाती हैं। अनुमान हार्डवेयर को रजिस्टर पढ़ने की प्रतीक्षा किए बिना निर्देशों को प्रीफ़ेच करने की अनुमति देता है। सट्टा निष्पादन और संवर्द्धन है जिसमें पूर्वानुमानित पथ के साथ कोड को न केवल प्रीफ़ेच किया जाता है किन्तु यह ज्ञात होने के पश्चात भी निष्पादित किया जाता है कि शाखा ली जानी चाहिए या नहीं, अनुमान ठीक होने पर यह उत्तम प्रदर्शन प्रदान कर सकता है, इस प्रकार से अनुमान व्यर्थ होने पर हैवी जुर्माने की कठिनाई हो सकती है क्योंकि निर्देशों को पूर्ववत करने की आवश्यकता होती है।

सुपरस्केलर

ऊपर उल्लिखित अवधारणाओं का समर्थन करने के लिए आवश्यक सभी अतिरिक्त समष्टि और गेटों के साथ भी अर्धचालक निर्माण में सुधार ने शीघ्र ही और भी अधिक लॉजिक गेटों का उपयोग करने की अनुमति दी है।

उपरोक्त रूपरेखा में प्रोसेसर समय में ही निर्देश के कुछ भागो को संसाधित करता है। यदि अनेक निर्देशों को साथ संसाधित किया जाए तब यह कंप्यूटर प्रोग्राम तीव्र से निष्पादित हो सकते हैं। और एएलयू जैसी कार्यात्मक इकाइयों की कॉपी करके, सुपरस्केलर प्रोसेसर प्राप्त करते हैं। कार्यात्मक इकाइयों की प्रतिकृति केवल तब संभव होती है जब एकल-इश्यू प्रोसेसर का डाई क्षेत्र विश्वसनीय रूप से निर्मित की जा सकने वाली चीज़ों की सीमा को नहीं बढ़ाता है । अतः 1980 के दशक के अंत तक, सुपरस्केलर डिज़ाइन बाज़ार में आने लगे थे ।

आधुनिक डिज़ाइनों में दो लोड इकाइयाँ, स्टोर (कई निर्देशों को संग्रहीत करने के लिए कोई परिणाम नहीं होता), दो या अधिक पूर्णांक गणित इकाइयाँ, दो या अधिक फ़्लोटिंग पॉइंट इकाइयाँ, और प्रायः एकल निर्देश, किसी प्रकार की एकाधिक डेटा इकाई मिलना समान रूप है। इस प्रकार से मेमोरी से निर्देशों की विशाल सूची को पढ़ने और उन्हें उस बिंदु पर निष्क्रिय विभिन्न निष्पादन इकाइयों को सौंपने से निर्देश प्राप्त करने का तर्क समिष्टतः में बढ़ता है। फिर परिणाम एकत्र किए जाते हैं और अंत में पुनः व्यवस्थित किए जाते हैं।

आउट-ऑफ़-ऑर्डर निष्पादन

अर्थात कैश को जोड़ने से मेमोरी पदानुक्रम से डेटा प्राप्त होने की प्रतीक्षा के कारण स्टालों की आवृत्ति या अवधि घट जाती है, किन्तु इन स्टालों से पूर्ण रूप से छुटकारा नहीं मिलता है। प्रारंभिक डिज़ाइनों में कैश मिस होने से कैश नियंत्रक को प्रोसेसर को रोकने और प्रतीक्षा करने के लिए बाध्य होना पड़ता था। निःसंदेह प्रोग्राम में कुछ अन्य निर्देश भी हो सकते हैं जिनका डेटा उस समय कैश में उपलब्ध होता है। और आउट-ऑफ़-ऑर्डर निष्पादन उस तैयार निर्देश को संसाधित करने की अनुमति देता है जबकि उच्च निर्देश कैश पर प्रतीक्षा करता है, फिर परिणामों को पुनः आदेश देता है जिससे यह प्रतीत होता है कि सभी प्रकार के प्रोग्राम किए गए क्रम में हुआ है । इस विधियों का उपयोग अन्य ऑपरेंड निर्भरता स्टालों से सुरक्षित करने के लिए भी किया जाता है, जैसे लंबी विलंबता फ़्लोटिंग-पॉइंट ऑपरेशन या अन्य बहु-चक्र संचालन से परिणाम की प्रतीक्षा करने वाला निर्देश है ।

नामांतरण रजिस्टर

रजिस्टर का नाम परिवर्तित करके ऐसी विधियों को संदर्भित करता है जिसका उपयोग उन निर्देशों द्वारा समान रजिस्टरों के पुन: उपयोग के कारण प्रोग्राम निर्देशों के अनावश्यक क्रमबद्ध निष्पादन से सुरक्षित करने के लिए किया जाता है। मान लीजिए कि हमारे पास निर्देश के दो समूह हैं जो समान प्रोसेसर रजिस्टर का उपयोग करते है । रजिस्टर को दूसरे सेट पर छोड़ने के लिए निर्देशों के सेट को पहले निष्पादित किया जाता है, किन्तु यदि दूसरे सेट को अलग समान रजिस्टर को सौंपा जाता है, तो निर्देशों के दोनों सेटों को समानांतर (या) श्रृंखला में निष्पादित किया जा सकता है।

मल्टीप्रोसेसिंग और मल्टीथ्रेडिंग

इस प्रकार से सीपीयू ऑपरेटिंग आवृत्तियों और गतिशील रैंडम-एक्सेस मेमोरी एक्सेस समय में बढ़ते बेमेल के कारण कंप्यूटर आर्किटेक्ट स्तब्ध हो गए हैं। प्रोग्राम के अन्दर अनुदेश-स्तर समानता (आईएलपी) का लाभ उठाने वाली कोई भी विधियों मुख्य मेमोरी से डेटा लाने पर होने वाली लंबी रुकावटों की भरपाई नहीं कर सकती है । इसके अतिरिक्त, अधिक उन्नत आईएलपी विधियों के लिए आवश्यक उच्च ट्रांजिस्टर गणना और उच्च परिचालन आवृत्तियों के लिए विद्युत अपव्यय स्तर की आवश्यकता होती है जिसे अब सरलता से ठंडा नहीं किया जा सकता है। इन कारणों से, कंप्यूटर की नई पीढ़ियों ने एकल प्रोग्राम या थ्रेड (कंप्यूटिंग) के बाहर उपस्तिथ समानता के उच्च स्तर का लाभ उठाना प्रारंभ कर दिया है।

इस प्रवृत्ति को कभी-कभी थ्रूपुट कंप्यूटिंग के रूप में जाना जाता है। यह विचार मेनफ्रेम बाजार में उत्पन्न हुआ जहां ओएलटीपी ने न केवल लेनदेन की निष्पादन गति पर बल दिया है किन्तु उच्च संख्या में लेनदेन से समाप्त करने की क्षमता पर भी बल दिया है । पिछले दशक में नेटवर्क रूटिंग और वेब-साइट सेवा जैसे लेनदेन-आधारित अनुप्रयोगों में अधिक वृद्धि हुई है, कंप्यूटर उद्योग ने क्षमता और थ्रूपुट नियम पर पुनः बल दिया है।

यह समानता से कैसे प्राप्त की जाती है इसकी विधियों बहु सिस्टम, कई सीपीयू वाले कंप्यूटर सिस्टम के माध्यम से है। बार हाई-एंड मेनफ़्रेम कंप्यूटर और सुपर कंप्यूटर के लिए आरक्षित होने के पश्चात् , छोटे मापदंड के (2-8) मल्टीप्रोसेसर सर्वर छोटे व्यवसाय बाजार के लिए समान हो गए हैं। उच्च निगमों के लिए, उच्च मापों (16-256) मल्टीप्रोसेसर आम हैं। यहां तक कि कई सीपीयू वाले निजी कंप्यूटर भी 1990 के दशक से सामने आए हैं।

अर्धचालक प्रौद्योगिकी प्रगति के साथ ट्रांजिस्टर आकार में और कटौती उपलब्ध होने के साथ, मल्टी-कोर प्रोसेसर मल्टी-कोर सीपीयू सामने आए हैं जहां ही सिलिकॉन चिप पर कई सीपीयू प्रयुक्त किए जाते हैं। प्रारंभ में एम्बेडेड बाजारों को लक्षित करने वाले चिप्स में उपयोग किया जाता था, जहां सरल और छोटे सीपीयू सिलिकॉन के टुकड़े पर कई इंस्टेंटेशन को फिट करने की अनुमति देते थे। अतः 2005 तक, अर्धचालक विधियों ने दोहरी हाई-एंड डेस्कटॉप सीपीयू सीएमपी चिप्स को उच्च मात्रा में निर्मित करने की अनुमति दी है । कुछ डिज़ाइन, जैसे कि सन माइक्रोसिस्टम्स के अल्ट्रास्पार्क टी1, सिलिकॉन के टुकड़े पर अधिक प्रोसेसर फिट करने के लिए सरल (स्केलर, इन-ऑर्डर) डिज़ाइन में वापस आ गए हैं।

और विधियों जो वर्तमान समय में अधिक लोकप्रिय हो गई है वह है मल्टीथ्रेडिंग (कंप्यूटर आर्किटेक्चर) मल्टीथ्रेडिंग में, जब प्रोसेसर को धीमी सिस्टम मेमोरी से डेटा लाना होता है, तो डेटा आने के लिए रुकने के अतिरिक्त , प्रोसेसर दूसरे प्रोग्राम या प्रोग्राम थ्रेड पर स्विच हो जाता है जो निष्पादित करने के लिए तैयार होता है। चूंकि यह किसी विशेष प्रोग्राम/थ्रेड को गति नहीं देता है, किन्तु यह सीपीयू के निष्क्रिय रहने के समय को कम करके समग्र सिस्टम थ्रूपुट को बढ़ाता है।

इस प्रकार से वैचारिक रूप से, मल्टीथ्रेडिंग ऑपरेटिंग सिस्टम स्तर पर संदर्भ स्विच के समान है। अंतर यह है कि मल्टीथ्रेडेड सीपीयू सीपीयू चक्र में थ्रेड स्विच कर सकता है, न कि सैकड़ों या हजारों सीपीयू चक्रों के अतिरिक्त संदर्भ स्विच के लिए सामान्य रूप से आवश्यकता होती है। यह प्रत्येक सक्रिय थ्रेड के लिए राज्य हार्डवेयर (जैसे रजिस्टर फ़ाइल और प्रोग्राम गणक ) की प्रतिलिपि बनाकर प्राप्त किया जाता है।

अतः वृद्धि साथ मल्टीथ्रेडिंग है। यह विधियों सुपरस्केलर सीपीयू को ही चक्र में साथ विभिन्न प्रोग्राम/थ्रेड से निर्देशों को निष्पादित करने की अनुमति देती है।

यह भी देखें

- नियंत्रण यूनिट

- हार्डवेयर आर्किटेक्चर

- हार्डवेयर विवरण लैन्गवेग (एचडीएल)

- निर्देश-स्तरीय समानता (आईएलपी)

- एएमडी सीपीयू माइक्रोआर्किटेक्चर की सूची

- इंटेल सीपीयू माइक्रोआर्किटेक्चर की सूची

- प्रोसेसर डिज़ाइन

- स्ट्रीम प्रोसेसिंग

- वीएचडीएल

- अधिक उच्च मापों पर एकीकरण (वीएलएसआई)

- वेरिलोग

संदर्भ

- ↑ Curriculum Guidelines for Undergraduate Degree Programs in Computer Engineering (PDF). Association for Computing Machinery. 2004. p. 60. Archived from the original (PDF) on 2017-07-03.

Comments on Computer Architecture and Organization: Computer architecture is a key component of computer engineering and the practicing computer engineer should have a practical understanding of this topic...

- ↑ Murdocca, Miles; Heuring, Vincent (2007). Computer Architecture and Organization, An Integrated Approach. Wiley. p. 151. ISBN 9780471733881.

- ↑ Clements, Alan. Principles of Computer Hardware (4th ed.). pp. 1–2.

- ↑ Flynn, Michael J. (2007). "An Introduction to Architecture and Machines". कंप्यूटर वास्तुकला पाइपलाइन और समानांतर प्रोसेसर डिजाइन. Jones and Bartlett. pp. 1–3. ISBN 9780867202045.

- ↑ Jump up to: 5.0 5.1 Hennessy, John L.; Patterson, David A. (2006). Computer Architecture: A Quantitative Approach (4th ed.). Morgan Kaufmann. ISBN 0-12-370490-1.

- ↑ Wilkes, M. V. (1969). "The Growth of Interest in Microprogramming: A Literature Survey". ACM Computing Surveys. 1 (3): 139–145. doi:10.1145/356551.356553. S2CID 10673679.

अग्रिम पठन

- Patterson, D.; Hennessy, J. (2004). Computer Organization and Design: The Hardware/Software Interface. Morgan Kaufmann. ISBN 1-55860-604-1.

- Hamacher, V. C.; Vrasenic, Z. G.; Zaky, S. G. (2001). Computer Organization. McGraw-Hill. ISBN 0-07-232086-9.

- Stallings, William (2002). Computer Organization and Architecture. Prentice Hall. ISBN 0-13-035119-9.

- Hayes, J. P. (2002). Computer Architecture and Organization. McGraw-Hill. ISBN 0-07-286198-3.

- Schneider, Gary Michael (1985). The Principles of Computer Organization. Wiley. pp. 6–7. ISBN 0-471-88552-5.

- Mano, M. Morris (1992). Computer System Architecture. Prentice Hall. p. 3. ISBN 0-13-175563-3.

- Abd-El-Barr, Mostafa; El-Rewini, Hesham (2004). Fundamentals of Computer Organization and Architecture. Wiley. p. 1. ISBN 0-471-46741-3.

- Gardner, J (2001). "PC Processor Microarchitecture". ExtremeTech.

- Gilreath, William F.; Laplante, Phillip A. (2012) [2003]. Computer Architecture: A Minimalist Perspective. Springer. ISBN 978-1-4615-0237-1.

- Patterson, David A. (10 October 2018). A New Golden Age for Computer Architecture. US Berkeley ACM A.M. Turing Laureate Colloquium. ctwj53r07yI.