बहुसंकेतक

इलेक्ट्रानिक्स में, मल्टीप्लेक्सर (या मक्स; कभी-कभी मल्टीप्लेक्सर के रूप में लिखा जाता है), जिसे डेटा चयनकर्ता के रूप में भी जाना जाता है, यह ऐसा उपकरण है जो कई एनालॉग संकेत या डिजिटल इनपुट संकेत (इलेक्ट्रॉनिक्स) के बीच चयन करता है और चयनित इनपुट को एकल आउटपुट रेखा पर अग्रेषित करता है।[1] चयन को डिजिटल इनपुट के भिन्न सेट द्वारा निर्देशित किया जाता है जिसे चयनित लाइनों के रूप में जाना जाता है। इनपुट के एक मल्टीप्लेक्सर में चयन रेखायें होती हैं, जिनका उपयोग यह चुनने के लिए किया जाता है कि आउटपुट को कौन सी इनपुट रेखा भेजनी है।[2]

एक मल्टीप्लेक्सर कई इनपुट संकेतों के लिए एक उपकरण या संसाधन को साझा करना संभव बनाता है, उदाहरण के लिए, प्रति इनपुट संकेत में एक उपकरण होने के अतिरिक्त, एक एनालॉग-से-डिजिटल कनवर्टर या एक संचार ट्रांसमिशन माध्यम। मल्टीप्लेक्सर्स का उपयोग कई वेरिएबल्स के बूलियन बीजगणित को प्रायुक्त करने के लिए भी किया जा सकता है।

इसके विपरीत, एक डिमल्टीप्लेक्सर (या डिमक्स) एक उपकरण है जो एकल इनपुट लेता है और संगत मक्स के आउटपुट के संकेतों का चयन करता है, जो एकल इनपुट और एक साझा चयन रेखा से जुड़ा होता है। एक मल्टीप्लेक्सर का उपयोग अधिकांश प्राप्त सिरे पर एक पूरक डीमल्टीप्लेक्सर के साथ किया जाता है।।[1]

एक इलेक्ट्रॉनिक मल्टीप्लेक्सर को मल्टीपल-इनपुट, सिंगल-आउटपुट स्विच और डीमल्टीप्लेक्सर को सिंगल-इनपुट, मल्टीपल-आउटपुट स्विच के रूप में माना जा सकता है।[3] मल्टीप्लेक्सर के लिए योजनाबद्ध प्रतीक एक समद्विबाहु समलम्बाकार है जिसमें लंबे समानांतर पक्ष में इनपुट पिन और छोटे समानांतर पक्ष में आउटपुट पिन होता है।[4] दाईं ओर का योजनाबद्ध बाईं ओर 2-से-1 मल्टीप्लेक्सर और दाईं ओर एक समतुल्य स्विच दिखाता है। वायर वांछित इनपुट को आउटपुट से जोड़ता है।

अनुप्रयोग

मल्टीप्लेक्सर्स एक विशिष्ट स्रोत से डेटा का चयन करने के लिए कंप्यूटर सिस्टम का भाग हैं, तथापि वह मेमोरी चिप हो या हार्डवेयर पेरिफेरल हो। एक कंप्यूटर डेटा को नियंत्रित करने और बसों को संबोधित करने के लिए मल्टीप्लेक्सर्स का उपयोग करता है, जिससे प्रोसेसर को कई डेटा स्रोतों से डेटा का चयन करने की अनुमति मिलती है

डिजिटल संचार में, मल्टीप्लेक्सर के एकल आउटपुट को डीमल्टीप्लेक्सर के एकल इनपुट (टाइम-डिवीजन मल्टीप्लेक्सिंग) से जोड़कर, एक ही चैनल पर कई कनेक्शन की अनुमति देते हैं। दाईं ओर की छवि इस लाभ को दर्शाती है। इस स्थितियों में, प्रत्येक डेटा स्रोत के लिए भिन्न-भिन्न चैनल प्रायुक्त करने की लागत मल्टीप्लेक्सिंग/डीमल्टीप्लेक्सिंग फ़ंक्शन प्रदान करने की लागत और असुविधा से अधिक है।

डेटा लिंक के प्राप्त अंत में एकल डेटा स्ट्रीम को मूल स्ट्रीम में वापस तोड़ने के लिए सामान्यतः एक पूरक डीमल्टीप्लेक्सर की आवश्यकता होती है। कुछ मामलों में, सुदूर अंत प्रणाली की कार्यक्षमता एक साधारण डीमल्टीप्लेक्सर से अधिक हो सकती है; और जबकि डीमल्टीप्लेक्सिंग अभी भी तकनीकी रूप से होती है, इसे कभी भी विवेकपूर्वक प्रयुक्त नहीं किया जा सकता है। उदाहरण के लिए, यह तब होगा जब एक मल्टीप्लेक्सर कई इंटरनेट प्रोटोकॉल नेटवर्क उपयोगकर्ताओं को सेवा प्रदान करेगा; और फिर सीधे राउटर (कंप्यूटिंग) में फ़ीड करता है, जो तुरंत पूरे लिंक की सामग्री को अपने रूटिंग प्रोसेसर में पढ़ता है; और फिर मेमोरी में डीमल्टीप्लेक्सिंग करता है जहां से इसे सीधे आईपी अनुभागों में परिवर्तित किया जाएगा।

अधिकांश, एक मल्टीप्लेक्सर और डीमल्टीप्लेक्सर को उपकरण के एक टुकड़े में जोड़ दिया जाता है, जिसे केवल मल्टीप्लेक्सर के रूप में जाना जाता है। ट्रांसमिशन लिंक के दोनों सिरों पर दोनों परिपथ अवयवों की आवश्यकता होती है क्योंकि अधिकांश संचार प्रणालियां डुप्लेक्स (दूरसंचार) में संचारित होती हैं।

एनालॉग परिपथ डिज़ाइन में, मल्टीप्लेक्स विशेष प्रकार का एनालॉग स्विच होता है जो कई इनपुट से चुने गए संकेत को आउटपुट से जोड़ता है।

डिजिटल मल्टीप्लेक्सर्स

डिजिटल परिपथ डिजाइन में, चयनकर्ता तार डिजिटल मान के होते हैं। 2-से-1 मल्टीप्लेक्सर के स्थितियों में, 0 का लॉजिक मान को आउटपुट से जोड़ेगा जबकि 1 का लॉजिक मान को आउटपुट से जोड़ेगा।

बड़े मल्टीप्लेक्सर्स में, चयनकर्ता पिनों की संख्या के बराबर होती है जहां इनपुट की संख्या है।

उदाहरण के लिए, 9 से 16 इनपुट के लिए 4 चयनकर्ता पिन से कम की आवश्यकता नहीं होगी और 17 से 32 इनपुट के लिए 5 चयनकर्ता पिन से कम की आवश्यकता नहीं होगी। इन चयनकर्ता पिनों पर व्यक्त बाइनरी मान चयनित इनपुट पिन को निर्धारित करता है।

2-से-1 मल्टीप्लेक्सर में एक बूलियन समीकरण होता है जहां और दो इनपुट हैं, चयनकर्ता इनपुट होता है, और आउटपुट होता है:

जिसे वास्तविक तालिका के रूप में व्यक्त किया जा सकता है:

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

या, सरल अंकन में:

| 0 | A |

| 1 | B |

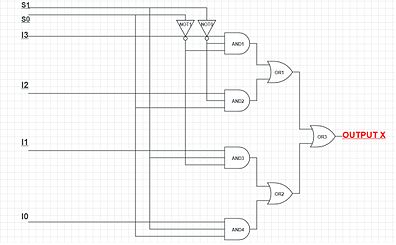

ये तालिकाएँ दर्शाती हैं कि जब तब किन्तु जब तब होता है। इस 2-से-1 मल्टीप्लेक्सर की सीधी प्राप्ति के लिए 2 AND द्वार, OR द्वार और NOT द्वार की आवश्यकता होगी। चूंकि यह गणितीय रूप से सही है, प्रत्यक्ष भौतिक कार्यान्वयन दौड़ की स्थिति उत्पन्न हो सकती है, जिसे दबाने के लिए अतिरिक्त फाटकों की आवश्यकता होती है।[5]

बड़े मल्टीप्लेक्सर्स भी सामान्य हैं और, जैसा कि ऊपर बताया गया है, इनपुट के लिए न चयनकर्ता पिन की आवश्यकता होती है। अन्य सामान्य आकार 4-से-1, 8-से-1 और 16-से-1 हैं। चूंकि डिजिटल लॉजिक बाइनरी मानों का उपयोग करता है, इसलिए चयनकर्ता इनपुट की दी गई संख्या के लिए कई इनपुट को अधिकतम रूप से नियंत्रित करने के लिए 2 की शक्तियों (4, 8, 16) का उपयोग किया जाता है।

4-से-1 मल्टीप्लेक्सर के लिए बूलियन समीकरण है:

निम्नलिखित 4-से-1 मल्टीप्लेक्सर 3-स्टेट बफर और AND (AND गेट्स डिकोडर के रूप में कार्य कर रहे हैं) गेट्स से निर्मित होता है:

सबस्क्रिप्ट पर इनपुट बाइनरी नियंत्रण इनपुट के दशमलव मान को निरुपित करते हैं जिस पर उस इनपुट को जाने दिया जाता है।

चेनिंग मल्टीप्लेक्सर्स

छोटे मल्टीप्लेक्सर्स को साथ जोड़कर बड़े मल्टीप्लेक्सर्स का निर्माण किया जा सकता है। उदाहरण के लिए, 8-से-1 मल्टीप्लेक्सर को दो 4-से-1 और 2-से-1 मल्टीप्लेक्सर के साथ बनाया जा सकता है। दो 4-से-1 मल्टीप्लेक्सर आउटपुट को 2-से-1 में सेलेक्टर पिन के साथ 4-से-1 के समानांतर रखा जाता है, जिससे चयनकर्ता इनपुट की कुल संख्या 3 हो जाती है, जो 8-से-1 के समान है।

आईसी की सूची जो बहुसंकेतन प्रदान करती है

निम्न तालिका में 7400 श्रृंखला भाग संख्याओं के लिए, x लॉजिक वर्ग है।

| आईसी नं. | फंक्शन | आउटपुट स्टेट |

|---|---|---|

| 74x157 | क्वाड 2:1 मक्स. | दिए गए इनपुट के समान आउटपुट |

| 74x158 | क्वाड 2:1 मक्स. | आउटपुट व्युत्क्रम इनपुट है |

| 74x153 | ड्यूल 4:1 मक्स. | आउटपुट इनपुट के समान ही है |

| 74x352 | ड्यूल 4:1 मक्स. | आउटपुट व्युत्क्रम इनपुट है |

| 74x151A | 8:1 मक्स. | दोनों आउटपुट उपलब्ध हैं (अर्थात्, पूरक आउटपुट) |

| 74x151 | 8:1 मक्स. | आउटपुट व्युत्क्रम इनपुट है |

| 74x150 | 16:1 मक्स. | आउटपुट व्युत्क्रम इनपुट है |

डिजिटल डिमल्टीप्लेक्सर्स

डीएमएलटी कॉम्प्लेक्सर्स एक डेटा कैप्चर और कई सेलेक्शन चैलेंजर्स हैं, और उनके पास कई चैलेंजर्स उपस्थित हैं।

वे किसी भी एक विचारधारा को अग्रेसित करते हैं। डिमल्टी कॉम्प्लेक्सर का डिज़ाइन हमेशा-हमेशा के लिए सत्य हो जाता है, इसलिए डिमल्टी कॉम्प्लेक्सर बाइनरी डिकोडर के रूप में काम करता है।

इसका अर्थ यह है कि किसी भी फिल्म के निर्माण के लिए बिट्स का चयन करें, जैसे कि चित्र के सही सेट को OR-ING करके बनाया जा सकता है।

यदि X इनपुट है और S चयनकर्ता है, और A और B आउटपुट हैं:

डीमल्टीप्लेक्सिंग प्रदान करने वाले आईसी की सूची

निम्न तालिका में 7400 श्रृंखला भाग संख्याओं के लिए, x लॉजिक वर्ग है।

| IC No. (7400) | IC No. (4000) | Function | Output State |

|---|---|---|---|

| 74x139 | ड्यूल 1:4 डिमक्स | आउटपुट व्युत्क्रम इनपुट है | |

| 74x156 | ड्यूल 1:4 डिमक्स | आउटपुट खुला कलेक्टर है | |

| 74x138 | 1:8 डिमक्स. | आउटपुट व्युत्क्रम इनपुट है | |

| 74x238 | 1:8 डिमक्स. | ||

| 74x154 | 1:16 डिमक्स. | आउटपुट व्युत्क्रम इनपुट है | |

| 74x159 | CD4514/15 | 1:16 डिमक्स. | आउटपुट खुला कलेक्टर है और इनपुट के समान है |

मल्टीप्लेक्सर्स पीएलडी के रूप में

बूलियन फ़ंक्शंस को प्रयुक्त करने के लिए मल्टीप्लेक्सर्स को प्रोग्रामेबल लॉजिक उपकरण के रूप में भी उपयोग किया जा सकता है। n वेरिएबल्स और एक परिणाम के किसी भी बूलियन फ़ंक्शन को n चयनकर्ता इनपुट वाले मल्टीप्लेक्सर के साथ कार्यान्वित किया जा सकता है। वेरिएबल चयनकर्ता इनपुट से जुड़े होते हैं, और चयनकर्ता इनपुट के प्रत्येक संभावित संयोजन के लिए फ़ंक्शन परिणाम, 0 या 1, संबंधित डेटा इनपुट से जुड़ा होता है। यदि वेरिएबल (उदाहरण के लिए, D) भी व्युत्क्रम उपलब्ध है, तो n-1 चयनकर्ता इनपुट वाला मल्टीप्लेक्सर पर्याप्त है; चयनकर्ता इनपुट के प्रत्येक संयोजन के लिए वांछित आउटपुट के अनुसार डेटा इनपुट 0, 1, D, या ~D से जुड़े हैं।[6]

यह भी देखें

- डिजिटल सब्सक्राइबर लाइन एक्सेस मल्टीप्लेक्सर (डीएसएलएएम)

- व्युत्क्रम मल्टीप्लेक्सर

- मल्टीप्लेक्सिंग

- सीडीएमए (कोड-डिवीजन मल्टीप्लेक्सिंग)

- फ्रीक्वेंसी-डिवीजन मल्टीप्लेक्सिंग

- समय विभाजन बहुसंकेतन

- वेवलेंथ समय विभाजन बहुसंकेतन

- सांख्यिकीय बहुसंकेतन

- चार्लीप्लेक्सिंग

- प्राथमिकता एनकोडर

- नियम 184 , एक सेलुलर ऑटोमेटन जिसमें प्रत्येक सेल दो आसन्न कोशिकाओं के मानों के लिए मल्टीप्लेक्सर के रूप में कार्य करती है

- सांख्यिकीय मल्टीप्लेक्सर

संदर्भ

- ↑ 1.0 1.1 Dean, Tamara (2010). नेटवर्क + नेटवर्क के लिए गाइड. Delmar. pp. 82–85. ISBN 978-1423902454.

- ↑ Debashis, De (2010). बेसिक इलेक्ट्रॉनिक्स. Dorling Kindersley. p. 557. ISBN 9788131710685.

- ↑ Lipták, Béla (2002). इंस्ट्रूमेंट इंजीनियर्स हैंडबुक: प्रोसेस सॉफ्टवेयर और डिजिटल नेटवर्क. CRC Press. p. 343. ISBN 9781439863442.

- ↑ Harris, David (2007). डिजिटल डिजाइन और कंप्यूटर आर्किटेक्चर. Penrose. p. 79. ISBN 9780080547060.

- ↑ Crowe, John; Hayes-Gill, Barrie (1998). "The multiplexer hazard". डिजिटल इलेक्ट्रॉनिक्स का परिचय. Elsevier. pp. 111–3. ISBN 9780080534992.

- ↑ Lancaster, Donald E. (1974). टीटीएल कुकबुक. H.W. Sams. pp. 140–3. ISBN 9780672210358.

आगे की पढाई

- Mano, M. Morris; Kime, Charles R. (2008). Logic and Computer Design Fundamentals (4th ed.). Prentice Hall. ISBN 978-0-13-198926-9.

इस पेज में लापता आंतरिक लिंक की सूची

- समद्विबाहु ट्रेपेज़ॉइड

- सच्ची तालिका

- वेवलेंथ डिविज़न मल्टिप्लेक्सिंग

बाहरी कड़ियाँ

The dictionary definition of multiplexer at Wiktionary

The dictionary definition of multiplexer at Wiktionary